Toshiba Develops Ultra-low-power Analog AI Accelerator Chip for Embedded Systems

Toshiba Corporation

Overview

Toshiba has developed an ultra-low-power analog AI accelerator chip for embedded systems. This technology realizes multiply-accumulate operation—which accounts for the majority of neural network operations—using only one-eighth the power of current digital circuits. This chip will accelerate the introduction of AI technologies into embedded devices that operate on battery power, energy harvesting, or remote wireless power, which has been difficult until now.

Development Background

AI technology has attracted attention not only for image processing, but also for use in fields such as industrial machinery, medicine and healthcare, mobile consumer devices, and Internet of Things devices. In conventional cloud-based AI, high-speed wired and wireless communications are required between sensors and a cloud-based neural network that analyzes the large amounts of sensor data from embedded devices. This has created a barrier to the introduction of AI. Other problems associated with introducing AI into embedded devices include high hardware costs and power consumption.

Features of the Technology

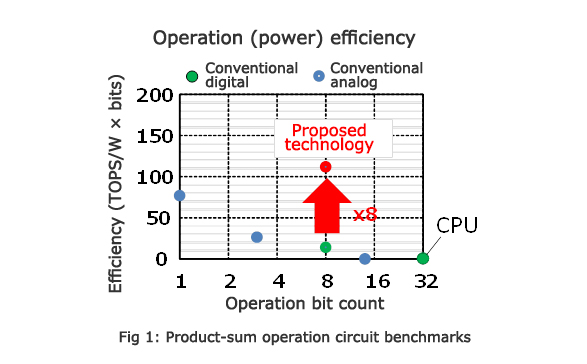

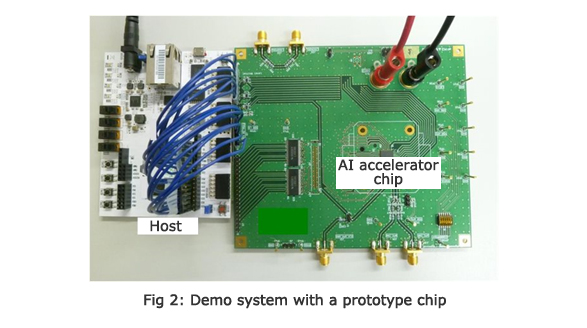

Toshiba has responded by developing an AI accelerator chip that performs multiply-accumulate operation with low power consumption, using a novel phase-domain analog circuit technology. Oscillation circuits are not normally used for arithmetic operations, but Toshiba's technology uses the phase domain of an oscillation circuit for multiply-accumulate operation by dynamically controlling oscillation time and frequency. This technology makes it possible to collectively process multiplication, addition, and memory operations that are conventionally processed by individual digital circuits, thereby reducing power consumption to one-eighth that of digital circuits with the same area (Fig. 1). Toshiba has successfully demonstrated application of the AI accelerator chip to inference processing in a neural network for image recognition and anomaly detection (Fig. 2).

Future Development

Toshiba will continue to develop practical applications of AI accelerator technology and will continue to contribute to the expansion of use cases for embedded devices and infrastructure solutions.