Corporate Research & Development Center

Development of a 10 nm-diameter nanowire transistor for ultra-low power consumption LSIs

Overview

A nanowire transistor is one of the most desired structures for the development of ultra-low power consumption LSIs. Toshiba has developed a 10 nm-diameter tri-gate nanowire transistor that saves the power during standby mode by a factor of ten by controlling the voltage applied to the substrate . This technique was presented at the 2012 Symposia on VLSI Technology & Circuits, an international conference on semiconductor devices held in the US in June 2012.

Development background

To be able to create an ultra-low power consumption LSI, manufacturers have been working on the development of a nanowire transistor, whose channel consists of nanometer-scale wire-shaped silicon. With the gate surrounding the thin-wire channel, this transistor offers improved gate control and a significant reduction in leak current caused by the short-channel effect when power is not being applied. On the other hand, the gate all-around structure of the transistor, in which the gate is placed under the nanowire channel and surrounds the entire channel, makes it difficult to reduce power consumption because the voltage cannot be applied to the substrate. This transistor design has thus hindered the manufacture of ultra-low power consumption LSIs.

Features of the technology

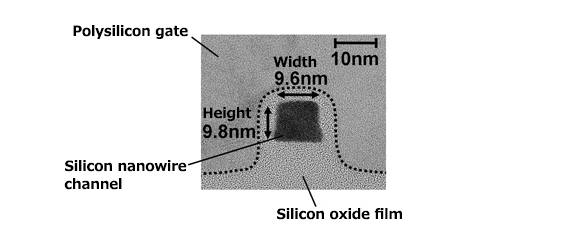

Toshiba has succeeded, for the first time in the world, in operating a tri-gate nanowire transistor, with the wire diameter downsized to 10 nm and the nanowire oxide film layer made as thin as 20 nm. We have applied a voltage of –1 V to the transistor substrate and verified that the off-state current (power consumption) during standby is reduced tenfold. We have also confirmed that application of a voltage of –1 V to the SRAM substrate (volatile memory) consisting of a tri-gate nanowire transistor will improve operational stability by 26% and reduce the power-supply voltage during standby by 21%.

Outlook

Based on this technology, we are continuing to study more sophisticated and lower-power-consuming LSIs. This technology is being created as a part of NEDO's Development of Nanoelectronic Device Technology.