News Releases

Toshiba Develops Many-Core SoC for Embedded Applications

New Chip integrates 64 Cores, Eight Times More Than the Previous SoCTOKYO—Toshiba Corporation (TOKYO: 6502) today announced the development of an innovative low-power, many-core System-on-a-Chip (SoC) for embedded applications in such areas as automotive products and digital consumer products. The prototype SoC integrates 64 cores, eight times more than its multi-core predecessor[1] and operates 14 times faster.

Details of the SoC and its development will be presented at the 2012 IEEE Symposia on VLSI Technology and Circuits in Honolulu, Hawaii on June 15[2].

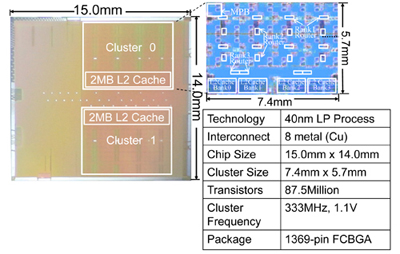

Recent advances in multimedia processing, including video encoding and decoding and image recognition, have relied on multi-core processors that combine high performance with low power consumption. Many-core processors go a step further; by increasing the number of cores they boost SoC performance to much higher levels. However, the power consumption and size of many-core SoC have been problems for their use in embedded applications. Toshiba's many-core SoC secures significant advances in performance while maintaining low power consumption and a cluster size of 84 mm2 , suitable for embedded applications.

Toshiba's new many-core SoC integrates 64 processor cores, eight times more than the company's multi-core SoC chip, achieved by using tree-based network-on-chip (NoC) architecture[3] and highly efficient embedded processor cores. Integrated with image recognition hardware accelerators, the new many-core SoC secures 1.5 tera operations per second at 333MHz, a processing rate 14 times faster than that of its eight-processor multi-core predecessor.

The new SoC applies low power technologies throughout its structure, including multi-level power gating, clock gating and Toshiba's proprietary low power data-mapping flip-flop circuit[4]. Advancing the fabrication process to 40nm secures a 40 to 50% boost in power efficiency over the company's previous multi-core chip, manufactured with 65nm process.

Toshiba plans to apply the many-core SoC and its related technologies to high performance over-HD (high definition) resolution image processing and recognition.

-

Notes:

- [1]

- The multi-core SoC that Toshiba announced at ISSCC 2008

- [2]

- Number: 18.1, title: "A Low Power Many-Core SoC with Two 32-Core Clusters Connected by Tree Based NoC for Multimedia Applications"

- [3]

- Network-on-chip technology transfers data as packets in an SoC.

- [4]

- A flip-flop circuit stores state information: "0" and "1".

Chip Micrograph and Features