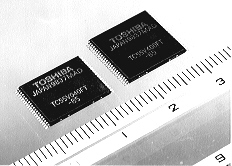

| Toshiba's New SRAM is Small, has Low Power Consumption Employs Full CMOS Technology 13 October, 1998

Tokyo--Toshiba Corporation today announced new static random access memories (SRAM) that combine significant chip shrinkage with a low standby current and a wide range of operating voltages. Fabricated with 0.35-micron millimeter, full complementary metal-oxide semiconductor (CMOS) process technology, the new SRAM are available in 2- and 4-megabit versions and are positioned to meet growing demand from the mobile equipment market. Toshiba will make its first samples available in October 1998. SRAM support enhanced system operation by temporarily holding data for the CPU while it executes other tasks. Toshiba's new chips offers small, powerful SRAM packages with low standby currency, characteristics that are a must for enhanced performance and functionality in hand-held and portable products. The new devices are primarily targeted at such products as cellular phones, pagers and personal digital assistants, where smaller, more versatile SRAM will support further design innovation and better performance. The operating characteristics of the SRAM will also support wider use, in such applications as point-of-sales equipment. Optimum Design for Stacked MCP The new specifications and pin assignment were agreed by Toshiba and NEC and have been endorsed by several other semiconductor companies. Specification of SRAM

|

||||||||||||||||||||||||

| Information in the press releases, including product prices and specifications, content of services and contact information, is current on the date of the press announcement,but is subject to change without prior notice. |