情報通信プラットフォーム

組込み向け超低消費電力アナログAIアクセラレータチップの開発

2018年02月09日

概要

当社は、組込み機器向けの超低消費電力アナログAIアクセラレータチップを開発しました。本技術によりニューラルネットワーク演算の大部分を占める積和演算処理を従来のデジタル回路と比べて1/8の消費電力で実現しました。また、本技術を適用することで、これまで困難であったエナジーハーベスト(環境発電)や遠隔無線給電で動作する組込み機器へのAI搭載が可能となり、機器の異常検知や寿命予測などへの応用が期待できます。

開発の背景

AI技術の活用は、画像処理だけでなく、製造、物流、医療、金融、インフラ向けなど様々な事業分野への拡大が注目されています。従来のクラウドベースAIでは、組込み機器に設置した大量のセンサデータをクラウド上のニューラルネットワークで解析するためにセンサとクラウドの間で膨大な量の通信が必要となり、AI導入の障壁となることが懸念されています。また、一方で、組み込み機器でのAI導入には、ハードウェアのコストや消費電力の高さという課題がありました。

本技術の特徴

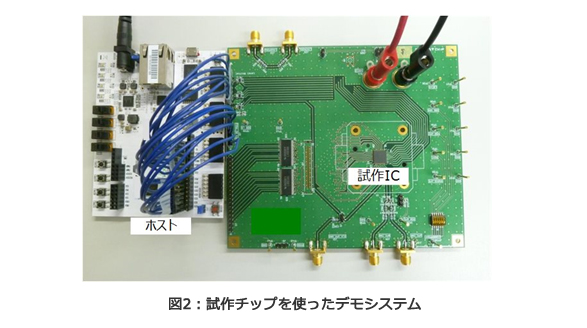

そこで当社は、演算回路に独自の発振回路を採用し、その発振時間と発振周波数を動的に制御することで演算を行う新たな演算処理技術を開発しました。本技術により、従来は個別のデジタル回路で処理されていた乗算、加算、記憶を1つの回路で処理可能となり、演算処理の際に動作するトランジスタの数が削減することにより消費電力の大幅な削減を実現します。また、今回開発した演算処理技術を搭載したAIアクセラレータチップを試作し、従来のデジタル回路と比べて同程度の面積で消費電力が1/8となることを確認しました(図1)。更に、開発したAIアクセラレータチップを用いて画像認識や故障検知のニューラルネットワークの推論処理のデモ動作にも成功しました(図2)。

今後の展望

当社は今後も、AIアクセラレータ技術の実用化に向けて開発を進め、組み込み機器やインフラソリューションなどの活用場面の拡大に貢献していきます。