LSI・ストレージ

ナノサイズの薄膜多結晶シリコントランジスタの性能と結晶性の関係を直接評価できる2次元結晶性評価技術を開発

2017年4月

概要

当社は、ナノサイズの薄膜多結晶シリコン(注1)トランジスタにおいて電子の伝導を担うチャネル(電流経路)部の性能と結晶性(注2)の関係を可視化する評価技術を開発しました。本技術により、従来関係性を調べることが困難だった電子デバイス中の多結晶シリコントランジスタの電気特性と結晶性との関係を直接評価し、電気特性の劣化要因を特定することが可能になりました。本技術の詳細は、米国モントレーで開催された国際信頼性物理シンポジウム(IRPS2017)にて、4月6日(現地時間)に発表しました。

開発の背景

IoTの普及により、さまざまなセンサーや通信デバイスなど、小型で高性能な電子デバイスが求められており、高性能で高密度な回路を持つ3次元構造の電子デバイスの開発が進められています。3次元構造の電子デバイスにおけるトランジスタには、従来の単結晶シリコンではなく、積層可能な薄膜多結晶シリコンが用いられます。一方、多結晶シリコンは結晶性が不均一であることが要因となり、電気性能(トランジスタの電流駆動力)が劣化してしまうことが懸念されています。薄膜多結晶シリコントランジスタの高性能化には、特にチャネル部分の結晶性が重要と考えられており、3次元構造でナノサイズの微細な素子において、多結晶シリコンの結晶性を評価する手法の確立が求められていました。

本技術の特徴

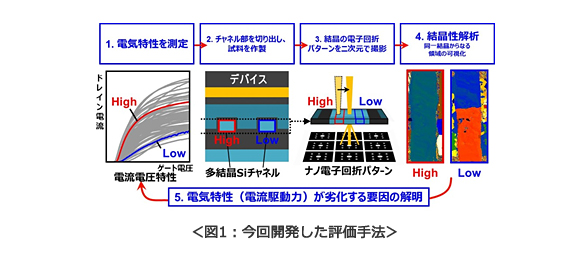

そこで当社は、トランジスタのチャネル部における多結晶シリコンの結晶性を解析する手法を開発しました。まず、多結晶シリコントランジスタのチャネル部分を切り出し、解析するための試料を作製します。作製した試料に、数ナノメートル以下の分解能を備えた電子顕微鏡を用いて結晶の電子回折パターン(注3)を二次元撮影し、多結晶シリコンの同一結晶からなる領域を可視化することに成功しました。

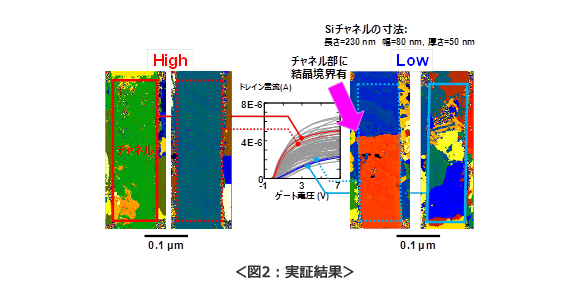

本技術により、世界で初めて(注4)微細な電子デバイス中の個々の多結晶シリコントランジスタのチャネル部の性能と結晶性の関係を直接評価することが可能となりました。また、本評価手法により、個々の多結晶トランジスタの性能が、結晶粒の平均的な大きさだけでなく、トランジスタのチャネル部を横断する結晶粒界注5の有無にも大きく依存することを明らかにしました。

今後の展望

当社は、今回開発した評価技術を3次元構造の多結晶シリコントランジスタの信頼性向上に活用していきます。また、ピンポイントに不良部の位置を特定できるという本技術の特長を応用し、多結晶材料を含む各種デバイスなど広い分野への展開を目指します。

(注1)多結晶シリコン:多数の微小な単結晶で構成されたシリコン結晶のこと。微小な単結晶間に結晶粒界と呼ばれる界面が存在する。

(注2)結晶性:結晶内の欠陥や結晶粒の大きさ、結晶粒の分布の様子のこと。

(注3)電子回折パターン:試料に電子をあてて得られる干渉パターンのこと。

(注4)当社調べ。

(注5)結晶粒界:結晶どうしの境界面のこと。