LSI・ストレージ

平成28年12月5日

内閣府政策統括官(科学技術・イノベーション担当)

Tel:03-6257-1339

株式会社 東芝

Tel:03-3457-2100(広報・IR部)

科学技術振興機構(JST)

Tel:03-5214-8404(広報課)

電圧制御磁化反転を使った不揮発性磁気メモリに新たな書込み方式を提案

ポイント

- データの書込みに2つの新規なスピントロニクスの物理原理(VCMA効果とスピンホール効果)を利用した電圧書込み方式の不揮発性磁気メモリの新たなアーキテクチャ技術(VoCSM: Voltage-Control Spintronics Memory)を開発

- 磁化反転の電圧制御を巧みに利用した独自の書込みシーケンスによる複数ビットの一括書込みを実証

- 書込みに必要な消費電力の一桁低減に目処

内閣府 総合科学技術・イノベーション会議が主導する革新的研究開発推進プログラム(ImPACT)の佐橋政司プログラム・マネージャーの研究開発プログラムの一環として、株式会社東芝 研究開発センターの與田博明技監らの研究開発チームは、電圧書込み方式の不揮発性磁気メモリの新たなアーキテクチャ技術を開発しました。

電圧制御磁化反転を使った、電圧書込み方式の不揮発性磁気メモリの実現に向けて、課題であった所要の書込み確率の確保を可能とする新たなアーキテクチャ技術の開発に成功しました。本研究開発チームは、データの書込みに2つのスピントロニクスの物理原理(VCMA効果とスピンホール効果)を利用した電圧書込み方式の不揮発性磁気メモリの新しいアーキテクチャの独自技術(VoCSM: Voltage-Control Spintronics Memory)を開発し、併せて独自の書込みシーケンス(Voltage-Control Flash 書込み:VoCF 書込み)による複数ビットの一括書込みを実証しました。これにより所要の書込みの確率を確保したうえで、書込み時の消費電力を一桁低減できる可能性を示しました。

この結果、究極の省電力・大容量メモリである電圧書込み不揮発性磁気メモリと超低消費電力情報機器の実現可能性が検証されました。

今後、産業技術総合研究所、物質・材料研究機構、東北大学、大阪大学と連携し、実用化に向けての最大課題である電圧書込み効率の向上に取り組んで参ります。

この成果の詳細は、2016年12月7日に、米国サンフランシスコにて開催される半導体国際会議International Electron Devices Meeting(IEDM:会期12月3日~7日)にて技術発表されます。また、本研究成果は2016年12月3日13時30分(米国太平洋標準時間(PST))発行予定の「IEDM 2016 Technical Digest」に掲載されます。

本成果は、以下の事業・研究プロジェクトによって得られました。

内閣府革新的研究開発推進プログラム(ImPACT)https://www.jst.go.jp/impact/

- プログラム・マネージャー:

- 佐橋 政司

- 研究開発プログラム:

- 「無充電で長期間使用できる究極のエコIT機器の実現」

- 研究開発課題:

- 「電圧駆動MRAMのプロセス技術およびメモリアレイの開発」

- 研究開発責任者:

- 與田 博明(株式会社 東芝 研究開発センター 技監)

- 研究期間:

- 平成26年度~平成30年度

上記研究開発課題では、電圧駆動MRAMの実現に重要な要素技術として、メモリアーキテクチャ、メモリデバイス、メモリ素子およびその微細加工技術の開発に取り組んでいます。

■ImPACTプログラム・マネージャーのコメント■

研究の背景と経緯

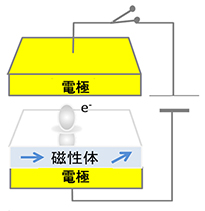

IoT(注1)やCPS(注2)など、ネットワーク情報通信機器の新たな展開が進むなか、コンピュータやメモリの新たなヒエラルキーの構築と情報(IT)機器の省電力化、いわゆるエコ(グリーン)ITの実現は、喫緊かつ最重要課題として取り組まなければならない社会的課題の1つです。その1つのアプローチに不揮発性エレクトロニクスデバイスの開発があります。スピントロニクス(注3)分野では、磁石の磁化が持つ不揮発性記憶機能を利用したMTJ記憶素子(Magnetic Tunnel Junction)(注4)を用い、待機電力ゼロの不揮発性磁気メモリMRAM(注5)の開発が精力的に行われています。現在、世界規模で製品開発が進められている電流駆動書込み方式のMRAM(STT-MRAM)(注6)は低消費電力の不揮発性磁気メモリとして期待されています。しかし、この方式のMRAMは、電流駆動のため書込み電流を流す必要があり、ジュール発熱などによる電力消費で、動作時の消費電力の低減には限界がありました。

一方、数ナノ秒の電圧パルスによる磁化反転の制御を使う電圧駆動MRAMは、1)原理的に電流が不要で超低消費電力駆動、2)数ナノ秒の高速動作、3)高い耐久性、4)室温での動作可能、などの特長があります。これまで、電圧書込み方式の磁気メモリである「電圧駆動MRAM」は、基礎研究の段階にありましたが、電流駆動であるSTT-MRAMに比べて、一層の低消費電力化が可能となり、究極の超低消費電力不揮発メモリが実現出来ること、CMOS(注7)用のトランジスタと同様、電圧駆動となるためトランジスタサイズを小面積にすることができ、高集積・高密度化のポテンシャルを持っていることから、実現のあかつきには大きな社会的インパクトが期待されます。

これまで、ImPACT佐橋プログラムでは、産総研(産業技術総合研究所)が中核拠点となり、電圧駆動MRAM開発タスクフォースプロジェクト(プロジェクトリーダ:湯浅新治 産総研スピントロニクス研究センター長)で、株式会社 東芝、物材機構(物質・材料研究機構)、東北大学 AIMR(原子分子材料科学高等研究機構)、大阪大学 大学院基礎工学研究科、JASRI(高輝度光科学研究センター)の参加のもと、厚さが数原子層程度の金属磁石薄膜に電圧をかけて、磁化の向きやすい方向(磁気異方性)を制御する技術の開発を中心に、界面電圧効果の物理解明、電圧駆動MRAMの評価技術の開発および材料開発に取り組んで来ました(2015年12月10日産総研プレス発表、2016年7月26日東北大AIMRプレス発表など)。

磁気異方性の電圧制御による電圧駆動MRAMの実用化には、書込みエラー率を10-10~10-15以下にする必要があります。しかし、これまでは電圧パルス書込み方式の書込みエラー率を評価し、メモリとして安定動作が可能であることは立証されている(産総研プレス発表2015年12月10日など)ものの、 書込みエラー率を低減するメモリアーキテクチャからの提案はされていませんでした。

今回、ImPACT佐橋プログラムの参加研究開発機関である株式会社 東芝 研究開発センターの與田博明技監を研究開発責任者(Principal Investigator: PI)とする東芝チームが、データの書込みに2つの新規なスピントロニクスの物理原理(VCMA(注8))とスピンホール効果(注9)を利用した電圧書込み方式の不揮発性磁気メモリの新たなアーキテクチャ技術(VoCSM: Voltage-Control Spintronics Memory)を開発しました。この開発により、書込み確率の大幅な向上が実証され、消費電力を一桁低減できる可能性を示しました。

なお、本研究開発は、内閣府「革新的研究開発推進プログラム(ImPACT)」の研究開発プログラム「無充電で長期間使用できる究極のエコIT機器の実現」(プログラム・マネージャー:佐橋 政司)の一環として行われたものです。

研究の内容

本研究開発のきもとなるデータの書込み技術には、開発した2つのスピントロニクスの物理原理(VCMA効果とスピンホール効果)を利用した電圧書込み方式の不揮発性磁気メモリの新たなアーキテクチャ(VoCSM: Voltage-Control Spintronics Memory)を用いました。

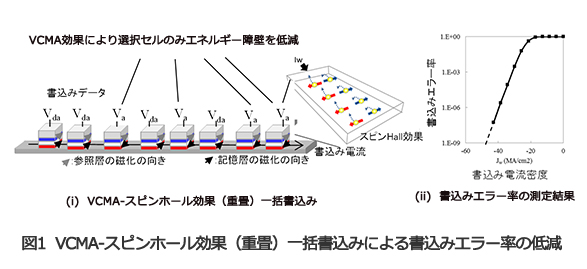

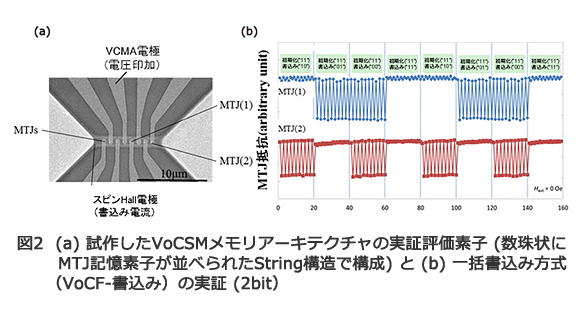

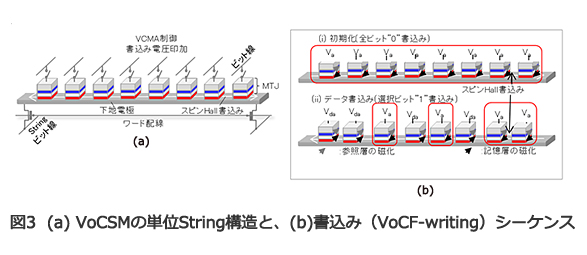

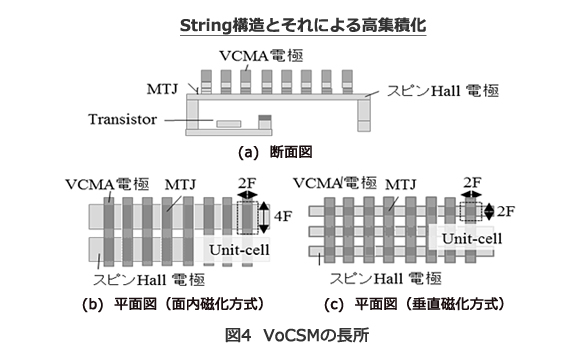

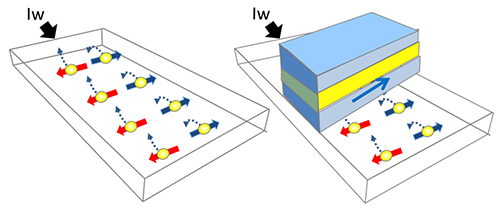

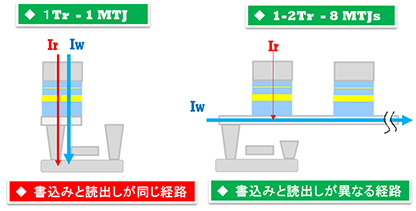

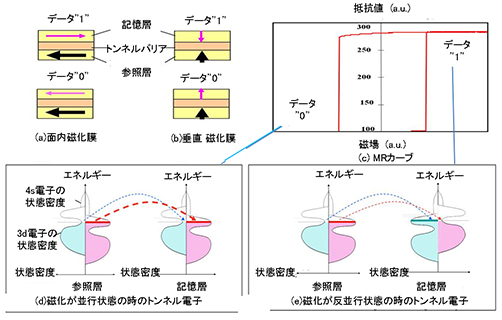

VCMA効果にスピンホール効果を重畳させる書込み方式を用いることで、書込みエラー率を大幅に低減できる可能性を初めて示しました(図1)。また、今回あみだした独自の書込みシーケンス(Voltage-Control Flash 書込み: VoCF 書込み)を用いた実装評価素子により、複数ビットを一括で書込めることも実証しました(図2、図3)。これにより書込みの際(動作時)に消費する電力を一桁低減できる可能性を示しました。なお、本発表の新たなメモリアーキテクチャは、実質三端子構造をとりますが、その欠点であるフットプリントの増大に対しては、複数のMTJ記憶素子を1つのストリング(糸紐)上に配置する数珠つなぎ構造(String構造)とすることで、この欠点を回避しました。

加えて、VoCSMアーキテクチャとVoCF書込みシーケンスは、将来的には以下のような理由で、大容量化のポテンシャルを持つ技術として期待できます。

電流駆動のSTT-MRAMでは、2端子構造ゆえに書込み時と読出し時の電流経路が同じであるため、いずれの際にもトンネル障壁に電流が流れ、読出し時に誤って書込みを行なってしまう誤書込み(Read Disturbance(注10))が発生する可能性があります。したがって、読出し時には誤書込みを起こさないように留意し、また書込み時にはトンネル障壁の寿命に留意した設計が必要です。それに対してVoCSMアーキテクチャでは、印加する読出し電圧の極性を選択することで、原理上読出し時の誤書込み(Read Disturbance)を無くすことができます。また、トンネル障壁に書込み電流を流す必要がないため、トンネル障壁の寿命に留意した設計をする必要がなくなります(原理上無限大の書き換え耐性を有します)。また、CMOS同様電圧駆動となるため、メモリセル選択用のトランジスタサイズを小面積にすることが可能になります(図4)。

これらの特長を最大限に活かしたうえで、VCMA効果さえ大きくすることができれば、STT-MRAMを凌駕する設計でWindowを確保することが可能となり、優れた拡張性を持たせることが出来るものと期待しています。

今後の展開

今回新たに開発した、MRAMメモリのアーキテクチャおよび一括書込み方式を実用化につなげるためには、10 nm台サイズの微細なMTJ素子を用いたスピントロニクス物理原理の効率向上を図る必要があります。なかでも、VCMA効果をさらに一層高めたMTJメモリ素子や材料技術の開発を必要とします。今後は、ImPACT 佐橋プログラムの中で、湯浅新治プロジェクトリーダ(産業技術総合研究所 スピントロニクスセンター長)を中心に、産業技術総合研究所、物質・材料研究機構、東北大学AIMR、との連携を強化して、この課題の解決に取り組んで参ります。

参考図

VoCSMの長所とその理由

| 長所 | その理由 |

|---|---|

| 低消費エネルギー | 独特のVoCF-writingシーケンス |

| 高集積 | 複数のMTJ記憶素子をひとつのString上に配置 |

| 読出し時の誤書込み耐性 (Read Disturbance Robust) |

書込み電流の経路と読出し電流の経路が異なる。(実質上三端子構造) |

| トンネル寿命制限なし | トンネル障壁に書込み電流が流れない。 |

用語解説

(注1)IoT

Internet of thingsの略。従来、パソコンやサーバー、プリンタなどのIT関連機器が接続されていたインターネットが、それ以外のさまざまな“モノ”に接続され、情報交換することにより相互に制御する仕組みまたは、それによる社会の実現を意味します。

(注2)CPS

Cyber Physical Systemの略。実世界(Physical空間)にある多様なデータをセンサーネットワークなどで収集し、サイバー空間で大規模データ処理技術などを駆使して分析を行い、そこで創出した情報によって、産業の活性化や社会問題の解決を図っていくものです。

(注3)スピントロニクス

電子の持つ電荷(電気的性質)とスピン(磁気的性質)の両方を利用して、新しい機能を持った電子デバイスを創出しようとする分野です。

(注4)MTJ記憶素子

Magnetic Tunnel Junctionの略。記録層、絶縁層、磁化固定層からなる素子をMTJ記憶素子と言います。両強磁性層の磁化の向きの相対配置によってMTJ素子の電気抵抗が変化する現象は、トンネル磁気抵抗効果(注11)と呼ばれています。記録層、磁化固定層の磁化が平行状態のとき抵抗は低く、反平行状態のとき抵抗は高くなります。

(注5)MRAM

MTJ記憶素子を用いた不揮発性メモリを「MRAM」と言います。MRAMでは、MTJ記憶素子の高抵抗状態と低抵抗状態を「0」、「1」に対応させて1ビットの情報記憶を行います。 MRAMの記憶書込み方式としては、磁界を用いる方式、電流を用いる方式、電圧を用いる方式などがあります。

(注6)STT-MRAM

電流書込み方式のMRAMは「STT-MRAM」(Spin-transfer-torque MRAM)と呼ばれ、現在世界規模で製品開発が進められています。MTJ記憶素子に流す電流の向きを変えることにより、記憶層のデジタル情報(「0」、「1」)を書き換えます。

(注7)CMOS

Complementary metal oxide semiconductorの略。P型とN型のMOSFETをデジタル回路(論理回路)の論理ゲートなどで相補的に利用する回路方式(論理方式)、およびそのような電子回路やICのこと。

(注8)VCMA

Voltage Control Magnetic Anisotropyの略であり、磁性体表面に電界を印加するとその磁気異方性が変化する効果をいいます。

(注9)スピンホール効果

タンタル(Ta)などの重金属に電流を通電すると、その表面にスピン偏極した電子が集まる効果をいいます。

(注10)Read Disturbance

読出し電流で、誤書込みを生じる事。STT-MRAMの場合、読出し電流(~10μA)により記憶層の磁化に弱いながらもスピントルクが作用し、意図しない書込みが起こる可能性があります。

VoCSMの場合、Read 印加電圧の極性を適切に選択するとRead Disturb Robustとできます(流れるリード電流も小さいため、スピントルクも小さくなります。)

(注11)トンネル磁気抵抗効果

トンネル障壁を挟んだ磁性層の磁化の方向が平行状態のときと反平行状態のときで、そのトンネル抵抗が変化する効果をいいます。

IEDM MRAMセッションプログラム抜粋

27.6 “Voltage-Control Spintronics Memory (VoCSM) Having Potentials of Ultra-Low Energy-Consumption and High-Density”

お問い合わせ先

<研究に関すること>

株式会社 東芝 研究開発センター

〒212-8582 川崎市幸区小向東芝町1 株式会社 東芝 研究開発センター

Tel:044-549-2056

<ImPACTの事業に関すること>

内閣府 革新的研究開発推進プログラム担当室

〒100-8914 東京都千代田区永田町1-6-1

Tel:03-6257-1339

<ImPACTプログラム内容およびPMに関すること>

科学技術振興機構 革新的研究開発推進室

〒102-0076 東京都千代田区五番町7 K's五番町

Tel:03-6380-9012 Fax:03-6380-8263

E-mail:impact@jst.go.jp

<報道担当>

株式会社 東芝 広報・IR部

〒105-8001 東京都港区芝浦1-1-1

Tel: 03-3457-2100

科学技術振興機構 広報課

〒102-8666 東京都千代田区四番町5番地3

Tel: 03-5214-8404 Fax: 03-5214-8432

E-mail: jstkoho@jst.go.jp