LSI・ストレージ

世界初、2Xnm世代以降トランジスタ向けに高速で低消費電力な1Xnmサイズの不揮発性STT-MRAM用MTJ素子を開発

2016年6月

概要

当社は、将来の高性能・低消費電力コンピューティングに必要なキャッシュメモリ向けに、2Xnm世代以降のシリコントランジスタで製造可能な不揮発性磁性体メモリSTT-MRAM用MTJ(Magnetic tunnel junction)素子を開発しました。

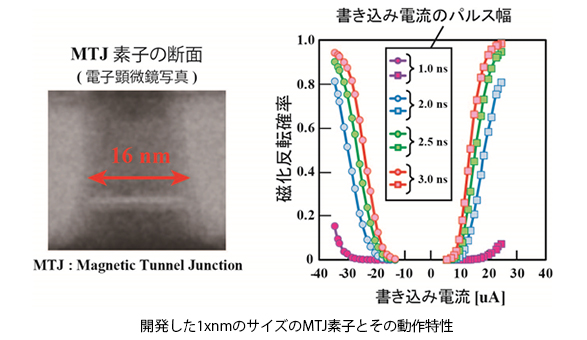

キャッシュメモリ用途として要求される3ns以下の高速動作性と100uA以下の低電流動作特性を、世界で初めて1XnmまでのMTJ素子で実現しました。本メモリを使うことで、従来のキャッシュメモリ(SRAM)と比較して消費電力を低減することが可能になります。本技術の詳細について、米国ハワイで開催される国際会議VSLI2016にて、6月15日(現地時間)に発表します。

開発の背景

近年、様々なコンピューティング機器において高性能化と低消費電力化のニーズが高まっています。これらに使われる半導体チップにおける消費電力は、内部にある揮発性メモリ(SRAM)の容量増大とともに、メモリ部分の消費電力の低減が大きな課題となってきています。特に、揮発性メモリは内部の漏れ電流(リーク電流)に起因した電力の消費量が大きく、現在利用されている揮発性メモリを不揮発性メモリに変えることが期待され、当社は、高速で低消費電力の不揮発性磁性体メモリ「MTJ:Magnetic Tunneling Junction」の開発を続けてきました。

これまでに、31nmのMTJを65nm世代のトランジスタ回路に適用し、キャッシュメモリ4Mb-RAMで消費電力が世界最小となることを実証してきました。しかし、この技術を2Xnm世代以降の最先端トランジスタにも適用していくためには、MTJの高速動作と低消費電力動作について、1Xnmまで微細化した素子で実現することが必要でした。

本技術の特徴

当社は、新たな微細加工技術により、1XnmサイズのMTJ素子を開発し、3ns以下の高速動作と100 uA以下の低電流動作を世界で初めて実証しました。キャッシュメモリで要求されるデータ保持時間(retention)を有し、高性能キャッシュメモリに必要な2-4nsの書き込み動作で優れたエラーレート特性を示すことを確認しました。典型的キャッシュメモリ動作を想定した3nsの書き込みを繰り返す試験で、誤書き込みが起きないことを確認しました。キャッシュメモリの低消費電力化により、コンピューティング機器の消費電力をさらに低減させることができると考えられます。

今後の展望

今回開発した磁性体メモリの技術は、NEDO(新エネルギー・産業技術総合開発機構)のノーマリオフコンピューティング基盤技術開発プロジェクトとして進められた成果です。当社は、これまで開発した新型磁性体メモリ技術をさらに改良し、より微細なシリコントランジスタに適合したメモリを継続的に開発してまいります。