LSI・ストレージ

小面積で低価格の不揮発FPGAを実現する回路技術を開発

2016年6月

概要

当社は、カスタムLSIに集積可能でチップ製造後にユーザーにて回路情報を書き換えることができるFPGA(field-programmable gate array)について、不揮発メモリの技術を応用することで、従来よりも小面積、かつ低価格で製造できる回路技術を開発しました。本技術の詳細を、ホノルルで開催される半導体デバイスに関する国際会議「VLSI技術シンポジウム2016」にて、6月14日(現地時間)に発表します。

開発の背景や市場動向

近年、IoTの普及などにより半導体に求められる用途が多様化しています。また、カスタムLSIの開発費は著しく増大し、用途に応じた細やかな回路を設計することが難しくなっています。ソフトウエアによる計算処理では消費電力あたりの処理性能が低く十分な性能を満たさないことから、チップ製造後に回路情報を書き変えられるFPGAの需要が高まっています。従来のFPGAでは、回路情報を記憶するメモリセルの面積が大きく、チップ価格が高くなるという課題があり、小面積、かつ低価格のFPGAが求められていました。

本技術の特徴

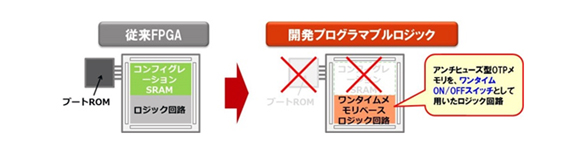

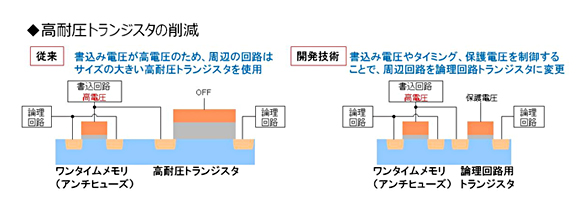

当社は、FPGAを構成するロジック回路のスイッチをアンチヒューズ型の不揮発ワンタイムメモリ素子を応用した高密度スイッチアレイに代替することで、ロジック回路とメモリセルを一体化し、従来より小面積で設計できる不揮発FPGAを実現しました。また、書き込みに高電圧が必要なアンチヒューズ素子と低電圧で動作するロジック回路を劣化させずに接続する回路を開発し、サイズが大きくチップ面積増大の一因となっている高耐圧トランジスタの使用を、従来の1/2に抑えました。これらにより、メモリとロジック回路との高集積化が可能になり、チップ価格が低い不揮発FPGAを実現しました。

当社は、今回開発した回路技術を適用した不揮発FPGAについて、回路情報を書き込むソフトウエアを開発し、実用途に即した機能ごとの面積を見積もったところ、従来のほぼ半分まで縮小することができ、同じ半導体世代のFPGAの中では世界最小の回路面積を実現しました(当社調べ)。本技術は標準CMOSで実現しており、カスタムLSIに集積できるため、様々な用途に対して細やかに回路の調整が可能なカスタムLSIを実現します。

今後の展望

当社は、今回開発した回路技術を当社のカスタムLSI向け回路群の一つとして、2017年度以降の実用化を目指して研究を進めており、今後も不揮発メモリ技術の応用範囲を拡大していきます。