LSI・ストレージ

磁性体メモリSTT-MRAMを用いた電力性能世界最高のキャッシュメモリを開発

2016年2月

概要

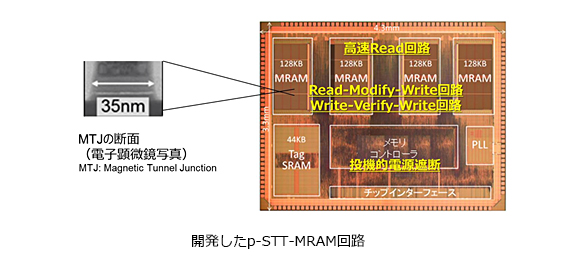

当社は、高性能プロセッサやSoC(System on Chip)チップ向けに、65nm世代のシリコントランジスタに混載した4Mbクラスの新方式磁性体メモリSTT-MRAMメモリ回路を開発しました。

本メモリ回路は、3.3nsメモリアクセスというキャッシュメモリ用に十分な高速性能を有し、さらに、従来の混載メモリ(SRAM)と比較して消費電力を10分の1以下にできます。これは、あらゆる種類の混載メモリと比べて世界最高の電力性能となります。本技術の詳細は、米国サンフランシスコで開催される半導体回路国際会議ISSCCにて、2月2日(現地時間)に発表します。

開発の背景

近年、IoT、ウエアラブル、さらにスマートフォン、デスクトップPCからデータセンタ用サーバまで、様々な用途の半導体チップ市場が拡大しており、高性能化と低消費電力化のニーズが高まっています。これらの半導体チップにおける消費電力は、内部にある揮発性メモリ(SRAM)の容量増大とともに、メモリ部分の消費電力の低減が大きな課題となってきています。特に、メモリ内部の漏れ電流(リーク電流)に起因した電力の消費量が大きく、現在利用されている揮発性メモリを不揮発メモリに変えることが期待され、当社は、高速で低消費電力の不揮発性磁性体メモリ「MTJ:Magnetic Tunneling Junction」の開発を続けてきました。

しかしメモリ書き込み時の電力やメモリ制御回路部(周辺回路)が消費する電力が大きいため、メモリアレイ回路が低消費電力(ノーマリオフ (注1))を実現してもキャッシュメモリ全体としては消費電力が十分小さくなっていませんでした。

本技術の特徴

当社は、現状の課題を解決するために、メモリ制御回路部をノーマリオフ動作状態に近づけるため、サブ100nsで高速電力遮断・復帰が可能な回路を開発し、メモリ動作状態に応じて動作に必要な部分以外は高速で電源遮断できるように改良しました。また、効率的な電源遮断のために、メモリアクセスパターンをモニターして、次のアクセスパターンを高い確率で予測するアルゴリズムも開発し、メモリ制御回路に内蔵しました。これらの技術により、従来の混載メモリ(SRAM)と比較して消費電力を10分の1以下まで削減することができました。

今後の展望

今回開発した磁性体メモリの技術開発は、東京大学中村宏教授(情報理工学系研究科)のグループと共同で、NEDO(新エネルギー・産業技術総合開発機構)のノーマリオフコンピューティング基盤技術開発プロジェクトとして進められています。当社は、これまで開発した新型磁性体メモリ素子と回路をさらに改良し、より微細なシリコントランジスタに適合したメモリ技術を継続的に開発してまいります。

(注1)システムとしては動作中であっても、省電力化のために真に動作すべき構成要素以外の電源を積極的に遮断すること。