LSI・ストレージ

新方式磁性体メモリ素子を用いた世界最高性能のプロセッサ用不揮発メモリ回路を開発

2015年3月

概要

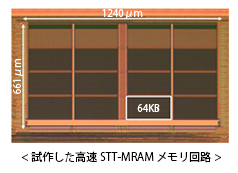

当社は、高性能プロセッサやSoC(System on Chip)チップ向けに、1Mbクラスの新方式磁性体メモリSTT-MRAMメモリ回路を開発しました。当社で開発した消費電力が小さい磁性体メモリMTJ(Magnetic Tunnel Junction)を高速かつ低消費電力で効率よく動作させるためのメモリ回路を開発しました。

本メモリ回路は、3.3nsメモリアクセスというキャッシュメモリ用に十分な高速性能を持ちます。さらに、従来の混載メモリ(SRAM)と比較して消費電力を約80%削減できます。これは、あらゆる種類の混載メモリと比べて世界最高の電力性能となります。本技術の詳細は、米国サンフランシスコで開催される半導体回路国際会議ISSCCにて、2月24日(現地時間)に発表しました。

開発の背景

近年、IoT、ウエアラブル、さらにスマートフォンからクラウド向けデータセンタまで、様々な用途の半導体SoC市場が拡大しており、その高性能化と低電力化のニーズが高まっています。これら半導体チップの消費電力は、内部にあるキャッシュメモリ(SRAM)容量増大とともに、メモリの消費電力が支配的となってきています。特に、メモリ内部の漏れ電流(リーク電流)に起因する電力が問題でした。この問題を解決するために、現在利用されている揮発性メモリを不揮発メモリに変えることが期待されてきました。当社では、以前からMTJという高速で低消費電力の磁性体メモリを開発してきました。

しかし、メモリ制御回路部(周辺回路)が消費する電力が大きく、折角メモリアレイ回路が低消費電力(ノーマリオフ)なのに、キャッシュメモリ全体としては消費電力が十分小さくなっていませんでした。

本技術の特徴

当社は、現状の課題を解決するために、メモリ制御回路部をノーマリオフ動作に近くするため、サブ100nsで高速電力遮断・復帰が可能な回路を設計し、動作実証させました。具体的には、電源遮断後の復帰時間を減らすため、電源遮断する領域を7つに分割し、各領域に電源スイッを実装し、メモリ動作状態に応じて動作に必要な部分以外は電源遮断できるように改良しました。主な動作モードでの実測値で、最速22nsで電源遮断後からの復帰を確認しました。(キャッシュメモリアクセスの平均待機時間(約30ns)よりも短い。)さらに、書き込み動作と読み出し動作時の無駄な消費電力を削減する工夫も盛り込みました。これらの技術により、従来の混載メモリ(SRAM)と比較して消費電力を約80%削減できます。

今後の展望

今回開発した磁性体メモリの技術開発は、NEDO(新エネルギー・産業技術総合開発機構)のノーマリオフコンピューティング基盤技術開発プロジェクトにて進められております。当社は、これまで開発した新型磁性体メモリ素子と回路をさらに改良し、プロジェクトの最終年度(2015年度)までに、プロセッサ全体の消費電力を10分の1に抑えることが可能な不揮発メモリ技術の開発を目指します。