LSI・ストレージ

超低消費電力LSI向け10nm径ナノワイヤトランジスタ

2012年6月

概要

立体構造のナノワイヤトランジスタは、超低消費電力LSIの実現に向けたトランジスタ構造の有力候補のひとつです。当社は、基板にかける電圧を制御してトランジスタの待機時の消費電力を1桁低減できる、10nm径トライゲート構造のナノワイヤトランジスタを開発しました。2012年6月に米国で開催された半導体デバイスに関する国際会議「VLSI技術シンポジウム」で、本成果を発表しました。

開発の背景

近年、超低消費電力LSIを目指し、トランジスタのチャネル部がナノメートル級の細いワイヤ形状のシリコンからなるナノワイヤトランジスタの開発が進められています。細線状のチャネルをゲートが取り囲むことによりゲートによる制御性能が向上し、短チャネル効果による電源電圧オフ時のリーク電流の大幅な抑制が可能です。しかし、ゲートがナノワイヤチャネルの下部に潜り込み、チャネル全体を取り囲むゲートオールアラウンド構造であるため、消費電力の低減に有効な基板へ電圧を印加する手法の適用が困難であり、さらなるLSI低消費電力化の阻害要因となっていました。

本技術の特長

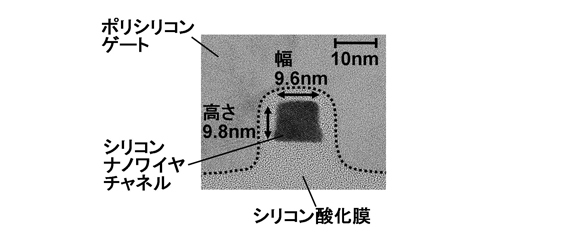

今回、ナノワイヤ径を10nmまで小さくし、かつナノワイヤ下酸化膜層を20nmまで薄膜化したトライゲートナノワイヤトランジスタの動作に世界で初めて成功しました。このトランジスタの基板にマイナス1Vの電圧を印加し、待機時のオフ電流(消費電力)が1桁低減されることを実証しました。また、このトライゲートナノワイヤトランジスタで構成されたSRAM(揮発性メモリ)の基板に同じくマイナス1Vの電圧を印加すると、動作の安定性が26%向上し、待機時の電源電圧が21%低減できることも確認できました。

今後の展望

当社は、今回開発した技術を生かし、更に高性能で低消費電力のLSIの研究開発を行っていきます。なお、今回の研究開発の一部は、NEDOから受託したプロジェクト「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」の一環として実施したものです。