- Back to the previous page

- Nano Materials & Devices

3D Random Telegraph Noise Simulator for Development of High-Resolution CMOS Image Sensor

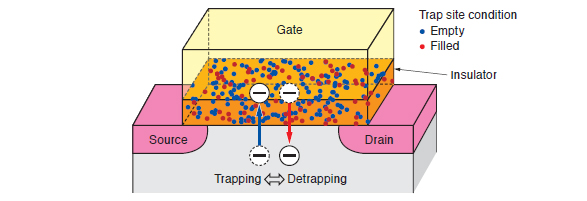

Random telegraph noise (RTN), one of main causes of image degradation in complementary metal-oxide semiconductor (CMOS) image sensors, is caused by current fluctuation originating in charge trapping and de-trapping at the gate insulator of transistors. As conventional device simulators cannot reproduce the dynamic behavior of charge trapping and detrapping at a gate insulator, it is difficult to reduce RTN efficiently.

As a solution to this issue, Toshiba has developed a three-dimensional (3D) device simulator that can predict RTN to improve the resolution of CMOS image sensors through the modeling of trapping and detrapping processes considering traps isolated in the insulator. This simulator makes it possible to predict the noise intensity according to the device structure and bias conditions. Furthermore, it can quantitatively simulate 3D trap site distribution by a comparison of measured and simulated data.

This simulator is expected to reduce the development period for CMOS image sensors by 20% compared with the time required for conventional prototype fabrication.

Outline of RTN simulation