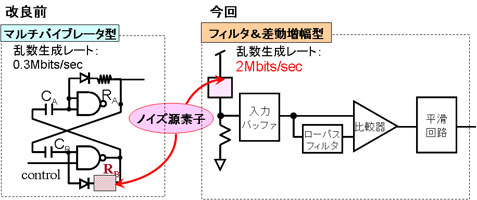

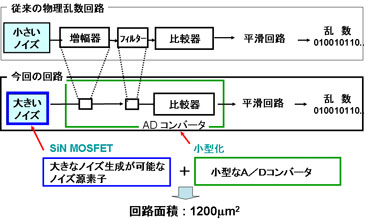

| 世界最高性能の高速物理乱数生成回路の開発について 2008年2月7日 小型素子で実用的生成レートを実現 当社は、ICカードや携帯機器の暗号セキュリティ向けに導入が期待される物理乱数の新技術として、実用的な高速生成レートと高い信頼性を両立しながら、面積あたりの生成レートで世界最高性能の回路技術を開発しました。本成果については、2月3日から米サンフランシスコで開催中の半導体国際学会ISSCC(国際固体素子回路学会)において、本日(現地時間)講演を行いました。 新技術では、乱数源としてトランジスタの窒化シリコン膜が電子を捕捉・放出する際のノイズを利用する当社独自の小型素子を用い、発生したノイズ信号を乱数に変換するデジタル変換回路に信号を効果的に増幅させる小型のA/Dコンバータを採用することで、回路全体を従来比で 9割近く小型化するとともに、乱数の生成レートを実用的レベルである2.0Mbits/sに高速化しました。また、生成した乱数については、物理乱数の信頼性課題である温度依存性がないことも確認しています。 現在、おもにICカードなどに用いられている暗号セキュリティ技術では、ソフトウェアによる擬似乱数が一般的で、解読するコンピュータの高性能化などから、将来的な安全上の課題が指摘されています。このような背景のなか、当社は、自然界の物理的な揺らぎを利用するため予測不可能な高い安全性をもつ物理乱数回路について、今回の技術をもとに更なる改善を進め、数年以内の実用化を目指します。 なお、本成果は、独立行政法人・情報通信研究機構(NICT)による、民間基盤技術研究促進制度に係る研究課題「高度情報セキュリティに向けた真性乱数生成集積回路の研究開発」の一環として開発したものです。開発の概要 当社では、これまでナノサイズのトランジスタによる温度依存性のない新構造の物理乱数源素子を用いた乱数生成回路の開発を進めてきました。今回、この素子と組み合わせるデジタル変換回路において、乱数素子から発生した高周波領域の大きいノイズ信号を効果的に活用できる新方式を採用し、全体の最適化を行ったもので、概要は次のとおりです。 (1)フィルタ&差動増幅型A/Dコンバータ

(2)ノイズ発生効率向上によるA/Dコンバータの小型化

(3)温度依存性のない高い信頼性 |

|

プレスリリース記載の情報(製品価格/仕様、サービスの内容、お問い合わせ先、URL等)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。最新のお問い合わせ先は、東芝全体のお問い合わせ一覧をご覧下さい。 |  |