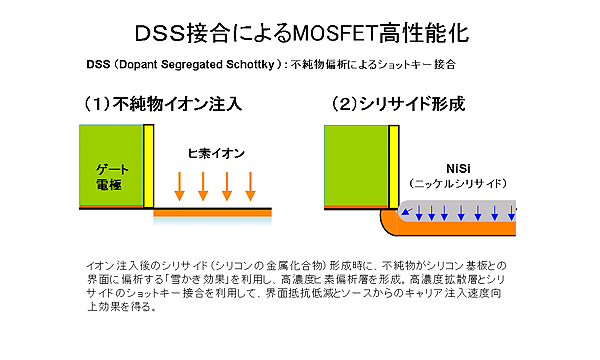

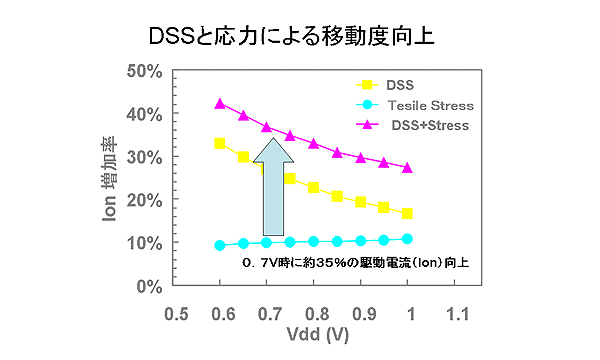

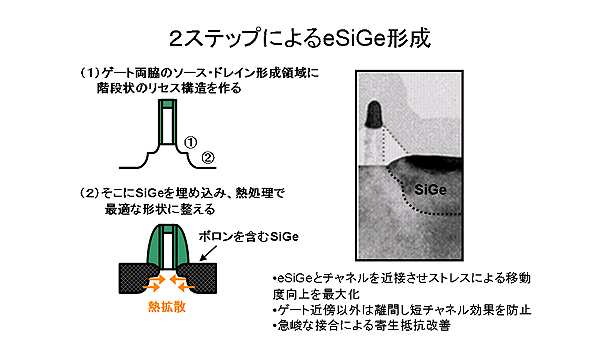

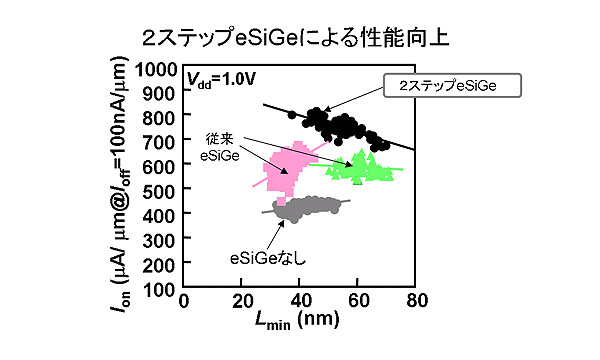

| 32nm世代LSI向け高性能トランジスタの開発について 2007年6月13日 高性能化の要素技術を確立 当社は、32nm世代LSI向けに、CMOS素子を構成するnMOS、pMOSそれぞれについて、高性能化のための2種類の要素技術を確立しました。今後、要素技術をCMOSプロセスとしての統合や技術の最適化を通じ、2010年までに実用化を目指します。 nMOSでは、ソース・ドレイン電極と基板の界面に不純物を偏析させるDopant Segregated Schottky(DSS)技術によって界面抵抗の低減とキャリア速度の向上をはかり、低電圧動作と高速化を実現しました。さらに、歪み応力膜によるキャリア移動度の向上を組合せ、0.7Vの低電圧でのトランジスタ駆動力を従来構造に比べて約35%向上させました。 pMOSでは、キャリア移動度を向上させるため、ソース・ドレインに埋め込みSiGe構造を導入しました。また、この構造を形成するにあたり、短チャネル効果を抑制しつつ応力効果を最大化する、新開発の二段形状の埋め込みSiGe構造とプロセスを採用しました。ゲート近傍ではチャネルと埋め込みSiGeを近接させて応力によるチャネル移動度を向上させながら、ゲートから離れる深部では離間させて短チャネル効果を防止します。この構造により、前世代(45nm)pMOSに対し30%以上の高速動作を実現しています。 なお、今回の技術については、6月12日から京都で開催中の国際学会「VLSIシンポジウム」において、本日講演を行いました。

|

|

プレスリリース記載の情報(製品価格/仕様、サービスの内容、お問い合わせ先、URL等)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。最新のお問い合わせ先は、東芝全体のお問い合わせ一覧をご覧下さい。 |  |