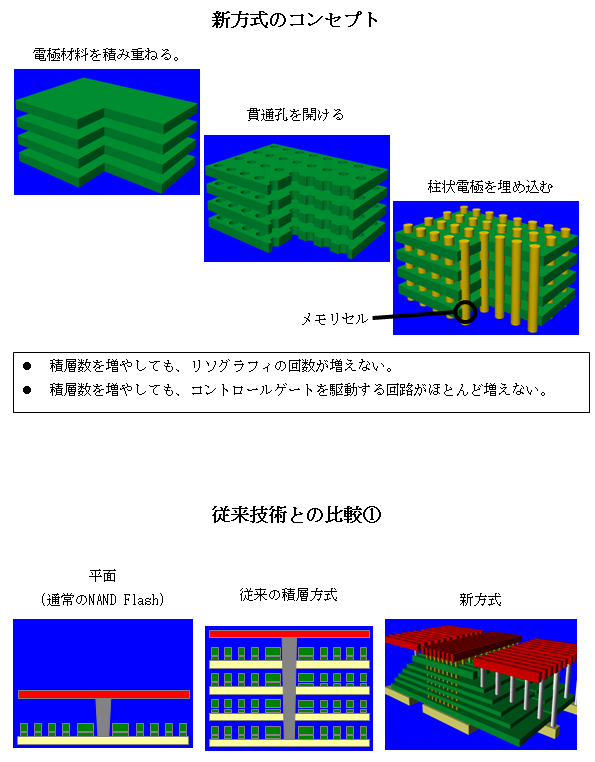

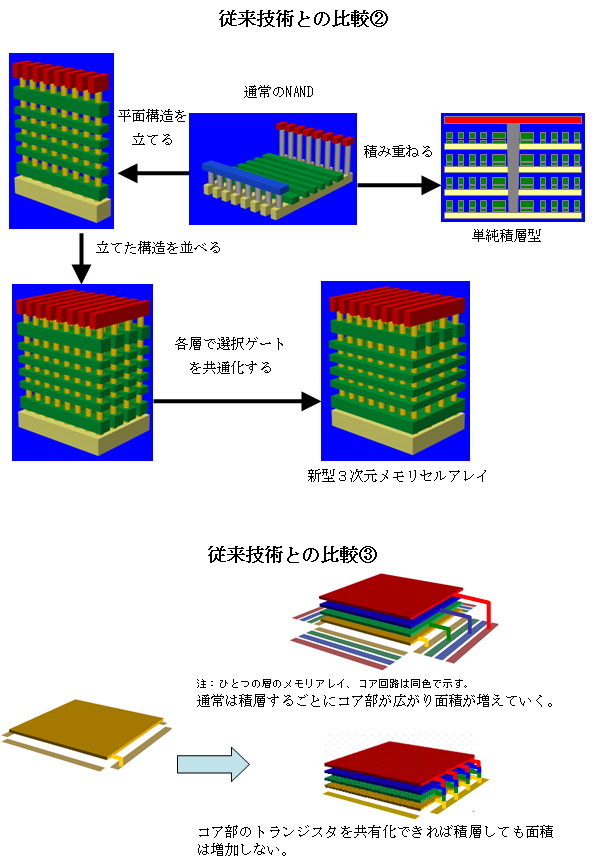

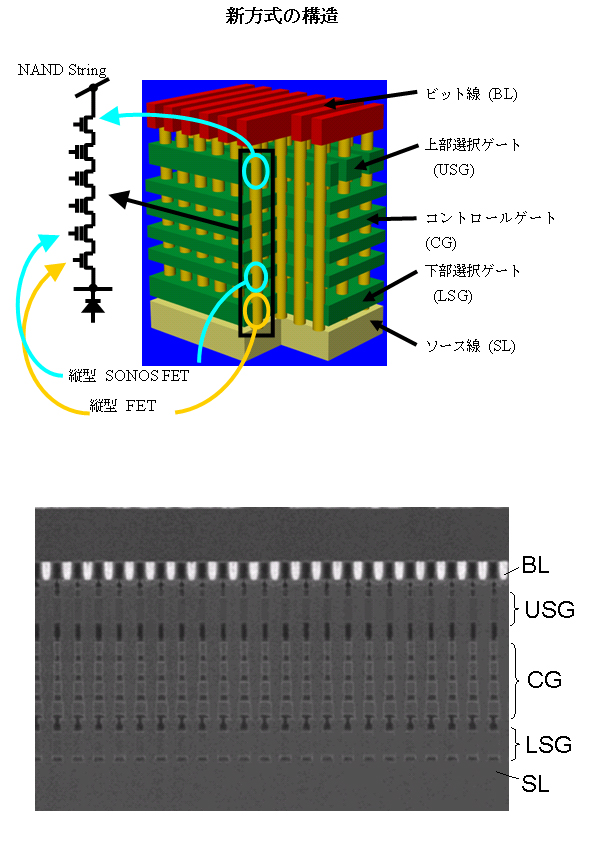

| 3次元構造を採用したNAND型フラッシュメモリの新技術を開発 2007年6月12日 微細化によらず大容量化できる新型セルアレイを採用 当社は、NAND型フラッシュメモリの将来的な大容量化に向け、積層した電極に柱状の素子列を垂直に貫通させて高密度配列した新型3次元メモリセルアレイ(セル配列)技術を開発しました。 従来の積層メモリ技術は、シリコン基板上に通常の平面メモリセルを形成する工程を層数分繰り返して積み上げていく構造で、一層あたりの製造工程数が多く、大容量化には不向きでした。 今回はセル構造などの要素技術を確立したもので、今後当社では、本技術を次々世代以降に適用する技術の候補と位置付け、従来方式と同等の性能や信頼性の確保に向け開発を進めます。 本方式の加工プロセスでは、まず、ゲート電極と層間絶縁膜を互い違いに積み重ねた積層構造に、最上層から最下層まで貫通する孔を一度に開け、不純物を含むシリコンを柱状に埋め込みます。 NAND型のメモリセルは、多数の素子を直列接続で一括処理する方式です。今回の技術では、積層数を増やすほど接続素子数が増え、チップ面積を増やすことなく大容量化できます。

|

|

プレスリリース記載の情報(製品価格/仕様、サービスの内容、お問い合わせ先、URL等)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。最新のお問い合わせ先は、東芝全体のお問い合わせ一覧をご覧下さい。 |  |