| デジタル家電向けメディア・プロセッサ「MeP」のハイエンド版コア「MeP‐h1」を開発 2005年8月17日

当社は、デジタル家電向けSoC*1などに組み込むメディア・プロセッサ「MeP」*2のハイエンド版コアとして、65nmプロセスで動作周波数1GHzの高速処理を実現する新コア「MeP‐h1」を開発しました。 新コアでは、高速化の手法として、命令を時分割して多重的に処理するパイプラインの段数を従来の5段から9段に増やしました。また、処理待ち時間の低減などの調整を行う「リオーダー・バッファ回路」を取り入れ、ユーザーが命令を追加するカスタム仕様に対してもプロセッサ全体の処理を常に最適化できる設計となっています。 現在、マルチメディア関連機器の市場は急成長を続けていますが、アプリケーションごとに要求される性能などが異なり、データ処理量も急激に増加しているため、カスタマイズできる高性能な内蔵プロセッサが求められています。 なお、本技術については、米国カリフォルニア州・スタンフォード大学で、8月14日から開催されているプロセッサの国際カンファレンス「HOT CHIPS17」において、本日(現地時間8月16日)に発表しました。

MePの概要 MePは、ユーザーのニーズに応じて命令セットや混載メモリの容量など数100万通りのパターンから選択できるコンフィギュラブルプロセッサです。映像や音声、通信などの大容量データを高速処理することが求められるデジタルメディア機器に最適な32ビットRISCプロセッサで、チップ面積が小さく、高速・低消費電力処理に加え、以下のような特長があります。

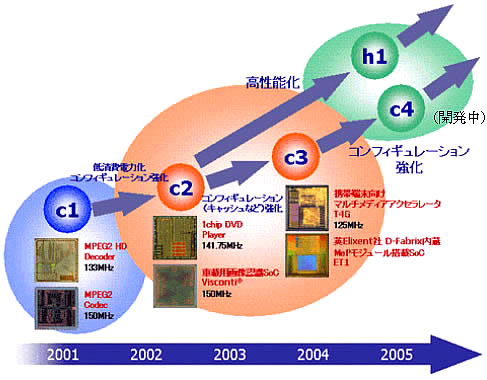

当社では、MePを自社で利用するほか、設計の柔軟性などの特長を求める社外ユーザーに対してもIP(設計資産)を公開しています。MePを製品に適用したいユーザーは、専用のWebサイト(http://www.MePcore.com/)で会員登録し契約に同意すれば、設計データをダウンロードして利用できます。 MePコアのロードマップ 2001年に5段パイプライン構成(cシリーズ)の最初のコア「MeP-c1」を開発した後、「MeP-c2」「MeP-c3」と順次機能の拡充を図ってきています。今回、9段パイプライン構成で開発した「MeP-h1」は、新しい高性能プロセッサコアhシリーズの最初のコアと位置づけています。一方、cシリーズの改良版として、「MeP-c4」コアも開発中です。

|

|

プレスリリース記載の情報(製品価格/仕様、サービスの内容、お問い合わせ先、URL等)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。最新のお問い合わせ先は、東芝全体のお問い合わせ一覧をご覧下さい。 |  |