IBM、ソニー、SCEI、東芝 次世代プロセッサ「Cell」の技術仕様を公開

2005年2月8日

8個の独立した浮動小数点演算コアとPowerベースのコアを持つ革新的なアーキテクチャ・デザインにより最新のPC向けプロセッサの10倍以上の性能を実現

IBMコーポレーション

ソニー株式会社

株式会社ソニー・コンピュータエンタテインメント

株式会社 東芝 IBMコーポレーション(以下、IBM)、ソニー株式会社および株式会社ソニー・コンピュータエンタテインメント(以下、ソニーグループ)、株式会社東芝(以下、東芝)は、米国サンフランシスコで開催中のISSCC(国際固体素子回路会議)において、4社共同で開発を進めてきた高性能プロセッサ(コードネーム:Cell)の主な技術仕様を公開しました。 8個の独立した浮動小数点演算コア(SPU)とPowerベースのコアを持つ革新的なマルチコア・アーキテクチャ・デザインの採用により、Cellは4GHzを超えるクロックスピード(動作周波数)とスーパーコンピュータ並みの浮動小数点演算性能を実現しています。

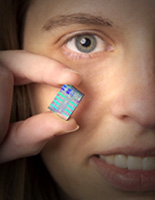

IBM、ソニーグループ、東芝各社のエンジニアは、米国テキサス州オースチンに設置した共同デザインセンターで2001年3月からCellプロセッサの開発を進めてきました。今回の試作チップは、90nmプロセスのSOI*(シリコン・オン・インシュレータ)技術を用いて試作したもので、221mm2のチップ面積に2億3400万個のトランジスタを搭載しています。 マルチコア/マルチプロセッサ・アーキテクチャの採用と超高速のデータ転送能力により、Cellはさまざまなケースで最新のPC用プロセッサの10倍以上の性能を実現しています。これにより、次世代のコンピュータエンタテインメントやリッチメディア・アプリケーション用途で必須となる膨大なリアルタイム処理において飛躍的な性能向上を実現しました。併せて、Cellプロセッサは既存のオペレーティングシステム(OS)に加え、コンピュータエンタテインメント・システムやデジタル家電に不可欠なリアルタイムOS、また特定用途に使われるゲストOSなど、複数のOSを同時にサポート・実行することが可能です。 「スーパーコンピュータ・オン・チップ」ともいうべきCellプロセッサの高い演算性能は、IBMの高性能サーバーに使用されている先進多重処理技術やソニーグループのコンピュータエンタテインメントシステム、東芝の半導体技術を融合することにより実現したもので、超高性能のブロードバンドプロセッサとして、産業向けのアプリケーションから次世代のデジタル家電に至るまで幅広い応用が期待されています。 Cellプロセッサの生産は、米国ニューヨーク州イーストフィッシュキルにあるIBMの300mmウエハー対応の半導体製造拠点で開始し、続いてソニーグループが長崎県諫早市に保有する半導体製造拠点(Fab2)でも年内に生産を開始する予定です。 今後IBMとソニーグループ、東芝は、デジタルテレビやホームサーバー、スーパーコンピュータなど、さまざまなアプリケーション向けに、Cellプロセッサの応用範囲を広げてまいります。 <Cellプロセッサに関して本日公開された主な内容>

| ・ |

8個の独立した浮動小数点演算コア(SPU)を持つ革新的なアーキテクチャ・デザイン |

| ・ |

4GHzを超えるクロックスピード(動作周波数)の実現(初期テストでの評価結果) |

| ・ |

膨大な浮動小数点演算能力を持つマルチコア・チップ |

| ・ |

OSを特定せず、複数OSを同時サポート |

IBM システムズ・アンド・テクノロジー・グループ

グループ・エグゼクティブ兼シニア・バイス・プレジデント ウィリアム・ザイトラーのコメント:

「本日のCellチップの画期的なアーキテクチャ・デザインの発表は、IBM、ソニーグループ、東芝が4年前に米国テキサス州オースチンに合同で設立したデザイン研究所で開始した意欲的なプロジェクトにおける重要な節目です。グラフィックスならびにマルチメディアの性能の新時代を予示するオープンなマルチコア・マイクロプロセッサは、協業の具体的な成果です」 ソニー株式会社 副社長兼COO、

株式会社ソニー・コンピュータエンタテインメント 社長兼グループCEO 久多良木健のコメント:

「大きな志を持って2001年3月に始まったプロジェクトの成果をISSCCで発表できることを誇りに思います。Cellはコンピュータの歴史の中で新たな幕開けをするものであり、いよいよコンピュータサイエンスの新しい一章が始まろうとしています。」 株式会社東芝 執行役常務 セミコンダクター社社長 室町正志のコメント:

「IBM、ソニーグループ、東芝が、各社の持つ高い技術力と優れたリソースを結集し、ここに、既存のプロセッサを凌駕する全く新しいアーキテクチャをもつ革新的なCellプロセッサができたことを誇りに思います。Cellプロセッサは、家電、ホームエンターテインメント、産業用システムまで、大量の情報を扱うあらゆる先進のブロードバンドアプリケーションの核として機能し、デジタルコンバージョンの進化を促進していくものと考えます。」

| * |

SOI(シリコン・オン・インシュレータ)=絶縁膜上に形成した単結晶シリコンを基板とした半導体および半導体技術 |

添付資料 次世代プロセッサ「Cell」 Cellは最新テクノロジーの導入により、日常生活の中で、高度なブロードバンド・メディア処理をスーパーコンピュータ並みの高性能で実現することを可能とします。 概要:

| ・ |

従来の常識を打ち破るアーキテクチャ・デザイン:8個のSynergistic Processing Units (以下、SPU)とPowerベースコアで構成。4GHzを超えるクロックスピードを実現(初期テストでの評価による) |

| ・ |

マルチコア・アーキテクチャの採用:高性能な浮動小数点演算機能をもつ8個のSPUと64ビットのPowerベースのプロセッサコアで構成 |

| ・ |

OSを特定せず、マルチOSの同時実行に対応 |

| ・ |

設計最適化のために以下を適用:独自の回路技術、設計再利用のためのモジュール性とカスタムクロック構造、独自のパワー・熱制御コンセプトのデザインへの採用 |

マルチコア・アーキテクチャ

| ・ |

各128本の128ビットレジスタファイルと256KBのローカルストアを有する独立した8個のSPU |

| ・ |

2スレッドSMT機能を持つVMX拡張付き64ビットPower ArchitectureTM -システムメモリに対して10ウェイのコヒレント・スレッド・マシンとして認識。 |

| ・ |

2.5MBオン チップメモリ(512KB L2 + 8* 256KB) |

| ・ |

トランジスタ数: 2億3,400万個 |

| ・ |

試作チップ面積:221mm2 |

| ・ |

90nmのSOI(Silicon-on-insulator)プロセス技術の採用 |

| ・ |

モジュラー構造を採用、SPU数の増減により浮動小数点演算能力の調整が可能。 |

ブロードバンド・アーキテクチャ

| ・ |

64ビットPower ArchitectureTMとの互換性 |

| ・ |

SPUはSIMD構造とローカルストアをもったRISCアーキテクチャを採用 |

| ・ |

プロセッサあたり128以上のメモリへの同時データトランザクション |

| ・ |

96B/cycle のハイスピード内部インターコネクト・バス |

リアルタイム・アーキテクチャ

| ・ |

リソース割付機能(帯域幅制御のため) |

| ・ |

キャッシュ・ロック機能(置換制御テーブルによる) |

| ・ |

同時実行される複数のOS間にまたがるリアルタイム応答性を持つ仮想化機能サポート |

高度なセキュリティ機能を実現するアーキテクチャ

| ・ |

柔軟なセキュリティプログラミングを実現するSPUダイナミック・コンフィギュレーション |

最新技術の結集

| ・ |

従来型アプリケーションならびにリアルタイムアプリケーションをサポートする仮想化技術 |

| ・ |

自律的パワー制御機能 |

| ・ |

リアルタイム・ヒューマン・インターアクションを実現する、リソース・マネジメント |

| ・ |

帯域幅を持続する高性能なメモリー・フロー・コントローラ(DMA) |

|