International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART '21), June 21-23, 2021, Online, Germany

Keynote presentation

## Large-scale combinatorial optimization in real-time systems by FPGA-based accelerators for simulated bifurcation

Kosuke TATSUMURA

Chief Research Scientist, Corporate Research and Development Center

Project Manager, New Business Development Office

### **Contents**

- Introduction:

- Combinatorial optimization in real-time systems

- O2 Simulated bifurcation (SB)

- 03 Real-time systems that make optimal responses

- 04 Scaling out Ising machines

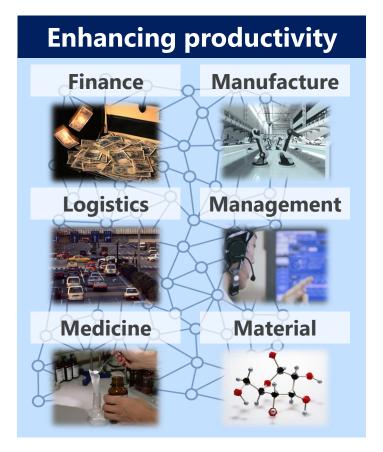

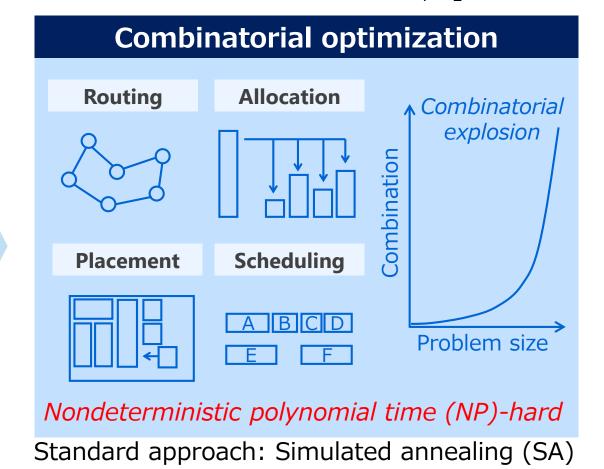

### **Combinatorial optimization problem\***

## **Economically valuable but computationally hard**

\*Find a combination of discrete values,  $(s_1, s_2, ...)$ , that minimizes a cost function of the discrete variables, Cost\_Func $(s_1, s_2, ...)$

### **Ising machines**

## Special-purpose hardware devices for quickly solving combinatorial optimization

D-Wave Sys.\*1 2011-

#### **Quantum Annealer**

HITACHI \*2 2015-

## **CMOS** annealing machine

U-Virginia\*6 2020-

### **Coupled oscillators**

FUJITSU \*3 2016-

### **Digital annealer**

HP/U-Michigan\*7 2020-

#### **Memristor HNN**

NTT/Stanford/U-Tokyo \*4 2016-

**Coherent Ising** machine (CIM)

U-Roma\*5 2019-

**Spatial-photonic Ising machine (SPIM)**

Toshiba\*8 2019-

#### **Simulated bifurcation**

© 2021 Toshiba Corporation

<sup>\*1</sup> https://www.dwavesys.com/d-wave-two-system

<sup>\*2</sup> https://www.hitachi.co.jp/New/cnews/month/2019/02/0219.html

<sup>\*3</sup> https://www.fujitsu.com/global/about/resources/news/press-releases/2018/0515-01.html

<sup>\*4</sup> https://www.ntt.co.jp/news2017/1711e/171120a.html

<sup>\*5</sup> D. Pierangeli, et al., Phys. Rev. Lett. **122**, 213902 (2019).

<sup>\*6</sup> A. Mallick, et al., Nature Communications **11**, 4689 (2020).

<sup>\*7</sup> F. Cai, et al., Nature Electronics 3, 409 (2020).

<sup>\*8</sup> https://www.global.toshiba/ww/technology/corporate/rdc/rd/topics/21/2103-03.html

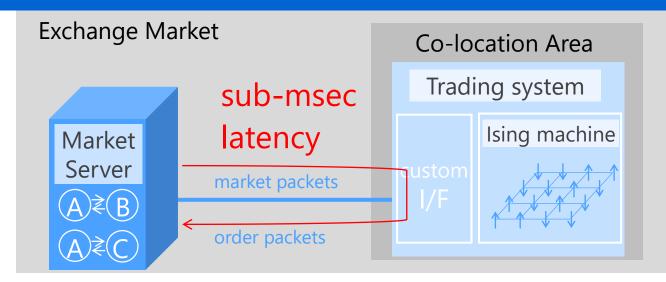

### For real-time systems

# Ising machines may allow those systems to choose the optimal response from among all the candidates -Rational decision-making in real-time systems-

#### Financial transaction system\*1

### Video processing\*2

#### **Swarm robotics**

### Real-time systems:

- -respond to rapid-changing situations with specified time constrains

- -decision making based on a simple conditional judgement (conventional)

The story of the birth of SB, https://www.toshiba-clip.com/en/detail/p=76

## A quantum-inspired algorithm for combinatorial optimization having Plentiful Parallelism

#### **Simulated Bifurcation (SB)**

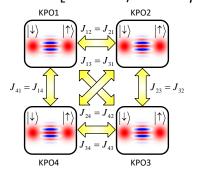

### **Quantum Bifurcation (QB) machine**

a quantum adiabatic optimization method [H. Goto, Sci. Rep **6**, 21686, '16]

### Plentiful parallelism

### Simulated Annealing (SA)

### This talk: Proposal & demonstration

## Real-time systems that make *optimal* responses enabled by FPGA-based SB accelerators

Simulated bifurcation (SB) & FPGA-based accelerators for SB

Real-time systems that make optimal responses:

An ultra-fast financial transaction machine

Scale-out architecture of Ising machines with full connectivity using the high parallelism of SB

### **Contents**

- Introduction:

- O1 Combinatorial optimization in real-time systems

- O2 Simulated bifurcation (SB)

- 03 Real-time systems that make optimal responses

- 04 Scaling out Ising machines

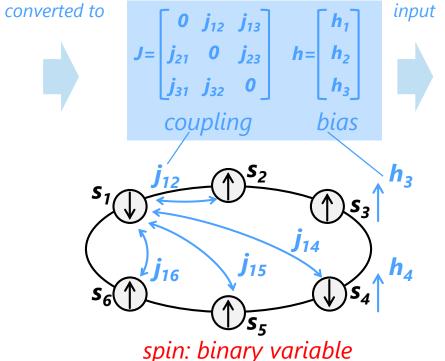

[Andrew Lucas, Frontiers in Physics 2, 5 (2014)] provides Ising formulations for many NP-complete/hard problems, including all of Karp's 21 NP-complete problems

- 1. Any NP problems can be converted to the Ising problem with P-time 2. Ising machine searches for the ground-state of Ising spin model

- Combinatorial optimization

**NP-hard**

Ising problem

NP-hard & NP-complete

Ising machine Special-purpose

search for ground-state *s* minimizing *E*

Ising energy

$$E = -\sum_{ij} j_{ij} s_i s_j + \sum_{i} h_i s_i$$

$$solution$$

$$Spin configuration, S$$

## The story of the birth of SB

## Simulated bifurcation was "discovered" from a quantum computer

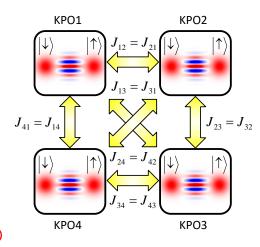

Quantum Bifurcation (QB) machine [H. Goto, Sci. Rep. 2016]

$$H_{q}(t) = \hbar \sum_{i=1}^{N} \left[ \frac{K}{2} (a_{i}^{\dagger 2} a_{i}^{2}) - \frac{p(t)}{2} (a_{i}^{\dagger 2} + a_{i}^{2}) + \Delta (a_{i}^{\dagger} a_{i}) \right] - \hbar \xi_{0} \sum_{i=1}^{N} \sum_{j=1}^{N} J_{i,j} (a_{i}^{\dagger} a_{j}) + \Delta (a_{i}^{\dagger} a_{j}) \right] - \hbar \xi_{0} \sum_{i=1}^{N} \sum_{j=1}^{N} J_{i,j} (a_{i}^{\dagger} a_{j}) + \Delta (a_{i}^{\dagger} a_{j})$$

Classical Bifurcation (CB) machine [H. Goto, Sci. Rep. 2016]

Classicization

$$H_{c}(\mathbf{x}, \mathbf{y}, t) = \sum_{i=1}^{N} \left[ \frac{K}{4} (x_{i}^{2} + y_{i}^{2})^{2} - \frac{p(t)}{2} (x_{i}^{2} - y_{i}^{2}) + \frac{\Delta_{i}}{2} (x_{i}^{2} + y_{i}^{2}) \right] - \frac{\xi_{0}}{2} \sum_{i=1}^{N} \sum_{j=1}^{N} J_{i,j} (x_{i}x_{j} + y_{i}y_{j})$$

↓ Algorithmic twist ↓ for speed-up

## Simulated Bifurcation (SB) algorithm

[Goto, Tatsumura, Dixon, Science Advances 5, eaav2372 (2019)]

There was No guarantee. We found that CB works very well and has an outstanding characteristics, i.e. parallelism.

Based on the quantum adiabatic theorem

#### Science Advances

"Combinatorial optimization by simulating adiabatic bifurcations in nonlinear Hamiltonian systems"

H. Goto et al.

April 19, 2019 Massi

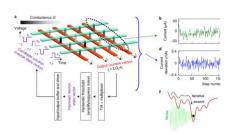

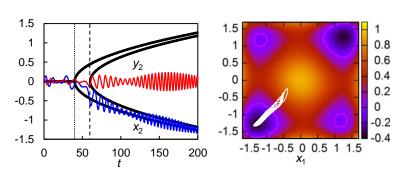

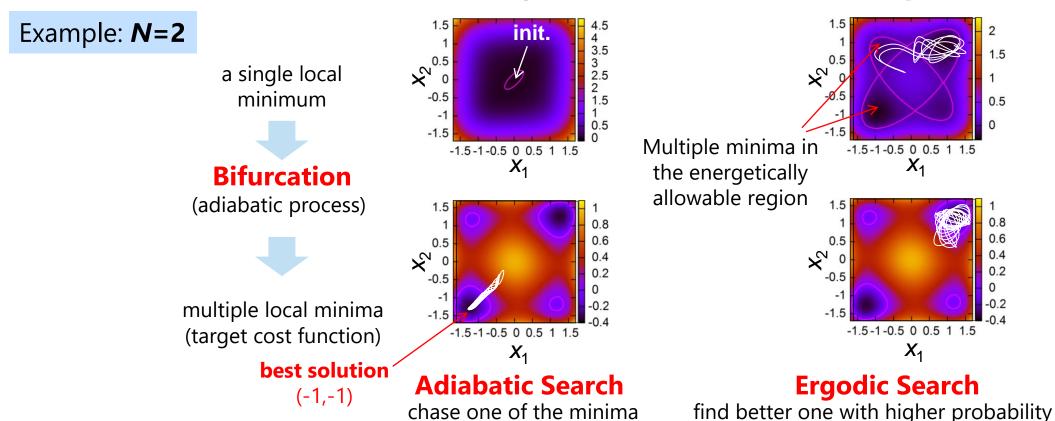

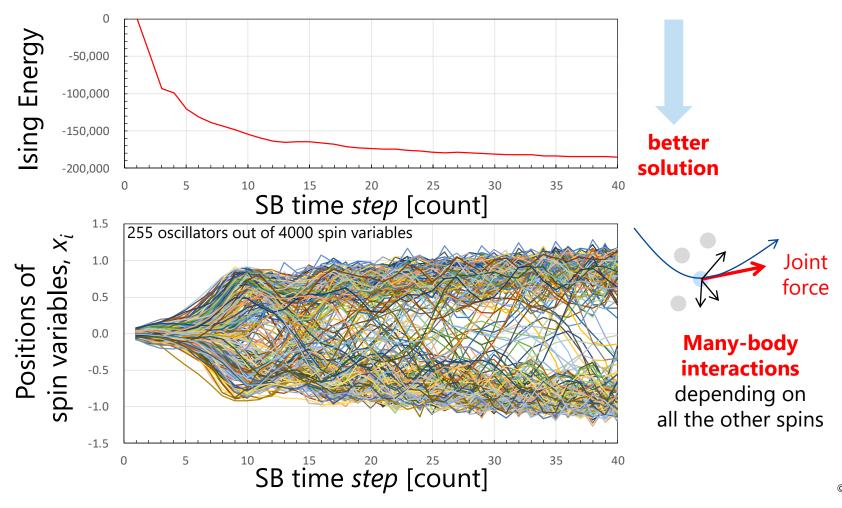

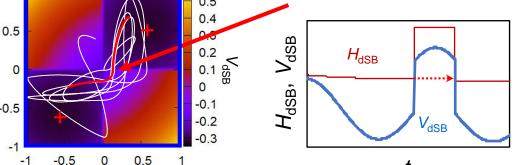

## **How it works: Simulated Bifurcation (SB)**

### N-body system dynamically searches for a good solution

## Movement of the system in N-dimensional space

### If N is large,

find a global minimum (or a local minimum close to the grand-state) from among  $2^N$  local minima

### **How it works: Simulated Bifurcation (SB)**

## Time evolution of N-body system

### Movements of N(=4000) spin-variables as a function of time

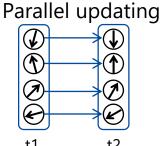

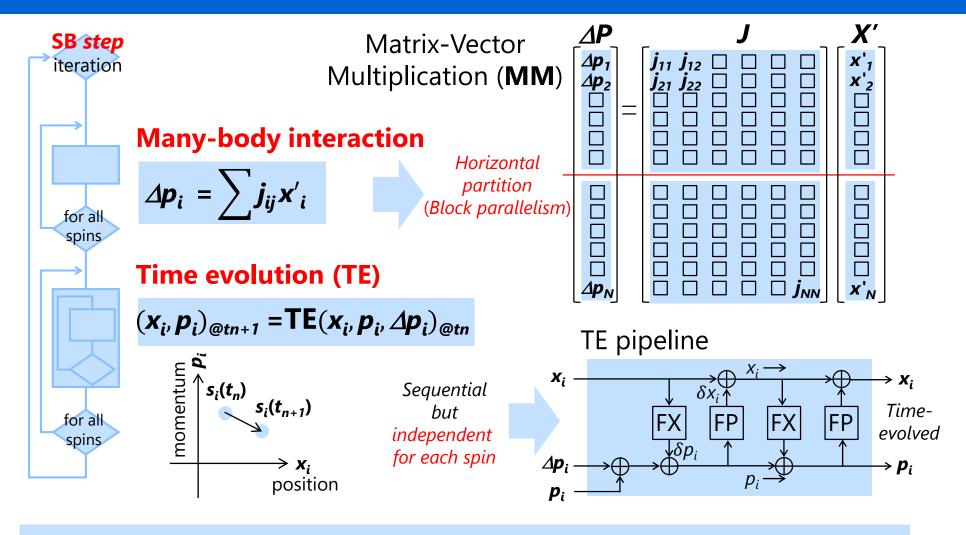

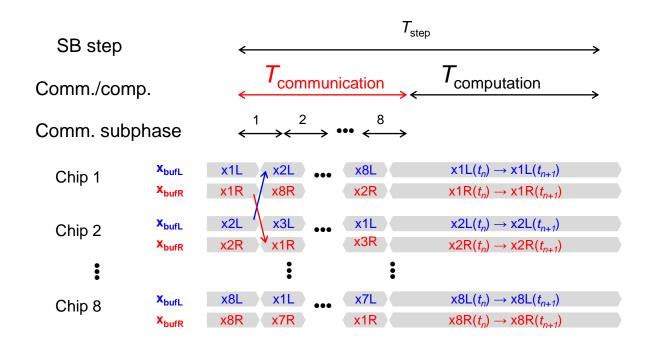

## Algorithm of SB and it's parallelism

## SB step: spin state at $t_{n+1} \leftarrow$ the previous state at $t_n$

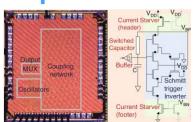

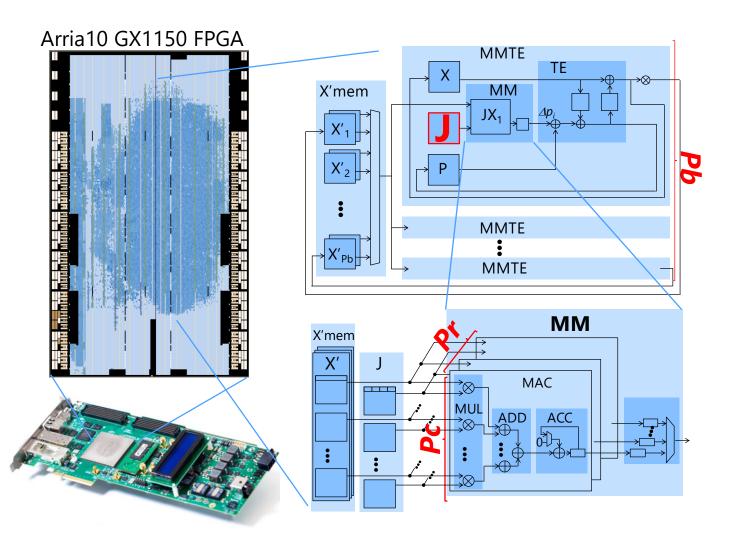

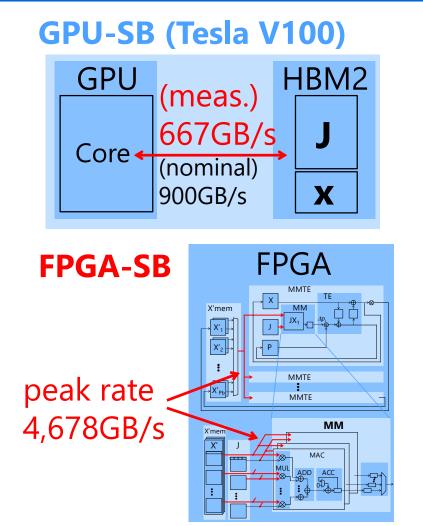

### FPGA-based accelerator for simulated bifurcation

## Large-scale, massively parallel, and high utilization

| Problem            | complete-graph<br>MAX-CUT       |

|--------------------|---------------------------------|

| Machine size       | 4,096-size<br>(on Arria10 FPGA) |

| Architecture       |                                 |

| Pr/Pc/Pb           | 32/32/8                         |

| # of MAC PEs       | 8,192                           |

| Effective activity | 92%                             |

| Resource           |                                 |

| ALM                | 40%                             |

| BRAM               | 56%                             |

| DSP                | 7%                              |

| System Clock       | [MHz]                           |

| Fsys               | 269                             |

@all-to-all-connected

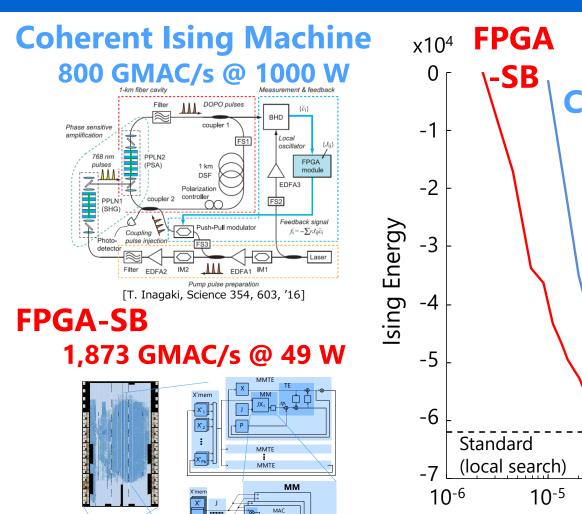

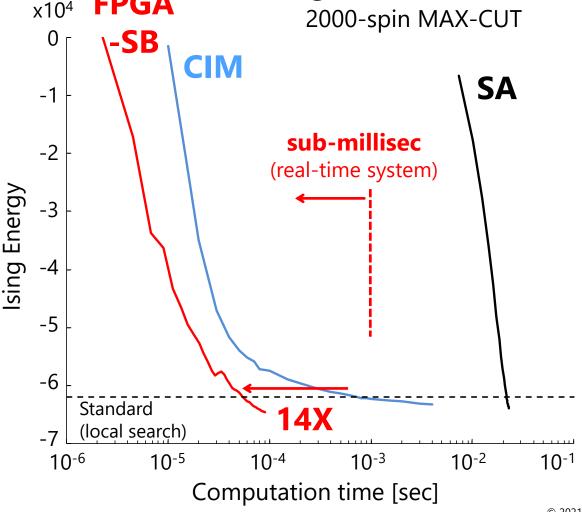

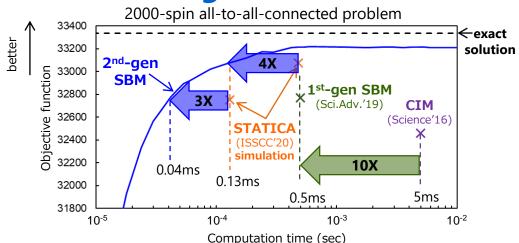

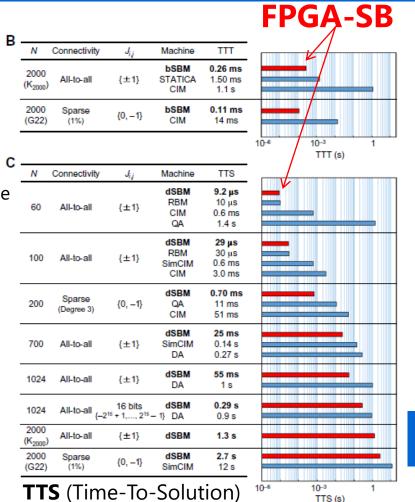

### **Evaluation: FPGA-SB vs. CIM**

## 14X faster, 288X more energy efficient than CIM

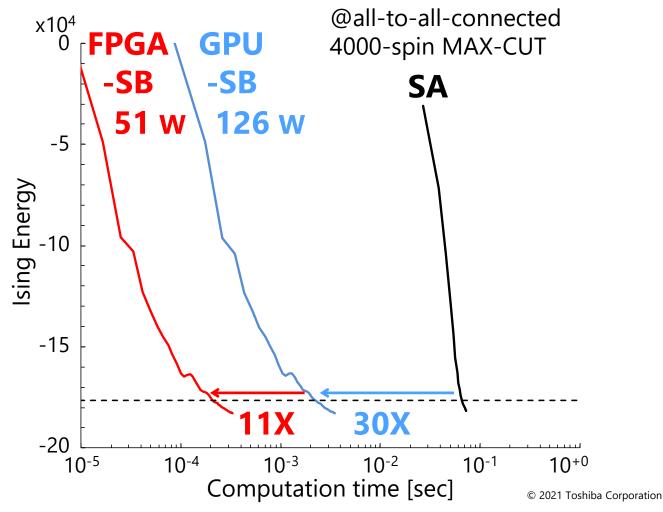

### **Evaluation: FPGA-SB vs. GPU-SB**

## FPGA is computation-bound, GPU memory-bound -11X faster, 26X more energy efficient than GPU-SB

## Why SB is faster than SA

## Maximum computation parallelism: N<sup>2</sup> for SB, N for SA SB can be further accelerated by more parallel computing

#### our best-optimized implementation **Simulated bifurcation (SB)** 800,000 800,000 Parallel updating Simulated bifurcation Simulated annealing N = 16,384**Quality of solution** Cut value **Sut value** HNN HNN 750,000 750,000 828X **Simulated Annealing (SA)** faster Sequential updating bifurcation annealing 700,000 700.000 10<sup>-3</sup> 10<sup>-2</sup> $10^{-4}$ 10-1 40 50 70 80 90 100 Number of steps Time [sec] The amount of computation **Computation time** (The amount of pair interactions evaluated)

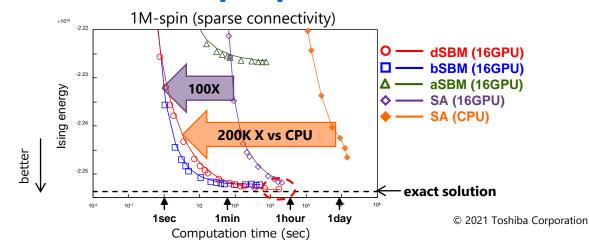

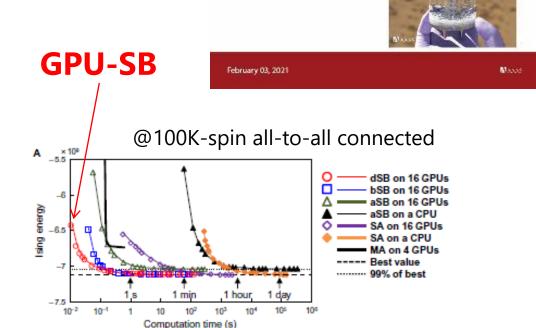

## 2<sup>nd</sup>-gen simulated bifurcation technology (Feb, '21)

Incorporated quasi-quantum effects, got further faster, larger & higher-quality

Improvement of Quality-of-Solution Quasi-quar

$\overset{5}{\mathsf{x}}$

Quasi-quantum tunneling effects

#### Science Advance

\*High-performance combinatorial optimization based on classical mechanics\*

H. Goto et a

February 03, 2021

-

### 10X faster than 1st-gen SB

## Solves 1M-spin problem in 30 min

mechanics"

H. Goto et a

High-performance combinatorial optimization based on classical

Science Advances

## 2<sup>nd</sup>-gen simulated bifurcation technology (Feb, '21)

## Comprehensive comparison with state-of-the-art Ising machines

### **Competitors**

SB: Simulated bifurcation

**QA**: Quantum annealer

**CIM**: Coherent Ising machine

**DA**: Digital annealer

SimCIM: Simulated CIM

**RBM**: Restricted Boltzmann machine

MA: Momentum annealing

## SB technology is competitive

### **Contents**

- Introduction:

- O1 Combinatorial optimization in real-time systems

- 02 Simulated bifurcation (SB)

- Real-time systems that make optimal responses

- 04 Scaling out Ising machines

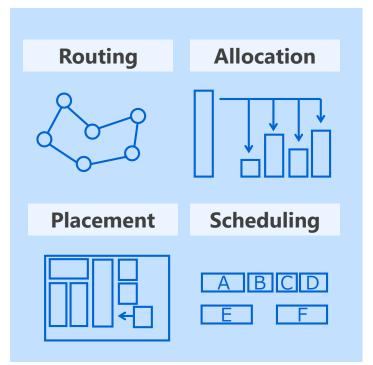

### **FPGA** accelerator for SB: For what?

## Real-time systems that make optimal responses System-wide response time (in sub-ms) is CRITICAL

Ultralow latency

Sub-ms latency has not yet been demonstrated for any Ising machines

Conv.

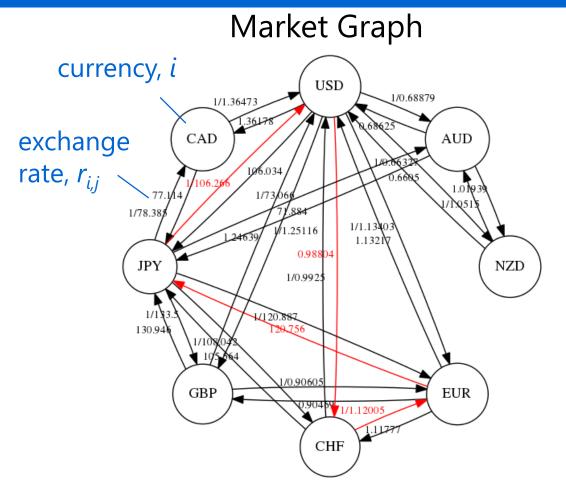

### **Detection of cross-currency arbitrage opportunity**

## Optimal path search in a directed graph -a combinatorial optimization problem-

### **Arbitrage Problem**

find a closed path that maximizes the profit

Cost function

$$Profit = \prod_{i,j \in path} r_{i,j}$$

Constraint

Must be a closed path

### Requirement

find more profitable paths in a shorter time

### Problem formulation: QUBO (Quadratic Unconstrained Binary Optimization)

## QUBO formulation of the arbitrage problem

For each edge,

Decision variable  $b_{i,j}$

Exchange rate  $r_{i,j}$

**Cost function**

**Cost function** (linear)

(high-order polynomial)

$$C' = \prod r_{i,j}^{b_{i,j}} - w_{i,j} = -\log r_{i,j} \longrightarrow C = \sum w_{i,j} b_{i,j}$$

**Penalty function** (quadratic)

$$P = \sum_{i} \sum_{j \neq j'} b_{i,j} \ b_{i,j'} \ + \sum_{j} \sum_{i \neq i'} b_{i,j} \ b_{i',j} \ + \sum_{i} \left( \sum_{j} b_{i,j} - \sum_{j} b_{j,i} \right)^2 + \sum_{i,j} b_{i,j} \ b_{j,i}$$

outflow < 1 outflow = inflow forbids traversing the same edge twice

**Total cost function** (quadratic)

$$C_{tot} = m_c C + m_p P$$

### **Arbitrage problem as a QUBO:**

Optimize the bit configuration  $\{b_{i,j}\}$  to minimize the quadratic cost function  $C_{tot}$  in

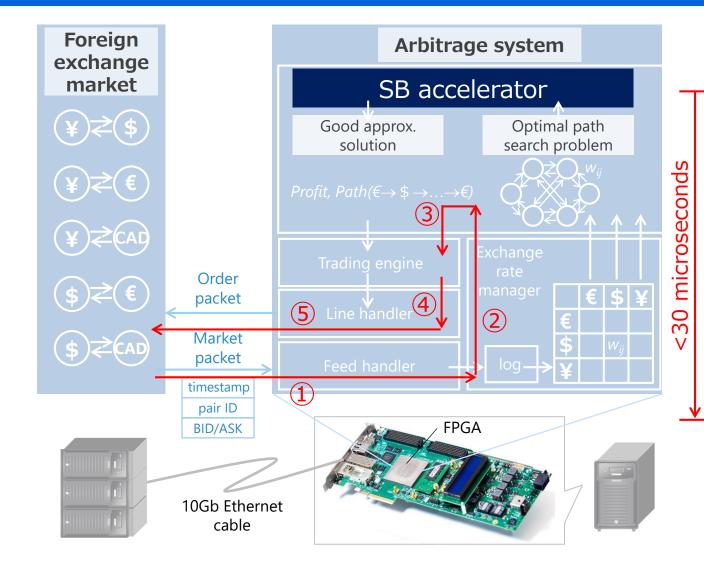

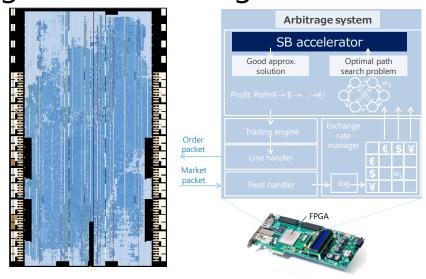

## **System configuration**

## An end-to-end FPGA-based arbitrage system

①Custom I/F (feed handler)

captures market feeds

at unscheduled intervals

**2** Exchange rate manager updates an NxN *wij* matrix, outputs all weights in a single clock

3SB accelerator searches for an optimal path from all possible paths

4 Trading engine prepares order packets

- **SCustom I/F (line handler)** issues the order packets

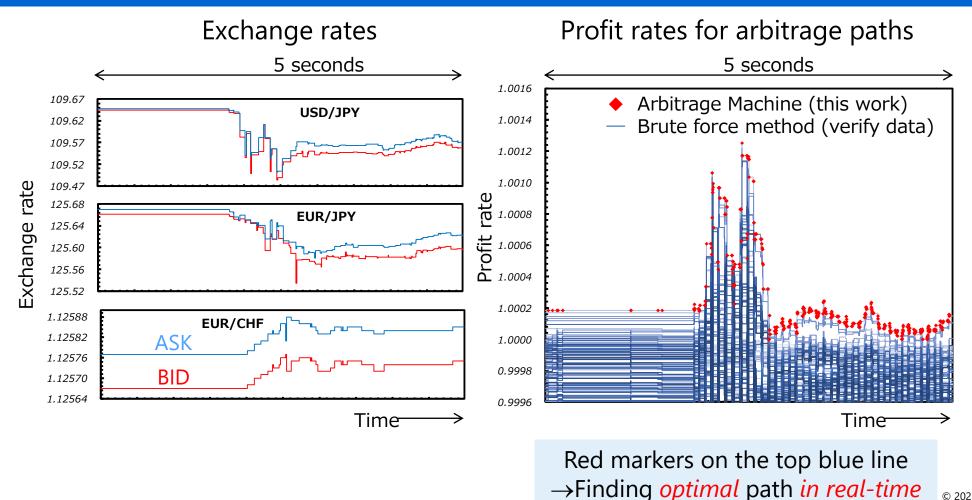

### **Demonstration: How it works**

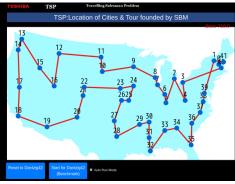

## The system's responses to real market situation on January 2nd, 2019

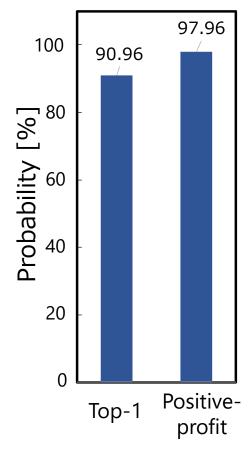

### **Performance: Response time & Accuracy**

## <30us System Latency & 91% Top-1 Probability

### Response time

### 10 milliseconds 1.0014 System-wide response time: 27.5us (on average over 1000 packets) 1.0012 1.0010 Rate 1.0008 Profit 1.0006 1.0004 1.0002 1.0000 9 10 Time [ $x10^{-3}$ sec]

### **Solution accuracy**

In the one-month data, 34,471,865 distinct events, 21.3% (7,355,698) were profitable (at least one path with a profit rate >1.0)

To facilitate the development of innovative real-time systems for everyone

## On-premises ver. of simulated bifurcation machine<sup>TM</sup> (Mar., 2021)

### A look-aside FPGA accelerator for SB C/Python APIs for software engineers

### Reference designs of real-time applications

a user-interactive interface for solving the travelling salesman problem

multi-object tracking by solving the maximum matching problem stream data processing of market graph for finding the diversified portfolio through solving the maximumindependent-set problem

### **Contents**

- Introduction:

- O1 Combinatorial optimization in real-time systems

- 02 Simulated bifurcation (SB)

- 03 Real-time systems that make optimal responses

- O4 Scaling out Ising machines

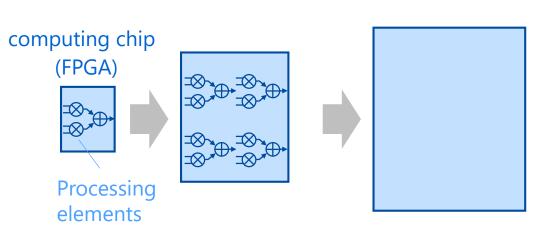

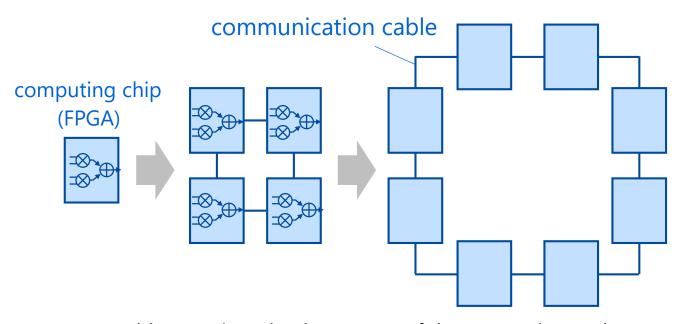

## Enlarging machine size & enhancing processing speeds -Enlarging machine size while keeping computational efficiency-

Single-FPGA accelerator for SB\*1

# of PEs: 8,192 Effective activity factor: 92% Sufficient data supply to PEs Peak rate: 4,678GB/s

On-chip memory/wiring resources

**FPGA** MMTE

The machine size is limited by on-chip memory

### Single-FPGA arbitrage machine\*2

Maximum market graph: Fully-connected 16-asset problems (16 nodes, 256 directed edges)

What can we do if we want to take more assets into account?

### Increasing computing performance and scale

## Two approaches: scale-up and scale-out

Scale-up

making a chip larger (denser)

Pros. Reactively easy to enhance the performance Cons. Need to develop a manufacturing technology

increasing the number of networked chips

Pros. Enables continued enlargement of the computing scale Cons. Need to develop a cluster architecture to avoid performance saturation due to communication overhead

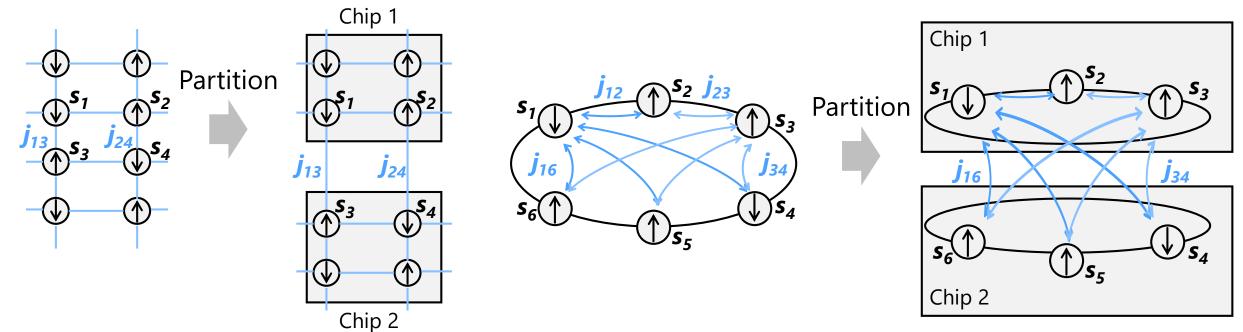

## Partitioning spin networks with local-/full-connectivity

## **Locally-connected network**

More practical value, but more difficult to partition

Issues: Spin-spin couplings over the subsystems must be incorporated Partitioned subsystems also have to evolve in a single time domain →Communication and synchronization can easily degrade the speed performance.

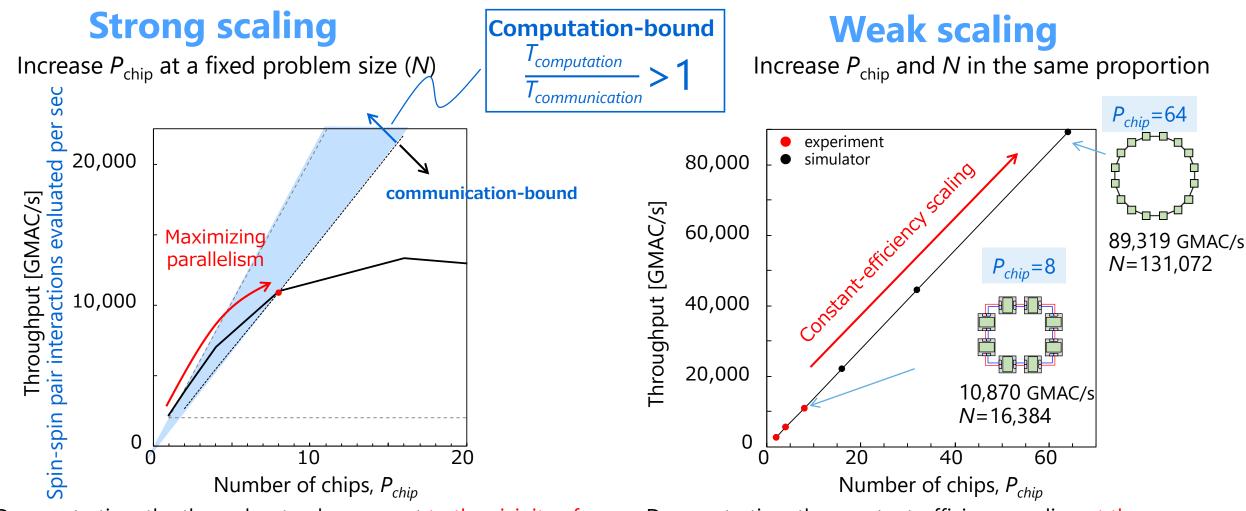

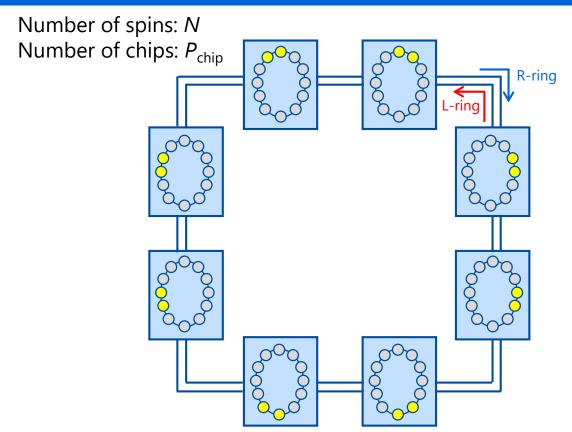

### Scaling out Ising machine with full connectivity

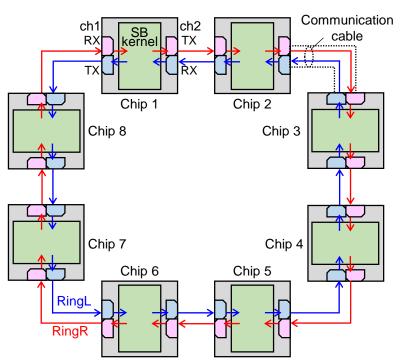

## A multi-chip architecture for SB that enables continued scaling of both machine size and computational throughput

Bidirectional ring-network cluster without any centralized features

Autonomous synchronization mechanism (No clock-sharing, No central-HUB)

nature electronics

$P_{chip}$ =8

All chips are

Time

### Demonstration: Scaling out characteristics

## Constant-efficiency scaling at the maximized computation parallelism

Demonstration: the throughput enhancement to the vicinity of an ideal upper limit determined by *N* and communication technology

Demonstration: the constant-efficiency scaling at the maximized computation parallelism (at the strong scaling limit)

### A multi-chip architecture for simulated bifurcation

## Partitioned SB algorithm that can be executed simultaneously on multiple chips

Each chip (spin subsystem) is responsible for  $N/P_{\rm chip}$  spins Each chip needs all the spin information to update the  $N/P_{\rm chip}$  spins (all-to-all connectivity)

#### Communication phase

- -Share all the spin information

- -Repeating exchange processes of spins btw neighboring chips

Computation phase -compute the time-evolved state in a chip-parallel fashion

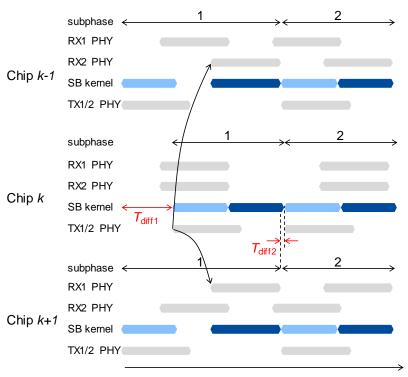

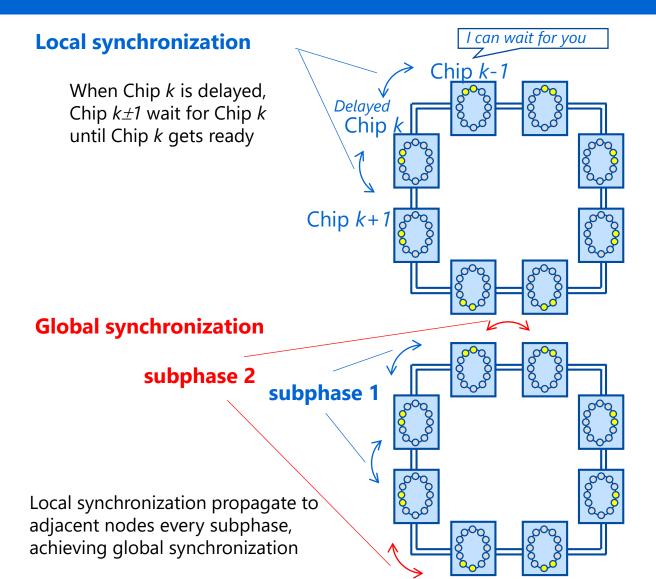

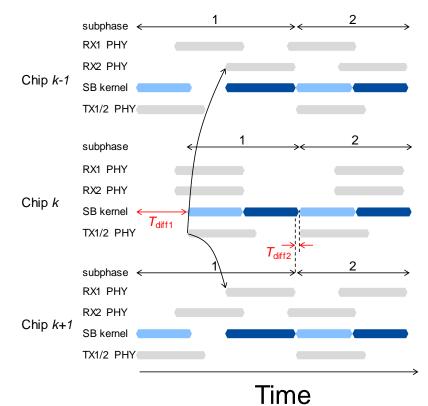

### A multi-chip architecture for simulated bifurcation

### **Autonomous synchronization mechanism**

### Autonomous synchronization mechanism

Global synchronization without a centralized control node (a chokepoint)

→ Good scalability of the processing speed

### **Conclusions**

## FPGA-based accelerators for simulated bifurcation that enables large-scale combinatorial optimization in real-time systems

## **Simulated bifurcation (SB):**

a quantum-inspired algorithm having plentiful parallelism

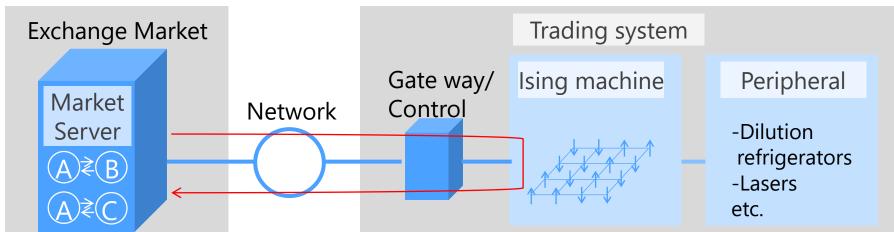

### **FPGA-based accelerators for SB:**

massively-parallel, fully-customized circuit architecture very practical (no refrigerator, no laser, but in FPGA) can be scaled out with an autonomously-synchronizable multi-chip architecture

## Real-time systems that make optimal responses

an example: an end-to-end cross-currency arbitrage system with <30us system latency & 91% top-1 probability

### **Future outlook**

## Toward creating various innovative real-time systems

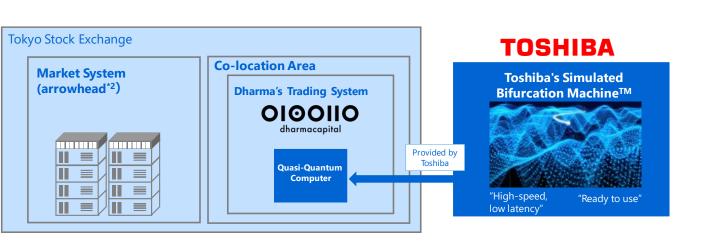

[On-going] Testing high-frequency trading systems using SB accelerators in the Tokyo stock exchange

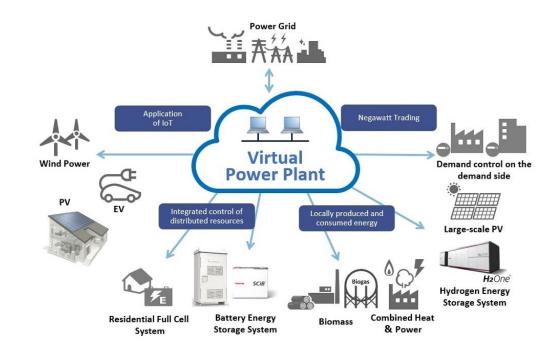

[Future] High-speed dynamic pricing systems applicable to virtual power plant

https://www.global.toshiba/ww/technology/corporate/rdc/rd/topics/21/2105-01.html

https://www.toshiba-clip.com/en/detail/p=228

### References: Simulated Bifurcation Machine<sup>TM</sup>

#### [Official web site]

Simulated Bifurcation Machine™

https://www.toshiba-sol.co.jp/en/pro/sbm/index.htm

#### [Journal papers/Peer-reviewed conference papers/Toshiba's Press Release]

[1] The story of the birth of simulated bifurcation machine  $^{\text{TM}}$

https://www.toshiba-clip.com/en/detail/p=76

[2] 1st Announcement of simulated bifurcation machine™

H. Goto *et al.*, "Combinatorial optimization by simulating adiabatic bifurcations in nonlinear Hamiltonian systems", *Science Advances* **5**, eaav2372 (2019).

https://doi.org/10.1126/sciadv.aav2372

Toshiba's Breakthrough Algorithm Realizes World's Fastest, Largest-scale Combinatorial Optimization <a href="https://www.toshiba.co.jp/rdc/rd/detail-e/e1904\_01.html">https://www.toshiba.co.jp/rdc/rd/detail-e/e1904\_01.html</a>

[3] 2-gen simulated bifurcation machine™

H. Goto *et al.*, "High-performance combinatorial optimization based on classical mechanics", *Science Advances* **7**, eabe7953 (2021).

https://doi.org//10.1126/sciadv.abe7953

Toshiba's New Algorithms Quickly Deliver Highly Accurate Solutions to Complex Problems https://www.toshiba.co.jp/rdc/rd/detail\_e/e2102\_01.html

[4] Custom accelerator

K. Tatsumura *et al.*, "FPGA-Based Simulated Bifurcation Machine", *IEEE Int'l Conf. on Field-Programmable Logic and Applications* (FPL), 59-66 (2019).

https://doi.org/10.1109/FPL.2019.00019

Toshiba Develops a Dedicated Massively Parallel Processing Circuit for Simulated Bifurcation Algorithms <a href="https://www.toshiba.co.jp/rdc/rd/detail-e/e1909-03.html">https://www.toshiba.co.jp/rdc/rd/detail-e/e1909-03.html</a>

[5] PoC for ultra-fast financial transaction machine

K. Tatsumura *et al.*, "A Currency Arbitrage Machine Based on the Simulated Bifurcation Algorithm for Ultrafast Detection of Optimal Opportunity", *IEEE Int'l Symp. on Circuits and Systems* (ISCAS), 1-5 (2020). <a href="https://doi.org/10.1109/ISCAS45731.2020.9181114">https://doi.org/10.1109/ISCAS45731.2020.9181114</a>

M. Yamasaki *et al.*, "Live Demonstration: Capturing Short-Lived Currency Arbitrage Opportunities with a Simulated Bifurcation Algorithm-Based Trading System", *IEEE Int'l Symp. on Circuits and Systems* (ISCAS), 1-1 (2020).

https://doi.org/10.1109/ISCAS45731.2020.9180679

Toshiba Develops Proof-of-concept Device for Ultra-high-speed Financial Transaction Machine with Simulated Bifurcation Algorithm

https://www.toshiba.co.jp/rdc/rd/detail\_e/e1910\_02.html

[6] Scaling out Ising machines

K. Tatsumura *et al.*, "Scaling-out Ising machines using a multi-chip architecture for simulated bifurcation", *Nature Electronics* **4**, 208–217 (2021).

https://doi.org/10.1038/s41928-021-00546-4

Also see BEHIND THE PAPER: <a href="https://go.nature.com/2MuGe21">https://go.nature.com/2MuGe21</a>

Cutting-edge Scale-Out Technology from Toshiba will Take Fintech and Logistics to New Level <a href="https://www.toshiba.co.jp/rdc/rd/detail">https://www.toshiba.co.jp/rdc/rd/detail</a> e/e2103 01.html

[7] On-premises version of Simulated Bifurcation Machine™

Toshiba Offers On-premises Simulated Bifurcation Machine™ for Market Trials in Japan <a href="https://www.global.toshiba/ww/technology/corporate/rdc/rd/topics/21/2103-03.html">https://www.global.toshiba/ww/technology/corporate/rdc/rd/topics/21/2103-03.html</a>

[8] Testing SB-based financial transaction machines in the Tokyo stock exchange Toshiba and Dharma Capital's Joint Experiment in Financial Markets to Verify the Effectiveness of a Quasi-Quantum Computer When Applied to High Frequency Trading <a href="https://www.global.toshiba/ww/technology/corporate/rdc/rd/topics/21/2105-01.html">https://www.global.toshiba/ww/technology/corporate/rdc/rd/topics/21/2105-01.html</a>

[9] Real-time systems that make optimal responses

K. Tatsumura *et al.*, "Large-scale combinatorial optimization in real-time systems by FPGA-based accelerators for simulated bifurcation", *ACM Int'l Symp. on Highly Efficient Accelerators and Reconfigurable Technologies* (HEART), 1-6 (2021).

https://doi.org/10.1145/3468044.3468045

#### [News Media]

[1] IEEE Spectrum (Dec, '19)

Toshiba's Optimization Algorithm Sets Speed Record for Solving Combinatorial Problems <a href="https://spectrum.ieee.org/tech-talk/computing/software/toshiba--optimization-algorithm-speed-record-combinatorial-problems#.XkHhXCOP1GQ.email">https://spectrum.ieee.org/tech-talk/computing/software/toshiba--optimization-algorithm-speed-record-combinatorial-problems#.XkHhXCOP1GQ.email</a>

[2]Analytics India Magazine (Dec, '19)

Top 5 Algorithm Breakthroughs In 2019

https://analyticsindiamag.com/top-5-algorithm-breakthroughs-in-2019/

[3] COMMUNICATIONs of the ACM (May, '21) Quantum Simulator Beats Quantum Hardware

https://cacm.acm.org/news/252584-quantum-simulator-beats-quantum-hardware/fulltext

[4] Risk.net (Jun, '21) Quantum kit offers HFTs '100-fold' speed boost

© 2021 Toshiba Corporation