# 薄膜 HfO。を用いた強誘電体トンネル接合メモリー

Ferroelectric Tunnel Junction Memory with HfO<sub>2</sub> Thin Film

藤井 章輔 齋藤 真澄

■ FUJII Shosuke

■ SAITOH Masumi

薄膜の強誘電体を利用したトンネル接合 (FTJ: Ferroelectric Tunnel Junction) メモリーは、次世代の不揮発性メモリーとして研究が進められている。しかし、一般に用いられているペロブスカイト型の強誘電体材料は、CMOS (相補型金属酸化膜半導体) 製造プロセスに組み込むことが難しいという課題があった。

東芝は、CMOS製造プロセスに組み込むことが容易な強誘電体材料の酸化ハフニウム ( $HfO_2$ ) 膜を適用したFTJ ( $HfO_2$  FTJ) メモリーを試作し、世界に先駆けて (注1)  $HfO_2$  FTJ メモリーによるメモリー動作を実証するとともに、低電流動作及び電圧駆動が可能で、整流特性を持つなど、近年注目されている様々な新規不揮発性メモリーよりも優れた特性を持つことを確認した。また、動作電圧に対する設計指針を構築し、動作電圧を低減することができた。

Research is being pursued on thin-film ferroelectric tunnel junction (FTJ) memory as a next-generation nonvolatile memory. One issue to be solved in this area is that the perovskite type ferroelectric materials that are conventionally used are difficult to incorporate into the process of complementary metal-oxide semiconductor (CMOS) production.

As a solution to this issue, Toshiba has developed a hafnium oxide  $(HfO_2)$  FTJ memory with a  $HfO_2$  film that is easy to incorporate into the CMOS process as a ferroelectric material, and demonstrated memory operation using a prototype of the  $HfO_2$  FTJ memory for the first time in the world. We have confirmed that the characteristics of this memory, including its low operating current, voltage-driven switching, and intrinsic diode property, are superior to those of other nonvolatile memories. In addition, we have created design guidelines for the operating voltage and have been able to reduce the operating voltage to below that of the prototype.

#### 1 まえがき

強誘電体を利用した不揮発性メモリーは、FeRAM (Ferroelectric RAM) として知られ、既に実用化されている技術である。しかし、FeRAMでは、データの読み出し時にデータを破壊してしまうことや、CMOS製造プロセスでの作製が困難なペロブスカイト型の強誘電材料を用いることなどが課題となっていた。

近年,この強誘電体メモリーの分野において二つの大きな 進展が見られた。

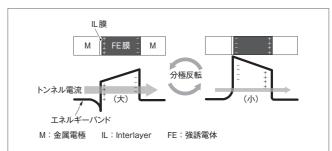

一つは、データの非破壊読み出しが可能なFTJメモリーの動作実証である。FTJメモリーは、厚さが10 nm程度以下でトンネル電流が観測できるくらい薄い強誘電体膜を、導電性の金属電極で挟んだ構造を持つ(図1)。FTJメモリーでは、強誘電体膜と金属電極の界面に形成した界面層や金属電極の有限な電荷遮蔽長により、強誘電体膜の分極方向に依存して電子のトンネル障壁が変化する<sup>(2)</sup>。このため、分極方向に応じて金属電極から注入されるトンネル電流が変化するので、これ

図1. FTJメモリーの動作原理 — 強誘電体の分極反転により、金属電極から注入される電子のトンネル障壁が変調される。そのため、分極方向に応じたトンネル電流値の変化が観測される。

Schematic diagram of structure and operating mechanism of FTJ memory  $% \left( 1\right) =\left( 1\right) \left( 1\right$

を利用してデータを記憶する。FTJメモリーのコンセプトは、1970年代に既に提案されていたが、薄膜強誘電体の形成などに技術的な困難があり、実際にFTJメモリーのメモリー動作が実証されたのは2009年になってからである<sup>(3)</sup>。

もう一つの進展は、先端CMOS製造プロセスで既に導入されている $HfO_2$ 膜において、強誘電性が確認されたことである<sup>(4)</sup>。 $HfO_2$ 膜は、従来のペロブスカイト型の強誘電体材料とは異なる二元系の材料であり、扱いやすい。 $HfO_2$ 膜中では、酸素の動きにより強誘電性が発現することが第一原理計算により明

<sup>(</sup>注1) 2016年6月に、2016 IEEE symposium on VLSI technologyで 発表<sup>(1)</sup>、当社調べ。

らかになっている<sup>(1)</sup>。

これらの進展により、データの非破壊読み出しが可能で、かつCMOS製造プロセスとの親和性が高い材料だけで構成された新規不揮発性メモリーであるHfO<sub>2</sub> FTJメモリーの実現が期待されていた。東芝は、世界に先駆けてこのHfO<sub>2</sub> FTJメモリーのメモリー動作を実証した。ここでは、その概要と結果について述べる。

## 2 HfO<sub>2</sub> FTJメモリーの構造と強誘電体特性

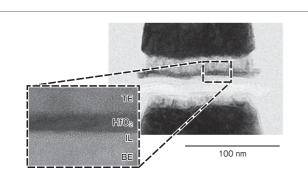

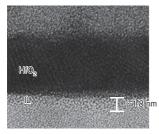

今回試作した $HfO_2$  FTJメモリーの透過型電子顕微鏡 (TEM) 像を**図2**に示す。最小で $100 \times 100$  nmの素子を作製した。作製プロセスは、次のとおりである。まず、下部金属電極 (BE: Bottom Electrode) と常誘電体のIL (Interlayer) 膜を形成後、シリコン (Si) を添加した $HfO_2$  膜をALD (Atomic Layer Deposition) 法により成膜した。次に、上部金属電極 (TE: Top Electrode) を成膜し、アニール処理を行った。TE形成後のアニール処理により、 $HfO_2$  膜は結晶化して強誘電性を示す斜方晶となる。

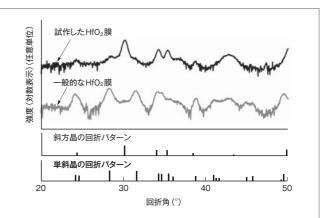

アニール処理後の $HfO_2$ 膜のX線回折測定結果を $\mathbf{Z}$ るに示す。一般に知られている $HfO_2$ 膜は単斜晶であり、回折角が $30^\circ$ 前後の位置に二つの回折ピークが見られるのが特徴である。単斜晶の $HfO_2$ 膜は、反転対称性を持つ結晶構造のため強誘電性を示さない。一方で、TE形成後にアニール処理プロセスを経た $HfO_2$ 膜は、 $30^\circ$ 付近に一つの回折ピークを持つ斜方晶となる。斜方晶の $HfO_2$ 膜は、反転対称性を持たない結晶構造のため、強誘電性を発現し得る。

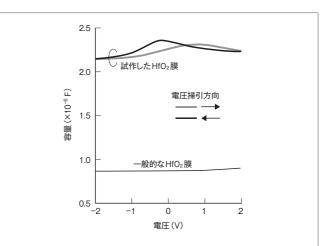

強誘電性の確認には容量-電圧測定を用いた。強誘電体膜の容量-電圧特性では、分極反転に対応するピークが観測される。また、ピークの現れる位置が電圧の掃引方向によって異なり、ヒステリシスを持つことが知られている。 $\mathbf{図4}$ は、 $\mathbf{HfO}_2$ 膜の容量-電圧特性である。一般的な単斜晶の $\mathbf{HfO}_2$ 膜とは異な

**図2. 試作したHfO<sub>2</sub> FTJメモリーの断面TEM像** — 試作したHfO<sub>2</sub> FTJメモリーは、上下の金属電極TEとBEでHfO<sub>2</sub> 膜とIL 膜を挟んだ構造である。

Cross-sectional transmission electron microscope (TEM) image of prototype  $HfO_2\,FTJ$  memory

図3.  $HfO_2$ 膜のX線回折パターンの比較 — 一般的な単斜晶の $HfO_2$ 膜と異なり、試作した $HfO_2$ 膜の回折パターンは、 $30^\circ$  付近に一つのピークを持つ。これは、斜方晶の $HfO_2$ 膜で想定される回折パターンとよく一致する。Comparison of X-ray diffraction patterns of conventional and prototype  $HfO_2$  films

図4.  $HfO_2$ 膜の容量 - 電圧特性 — 試作した $HfO_2$  FTJメモリーの $HfO_2$  膜では、容量 - 電圧特性にピークとヒステリシスが観測され、強誘電性を持つことが確認できた。

Comparison of capacitance-voltage characteristics of conventional and prototype  $HfO_2$  films

り、試作した $HfO_2$ 膜ではヒステリシスが観測され、強誘電性を持つことが確認できた。

#### 3 HfO<sub>2</sub> FTJメモリーの特性

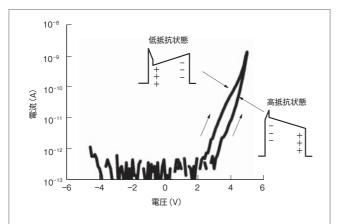

試作したHfO<sub>2</sub> FTJメモリーの電流-電圧特性を図5に示す。TEに正の電圧を印加すると、素子が高抵抗状態から低抵抗状態へ遷移する。これは、電圧印加中にHfO<sub>2</sub> 膜中で分極反転が起こり、抵抗が変化したと考えられる。図5には、低抵抗状態と高抵抗状態のエネルギーバンドダイヤグラムも同時に示してある。低抵抗状態では電子のトンネル障壁が低く、素子中を電子が通過しやすい。このとき、低抵抗状態の素子に対して負の電圧を印加すれば、逆方向への分極反転が起こ

図5. 試作したHfO<sub>2</sub> FTJメモリーの電流-電圧特性 — 正の電圧を印加すると高抵抗状態から低抵抗状態に、負の電圧を印加すると低抵抗状態から高抵抗状態に遷移し、HfO<sub>2</sub>膜中の分極反転により抵抗変化が起こっていることが確認できた。

Current-voltage characteristics of prototype HfO<sub>2</sub> FTJ memory

り、電子のトンネル障壁の高い高抵抗状態へ戻る。これらの結果から、 $HfO_2$ 膜中の分極反転により抵抗変化が起こっていることが確認できた。

HfO<sub>2</sub> FTJメモリーの動作時の最大電流はnA程度であった。これは、近年注目されているReRAM (Resistive RAM)、PCM (Phase Change Memory)、MRAM (Magnetic RAM) などの新規メモリーと比較して小さい。この特徴により、メモリーの低消費電力化が期待できる。また、正電圧方向の電流値の方が負電圧方向の電流値よりも大きく、整流特性を持つことも分かった。整流特性は、大容量化が可能なクロスポイント型のメモリーアレイを実現する上で重要な特性となる。クロスポイント型のメモリーアレイでは、迷走電流と呼ばれる電流ノイズが問題となるが、整流特性により迷走電流を抑制できることが知られている。このことから、HfO<sub>2</sub> FTJメモリーは、低消費電力で大容量のメモリーアレイを実現する可能性を持

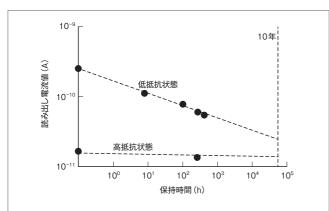

図6. 試作したHfO<sub>2</sub> FTJメモリーのデータ保持性能 — 実測値からの 外挿により、10年間のデータ保持後でも低抵抗状態と高抵抗状態が識別 可能であることが分かった。

Data retention performance of prototype HfO<sub>2</sub> FTJ memory

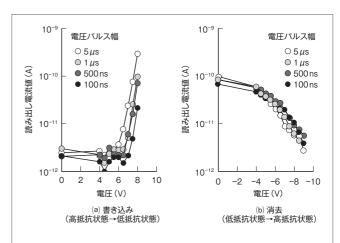

図7. 電圧パルスによる書き込み・消去動作 — 電圧パルス幅が100 ns でもデータの書き込み・消去が可能なことが分かった。

Characteristics of write and erase operations of prototype HfO<sub>2</sub> FTJ memory using voltage pulses

つことが明らかになった。

データ保持特性を図6に示す。高抵抗状態の読み出し電流値は、保持時間に対してほぼ一定で安定なのに対し、低抵抗状態の電流値は、徐々に低下する。データ保持期間を10年まで外挿しても、低抵抗状態と高抵抗状態は識別可能と見積もられ、良好な保持特性を持つことが分かった。

低抵抗状態の読み出し電流が低下する原因としては、データ保持中に、電子が $HfO_2$ 膜中に流入して捕獲されるためと推測している。したがって、低抵抗状態の保持特性をより安定化させるには、欠陥量が少なく電子を捕獲しにくい $HfO_2$ 膜の開発が有効と考えられる。

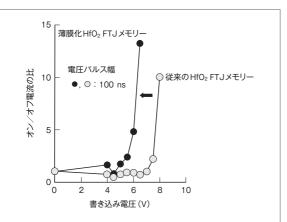

電圧パルスによるスイッチ特性を**図7**に示す。電圧パルス幅が 100 ns でも動作し、従来のNAND型メモリーの動作速度と比較して高速な動作が可能なことが確認できた。一方、動作電圧は $7\sim8$  Vで、ほかの新規メモリーに比べて高く、低動作電圧化が課題であることが分かった。

# 4 HfO<sub>2</sub> FTJメモリーの低動作電圧化

動作電圧の低減には、強誘電体膜の薄膜化が有効な手段である。強誘電体膜の分極反転は、ある一定のしきい値電界(抗電界)より大きい電界を印加することで引き起こされる。したがって、強誘電体膜を薄膜化すれば、より低い電圧で抗電界以上の電界が印加され、分極反転を引き起こすことができる。しかし一方で、強誘電体膜だけを薄膜化すると、分極電荷自身によって強誘電体膜中に形成される電界(減分極電界:Depolarization Field) $E_{\rm dep}$ が増加することが予想される。 $E_{\rm dep}$ は、分極状態を不安定化させるため、これが増加することは好ましくない。 $E_{\rm dep}$ は電磁気学によれば式(1)のように表される

$$E_{\rm dep} = \frac{P}{\varepsilon_{\rm FE}} \left( 1 + \frac{\varepsilon_{\rm IL} t_{\rm FE}}{\varepsilon_{\rm FE} t_{\rm IL}} \right)^{-1} \tag{1}$$

ここで、Pは強誘電体膜の分極量、 $t_{\rm FE}$ 、 $\varepsilon_{\rm FE}$ は強誘電体膜の膜厚と誘電率、そして $t_{\rm IL}$ 、 $\varepsilon_{\rm IL}$ は IL 膜の膜厚と誘電率である。式(1)によれば、強誘電体の ${\rm HfO_2}$ 膜だけを薄膜化すると $E_{\rm dep}$ が増加し、分極状態が不安定になる。そこで、 $E_{\rm dep}$ を低く保ち、安定な分極状態を維持するには、 ${\rm HfO_2}$ 膜の薄膜化と同時に IL 膜も薄膜化し、 $t_{\rm FE}$ と $t_{\rm IL}$ の比、すなわち $t_{\rm FE}/t_{\rm IL}$ を一定に保つのが重要なことを見いだした。

この設計指針に従って、薄膜化 $HfO_2$  FTJメモリーを作製し、動作電圧の低減を試みた。薄膜化 $HfO_2$  FTJメモリーのTEM像を**図8**に示す。従来の $HfO_2$  FTJメモリーに比べて、 $HfO_2$  膜、IL 膜の両方が薄くなっていることが分かる。薄膜化 $HfO_2$  FTJメモリーの電圧パルスによるスイッチ特性を**図9**に示す。 $HfO_2$  膜及びIL 膜の薄膜化により、従来と比較して動作電圧を2 V 程度低減できた。この結果により、今回構築し

(a) 従来のHfO<sub>2</sub> FTJメモリー

(b) 薄膜化HfO<sub>2</sub> FTJメモリー

図8. 従来と薄膜化 $HfO_2$  FTJメモリーの断面 TEM 像 — 薄膜化 $HfO_2$  FTJメモリーにおいて、 $HfO_2$  膜だけでなくIL 膜も1.8 nmから0.8 nmへ 薄膜化していることが分かる。

Cross-sectional TEM images of conventional and thin-film  $HfO_2\,FTJ$  memories

図9. 従来と薄膜化 $HfO_2$  FTJメモリーの電圧パルスによる書き込み特性の比較 — 薄膜化 $HfO_2$  FTJメモリーにおいて、従来よりも2 V 程度書き込み電圧が低減していることが分かる。

Comparison of write characteristics of conventional and thin-film  $HfO_2\ FTJ$  memories using voltage pulses

た、低動作電圧化に対する設計指針の有効性が確認できた。 この設計指針に従えば、 $HfO_2$ 膜、IL膜両方の精密な制御に より、更なる低動作電圧化が期待できる。

## 5 あとがき

当社は、 $HfO_2$  FTJメモリーのメモリー動作を世界に先駆けて実証した。また、低電流動作、電圧駆動、整流特性などの特性を持つことを明らかにし、大容量化、低消費電力化に適したメモリーであることを示した。更に、課題であった動作電圧の低減については設計指針を構築し、 $HfO_2$  膜及びIL 膜の薄膜化により 2 V 程度の動作電圧の低減に成功した。

当社がHfO<sub>2</sub> FTJメモリーのメモリー動作を実証して以降,世界で同様の構造を用いたFTJメモリーの報告が相次いでなされている<sup>(5). (6)</sup>。将来の不揮発性メモリーをいち早く実現できるように、今後も、更に研究開発を進めていく。

### 文 献

- (1) Fujii, S. et al. "First demonstration and performance improvement of ferroelectric HfO<sub>2</sub>-based resistive switch with low operation current and intrinsic diode property". 2016 IEEE symposium on VLSI technology Digest of Technical Papers. Honolulu, HI, 2016-06, IEEE. 2016, p.148-149.

- Kohlstedt, H. et al. Theoretical current-voltage characteristics of ferroelectric tunnel junctions. Phys. Rev. B, 2005, 72, 12, p.125341.1-125341.10.

- Garcia, V. et al. Giant tunnel electroresistance for non-destructive readout of ferroelectric states. Nature, 2009, 460, 7251, p.81 - 84.

- (4) Böscke, T. S. et al. Ferroelectricity in hafnium oxide thin films. Appl. Phys. Lett. 2011, 99, 10, p.102903-1-102903-3.

- (5) Tian, X. et al. "Tunneling Electro-resistance Effect in Ultra-thin Ferroelectric HfO<sub>2</sub> Junctions". 2016 International Conference on Solid State Devices and Materials. Tsukuba, 2016-09, Jpn. Soc. Appl. Phys. 2016 p. 625 - 626

- (6) Ambriz-Vargas, F. et al. Tunneling electroresistance effect in a Pt/  $Hf_{0.5}Zr_{0.5}O_2/Pt$  structure. Appl. Phys. Lett. 2017, 110, 9, p.093106-1 093106-5.

藤井 章輔 FUJII Shosuke 技術統括部 研究開発センター LSI 基盤技術ラボラトリー 応用物理学会会員 Advanced LSI Technology Lab.

齋藤 真澄 SAITOH Masumi, Ph.D. 技術統括部 研究開発センター LSI 基盤技術ラボラトリー 博士 (工学) IEEE・応用物理学会会員 Advanced LSI Technology Lab.