# TSV技術を用いた世界初の16段積層 NAND型フラッシュメモリパッケージ

World's First 16-Die Stacked NAND Flash Memory Package Fabricated Using TSV Technology

松寺 克樹 河崎 一茂

■ MATSUDERA Katsuki

■KAWASAKI Kazushige

近年NAND型フラッシュメモリは,ノートPC (パソコン)や,携帯電話,タブレットといった各種モバイル機器をはじめとして,ハイエンドサーバやデータセンターに用いられるSSD (ソリッドステートドライブ)など,様々なアプリケーションで使用されている。 応用分野の拡大に伴い,いっそうの高速化,低消費電力化,及び大容量化が求められている。

このようなアプリケーションからの要求に応えるため、東芝は、NAND型フラッシュメモリのパッケージングに、チップ内を 貫通する電極で配線するTSV (Through Silicon Via) 技術を適用した。TSV技術を適用した16段積層NAND型フラッシュメモリを世界で初めて<sup>(注1)</sup>開発し、従来のワイヤボンディング方式に比べて、データ転送速度の2倍以上の向上と約50% の消費電力削減を達成し、2015年8月に発表した。更なる大容量化を目指して、32段の積層や、3次元フラッシュメモリ BiCS FLASHにTSV技術を適用する開発を進めている。

NAND flash memory is now widely used in mobile terminals including notebook PCs, smartphones, and tablets, as well as various applications such as solid-state drives (SSDs) for high-end servers and data centers. Demand has been growing for higher speed, lower power consumption, and higher density accompanying the broadening of its areas of application.

To fulfill these requirements, Toshiba has introduced a through-silicon via (TSV) technology into NAND flash memory as a packaging technology using vertical vias to interconnect multiple silicon dies in a single package. In August 2015, we announced the development of the world's first 16-die stacked NAND flash memory package, which achieves more than double the data transfer rate and reduces power consumption by about half compared with those fabricated using conventional wire-bonding technologies. We are planning to apply this new technology to the development of a 32-die stacked package and the BiCS FLASH three-dimensional flash memory package.

#### 1 まえがき

近年NAND型フラッシュメモリは、ノートPCや、携帯電話、タブレットといった各種モバイル機器をはじめとして、ハイエンドサーバ、データセンターで用いられるストレージ製品など、様々なアプリケーションに使用されている。ハイエンドサーバやデータセンターなどでは、従来ストレージデバイスとして使用されてきたHDD(ハードディスクドライブ)からNAND型フラッシュメモリを用いたSSDへの置換えが進んでいる。これらのエンタープライズ向けのストレージデバイスは、小型かつ低消費電力で高速アクセスが可能というNAND型フラッシュメモリの特長を更に高めることが求められており、その実現方法の一つとしてTSV(Through Silicon Via)技術が注目されている。

TSV技術は、半導体チップの内部を垂直に貫通する電極を用いて、複数のチップを一つのパッケージ内に積層する。この技術は既にDRAMに適用され、4~8段の積層パッケージが実用化されている<sup>(1)-(3)</sup>。NAND型フラッシュメモリのパッケージに適用すると、データ転送速度の向上、低消費電力化、及び大容量化が可能になる。

東芝はTSV技術を適用した16段積層NAND型フラッシュメモリを世界で初めて<sup>(注1)</sup>開発し、2015年8月に発表した<sup>(4)</sup>。ここでは、TSV技術の特長や、当社におけるTSV技術を用いたNAND型フラッシュメモリの開発の経緯、性能向上などについて述べる。

### 2 TSV技術の特長

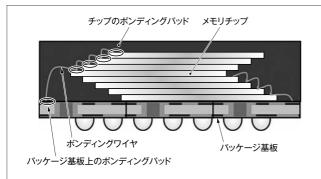

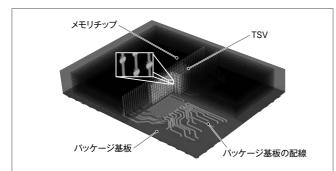

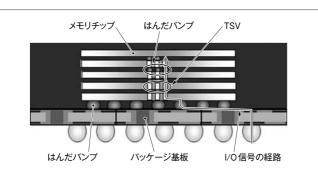

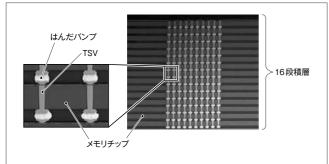

従来型のワイヤボンディング方式を用いたパッケージの断面イメージを図1に、TSV技術を用いたNAND型フラッシュメモリパッケージ内部の3次元イメージを図2に、その断面イメージを図3に示す。

従来技術のワイヤボンディング方式では、NAND型フラッシュメモリチップ(以下、メモリチップと略記)を階段状に積層し、パッケージ基板からボンディングワイヤで各メモリチップの端に配置されているボンディングパッドに配線することで電気的に接続する。パッケージ基板表面からはパッケージ基板内部の配線を通して裏面の外部端子に接続される。ワイヤボン

(注1) 2015年8月時点, 当社調べ。

図1. ワイヤボンディングパッケージの断面イメージ — パッケージ基板と各メモリチップをボンディングワイヤで接続するために、メモリチップが階段状に積層されている。

Cross-sectional structure of package fabricated using wire-bonding technology

図2. TSVバッケージの内部イメージ — パッケージ基板上にメモリチップが垂直に積層され、TSVで接続されている。

Internal structure of package fabricated using TSV technology

図3. TSVパッケージの断面イメージ — メモリチップどうしの間はメモリチップ内を貫通するTSVとはんだバンプで接続され、最下層のメモリチップははんだバンプでパッケージ基板と接続される。

Cross-sectional structure of package fabricated using TSV technology

ディング方式では、メモリチップの階段積層構造と、パッケージ基板上にボンディングパッド領域の確保が必要なため、搭載できるメモリチップの面積、すなわちメモリ容量が制限される。

一方TSV技術を用いたパッケージでは、図3に示すようにTSVが形成されたNANDチップを垂直に積層し、各チップ間ははんだバンプで接続されている。また、最下層のメモリチップの外部信号は配線層とはんだバンプを通してパッケー

ジ基板に接続される。パッケージ基板は、TSV用に高機能化 したり、層数を増やしたりする必要はなく、ワイヤボンディング 方式と同じ技術レベルのものを使用できる。

このようにTSV技術を用いるとメモリチップの垂直積層が可能になり、更にパッケージ基板のボンディングパッド領域が不要になるため、搭載可能なメモリチップ枚数の上限が増加する。

また、ワイヤボンディング方式の場合は、ボンディングパッドはメモリチップの一端にしか配置できず、配置できる最大ボンディングパッド数が数十個程度という制約があるが、TSV技術の場合はTSVの配置制約が少なく、電気特性上も最適な位置に多数を配置できる。このため、外部電源及びグランドの端子と各メモリチップ内の回路領域を低い寄生抵抗で接続できる。更に多数の制御信号やI/O (Input/Output) 信号をメモリチップ間で接続できる。これらにより、低消費電力化とデータ転送速度の向上が可能になる。

## 3 TSV技術を用いたNAND型フラッシュメモリ 開発の経緯

当社のTSV技術を用いたNAND型フラッシュメモリは、2010年にCMOS (相補型金属酸化膜半導体) イメージセンサにTSVを適用したときに培った技術<sup>(5)</sup>を応用して開発した。

2012年にボンディングパッドの領域にTSVを配置した19 nm 第1世代プロセスの64 GビットNAND型フラッシュメモリチップを8段積層し、評価サンプルを作成した。これは汎用メモリチップを用いて既存のボンディングワイヤ領域だけにTSVを配置して各メモリチップ間をTSVで接続した構造であったため、動作特性は既存製品と同等であったが、TSV技術を用いたNAND型フラッシュメモリパッケージの動作に成功した。この開発を通してTSVウェーハ加工プロセスと組立てプロセスを確立し、更に、TSVの電気的特性や、TSVがNAND型フラッシュメモリのメモリセル特性と周辺素子特性に与える影響などの基礎データを取得した。

2015年に、TSV技術を用いた19 nm第2世代プロセスの128 GビットNAND型フラッシュメモリチップを開発し、最大16 段積層 (記憶容量 256 Gバイト) のNAND型フラッシュメモリパッケージを作製した。

メモリチップは、TSV技術の長所を最大限に活用するために新たに設計した専用回路を搭載した。また、低消費電力化と高速化を実現するための課題となっていた寄生抵抗と寄生容量の低減を、構造デザインと加工プロセスの両面を最適化することで達成した。これらにより、消費電力とデータ転送速度に対する要求性能を満たすことに成功した。

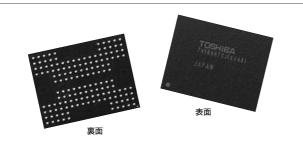

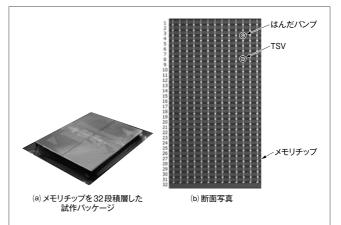

開発した19 nm第2世代プロセスのNAND型フラッシュメモリチップを用いたTSVパッケージの写真を**図4**に、19 nm

図4. 開発した19 nm第2世代プロセスの16段積層NAND型フラッシュメモリバッケージ — 外形は従来使われているワイヤボンディング方式のパッケージと同じで、標準の152 ボールのBGA (Ball Grid Array) パッケージである。

16-die stacked NAND flash memory package fabricated using second-generation 19 nm technology

## 表1.TSV技術を用いた19nm第2世代プロセスのNAND型フラッシュメモリパッケージの外形寸法と主な仕様

Basic specifications including external dimensions of second-generation 19 nm NAND flash memory package fabricated using TSV technology

| 項目        |            |      | 仕 様                  |      |

|-----------|------------|------|----------------------|------|

| パッケージタイプ  |            |      | NAND Dual x8 BGA-152 |      |

| 記憶容量      | 容量 (G バイト) |      | 128                  | 256  |

| 積層数       |            |      | 8                    | 16   |

| 外形寸法      | 幅          | (mm) | 14                   | 14   |

|           | 長さ         | (mm) | 18                   | 18   |

|           | 高さ         | (mm) | 1.35                 | 1.90 |

| インタフェース規格 |            |      | Toggle DDR           |      |

図5. TSV技術により16段積層したメモリチップの断面写真 — 16段積層したメモリチップどうしの間を TSV 及びはんだバンプで接続することで、寄生抵抗と寄生容量を低減した。

Cross-sectional X-ray image of 16-die stacked NAND flash memory package fabricated using TSV technology

第2世代プロセスのNAND型フラッシュメモリチップを用いた TSVパッケージの外形寸法と主な仕様を**表1**に示す。

パッケージ外形は、高さを除いて従来のワイヤボンディング接続のものとまったく同じ14(幅)×18(長さ) mmサイズで、外部端子もToggle DDR (Double Data Rate) 標準仕様としたため、従来型のワイヤボンディングによるパッケージをそのまま置き換えて実装できる。

チップ積層後のTSV断面写真を図5に示す。各チップに

図6. メモリチップを32段積層したバッケージとメモリチップの断面写真 — 2016年にメモリチップを32段積層したパッケージを試作し、技術的に実現可能であることを確認した。

Prototype 32-die stacked NAND flash memory package fabricated using TSV technology and cross-sectional X-ray image of memory chip

#### 1,000 個以上の TSV が配置されている。

2016年には、従来技術では困難だった32段積層パッケージの実現を目指して、TSV技術を用いてメモリチップの32段積層部品を試作した(図6)。試作品の評価を行い、技術的に実現可能であることを示す基礎データを得た。

## 4 TSV技術によるNAND型フラッシュメモリの 性能向上

TSV技術を用いたNAND型フラッシュメモリパッケージのデータ転送速度の向上, 低消費電力化, 及び大容量化について, 以下に述べる。

#### 4.1 データ転送速度の向上

従来のワイヤボンディング方式では、積層するチップ数が多いとパッケージの外部I/O端子の寄生容量が増大し、高い周波数で動作させる場合に障害になる。

一方、TSV技術を用いた多層パッケージの場合、外部I/O 端子には最下層のチップだけが接続されるため、積層するチップ数が増えても外部I/O端子の寄生容量は増大せず、高い周波数での動作を維持できる。

一般的なNAND型フラッシュメモリは8本の外部I/O端子で外部と接続される。今回開発したTSV技術を用いたNAND型フラッシュメモリでは、8本の外部I/O端子と接続される最下層チップとその他のチップの間は、64本のTSV端子で接続され、高いデータ転送バンド幅を実現している。最下層チップにはパラレルーシリアル変換回路を内蔵することで、8本の外部I/O端子は1Gビット/s以上と、従来の方式に比べて2倍以上の高速なデータ転送が実現できた。

#### 4.2 低消費電力化

従来のワイヤボンディング方式では、各メモリチップは一辺

にしかボンディングパッドを配置できない。また、ボンディングワイヤを用いて外部端子と接続するため、ボンディングパッドの開口面積及びピッチを縮小することが難しくボンディングパッドの数が限定される。このため、ワイヤボンディングによる積層では、電源及びグランドのボンディングパッドを適切な位置に配置できず、寄生抵抗を抑えて電源を供給することが難しい。

TSV技術を用いた場合、メモリチップのメモリセル領域以外であればTSV端子を配置できるため、低い寄生抵抗でメモリチップ内の各回路に電源及びグランドを供給できる。

今回の開発では、メモリチップ内のフラッシュメモリについてコア電源電圧の下限を2.35 Vから1.7 Vに抑えることが可能になり、メモリチップのProgram (データ書込み)、Read (データ読出し)、及びErase (データ消去)の基本動作の消費電力を30%以上削減した。更に、TSV端子の配置と接続の自由度が高いことでメモリチップの設計アーキテクチャの最適化も可能になり、データの送受信の消費電力を50%以上削減した。

#### 4.3 大容量化

2章で述べたとおり、従来のワイヤボンディング方式では、メモリチップを階段状に積み上げる必要があり、ボンディングパッドを配置するエリアの確保も必要だった。このため同じパッケージサイズに実装できるメモリチップのサイズは、積層数が増えるに従って小さくなるという制約があった。一方、TSV技術を用いた場合、チップを階段状に積み上げる必要がなく、多段に積層してもパッケージサイズに近い大きさのメモリチップを搭載できる。

また4.1節及び4.2節のとおり、ボンディングワイヤで各チップの信号、及び電源とグランドの端子を接続する場合、16段以上の積層を行うと寄生容量や寄生抵抗が大きくなり、信号特性や消費電力効率を悪化させるが、TSV技術を用いると解決できる。

これらにより、従来は困難であった32段、64段といったメモリチップの超積層が可能になり、超高密度パッケージを実現できる。

## 5 TSV技術を用いたNAND型フラッシュメモリ の今後

NAND型フラッシュメモリは、メモリセルの3次元化により大容量化、及びビット単価の低減が更に進むことが予想されており、現在、データセンターやエンタープライズストレージ製品ではHDDからSSDへの移行が急速に進んでいる。これらのアプリケーションでは、ストレージの大容量化の要求とともに、単位時間当たりの書込みと読出しのデータ量(I/Oバンド幅)が増大し、消費電力の削減がTCO(Total Cost of Ownership)抑制の重要な要素となっている。

TSV技術は、高速化、低消費電力化、及び大容量化という

要求を同時に満たすことができるため、当社の3次元フラッシュメモリBiCS FLASHと組み合わせた製品の量産化が期待されている。

#### 6 あとがき

当社はNAND型フラッシュメモリの高速化、低消費電力化、及び大容量化を目指して、TSV技術をNAND型フラッシュメモリに適用し、16段積層の19 nm第2世代プロセスNAND型フラッシュメモリを開発した。ここではその技術の特長と、適用アプリケーションでの利点について述べた。

現在、BiCS FLASHにTSV技術を適用する開発を進めており、製品化を予定している。

## 文 献

- (1) Kim, J. "The Future of Graphic and Mobile Memory for New Applications". Hot Chips 28 Tutorials. Hot Chips homepage. <a href="http://www.hotchips.org/wp-content/uploads/hc\_archives/hc28/HC28.21-Tutorial-Epub/HC28.21.1-Next-Gen-Memory-Epub/HC28.21.122-Next-Gen-Mem-GPU-Kim-SAMSUNG-v02-t1-3.pdf">https://www.hotchips.org/wp-content/uploads/hc\_archives/hc28/HC28.21-Tutorial-Epub/HC28.21.1-Next-Gen-Memory-Epub/HC28.21.122-Next-Gen-Mem-GPU-Kim-SAMSUNG-v02-t1-3.pdf</a>, (accessed 2016-09-15).

- (2) Tran, K. "The Era of High Bandwidth Memory". Hot Chips 28 Tutorials. Hot Chips homepage. <a href="http://www.hotchips.org/wp-content/uploads/hc\_archives/hc28/HC28.21-Tutorial-Epub/HC28.21.1-Next-Gen-Memory-Epub/HC28.21.130-High-Bandwidth-KEVIN\_TRAN-SKHYNIX-VERSION\_FINAL-dcrp-t1-4\_.pdf">http://www.hotchips.org/wp-content/uploads/hc\_archives/hc28/HC28.21-Tutorial-Epub/HC28.21.1-Next-Gen-Memory-Epub/HC28.21.130-High-Bandwidth-KEVIN\_TRAN-SKHYNIX-VERSION\_FINAL-dcrp-t1-4\_.pdf</a>, (accessed 2016-09-15).

- (3) Pawlowski, J. "Memory as We Approach a New Horizon". Hot Chips 28 Tutorials. Hot Chips homepage. <a href="http://www.hotchips.org/wp-content/uploads/hc\_archives/hc28/HC28.21-Tutorial-Epub/HC28.21.1-Next-Gen-Memory-Epub/HC28.21.110-Memory-Horizon-Pawlowski-microniv1-t1-2.pdf">http://www.hotchips.org/wp-content/uploads/hc\_archives/hc28/HC28.21-Tutorial-Epub/HC28.21.1-Next-Gen-Memory-Epub/HC28.21.110-Memory-Horizon-Pawlowski-microniv1-t1-2.pdf</a>, (accessed 2016-09-15).

- (4) 東芝. "世界で初めてTSV技術を用いた最大16段積層NAND型フラッシュメモリの開発について". 東芝プレスリリース. <a href="http://toshiba.semiconstorage.com/jp/company/news/news-topics/2015/08/memory-20150806-1.htm">httm</a>, (参照 2016-09-15).

- (5) 東芝. "TCV技術を適用した超小型カメラモジュール「CSCM」を世界で初めて製品化、一貫生産開始"、東芝プレスリリース、 <a href="http://www.toshiba.co.jp/about/press/2007\_10/pr\_j0102.htm">http://www.toshiba.co.jp/about/press/2007\_10/pr\_j0102.htm</a>, (参照 2016-09-15).

#### 松寺 克樹 MATSUDERA Katsuki

ストレージ&デバイスソリューション社 メモリ事業部 メモリ 応用技術第二部グループ長。NAND型フラッシュメモリ製品 の企画・開発・拡販に従事。 Memory Div.

#### 河崎 一茂 KAWASAKI Kazushige

ストレージ&デバイスソリューション社 メモリ事業部 メモリ パッケージ開発部主務。各種メモリパッケージの開発・設計 に従事。

Memory Div.