# ストレージプロダクツ向けのプリント回路板開発での DFM 適用

Toshiba's DFM-Based Approach to Printed Circuit Boards for Storage Products

石崎 聖和 石井 憲弘 梶 桂子

■ISHIZAKI Kiyokazu

■ ISHII Norihiro

KAJI Keiko

SSD (ソリッドステートドライブ) や, HDD (ハードディスクドライブ), SSHD (ソリッドステートハイブリッドドライブ) などのストレージプロダクツに搭載されるプリント回路板は, 大容量化のために高密度実装技術が求められる。特に, コントローラなどの大型の電子部品や, プリント配線板などはその設計が工場における製造品質や生産性に影響し, 不具合の是正には後戻りコストや日数が必要となる重要部品のため, 設計段階における仕様の最適化が重要である。

東芝は、設計の上流段階において、シミュレーションなどを活用したDFM (Design for Manufacturability)を適用することで、はんだ接合の信頼性などの製造品質確保、プリント配線板仕様の最適化などによるコスト低減、及び製造能力への適合などによる生産性向上を実現させた。

There is a need for high-density mounting technologies for printed circuit boards (PCBs) installed in storage products such as solid-state drives (SSDs), hard disk drives (HDDs), and solid-state hybrid drives (SSHDs), in line with the increasing data storage capacity of such products. In particular, it is important to optimize the design specifications of large-scale controller chips and printed wiring boards (PWBs), which are the main components affecting manufacturing quality and productivity in the factory, in order to eliminate costly and time-consuming design change processes in the event of a failure.

Toshiba has applied an approach based on design for manufacturability (DFM) to PCBs for storage products at the initial stage of design, taking manufacturing quality, productivity, and production costs into consideration. By conducting a variety of simulation experiments using this approach, we have succeeded in assuring quality, reducing costs, and improving the productivity of PCB manufacturing.

### 1 まえがき

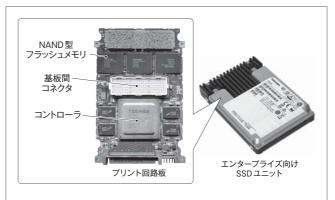

東芝は、モバイルノートPC (パソコン)やエンタープライズ向けサーバなどの記憶媒体として、SSDや、HDD、SSHDなどのストレージプロダクツを市場に提供しており、プリント回路板からユニット組立まで自社工場で設計し製造している。また、SSDやSSHDの記憶デバイスとして用いられるNAND型フラッシュメモリの設計と製造にも、自社製の強みを生かして連携しており、各工程にフィードバック可能な製品開発を行っている。

一方、ストレージプロダクツの大容量化に伴い、ユニット内での記憶媒体の占める領域が拡大傾向にあり、プリント回路板に確保できる制御回路部の領域が狭くなってきている。更に、アクセス性能の高速化や安全性の高いデータ保全機能の搭載などによって搭載部品や電子回路が増える傾向にあり、プリント回路板では高密度実装技術が必要不可欠となっている。

そのような背景もあり、プリント配線板に実装される主要部品であるコントローラは、高密度化と多機能化に伴い多ピン化が可能なBGA (Ball Grid Array)パッケージ構造の採用が多くなっている。そして、いっそうの多ピン化や、限られた領域に実装するためのパッケージサイズの小型化を実現するため、BGAパッケージにおいても接続ピンが狭ピッチ化される傾向

図1. エンタープライズ向けSSDに搭載されているプリント回路板 — 高品質で低コストなプリント回路板を実現するために,製造品質や,生産 性,コストなどを考慮したDFMを適用している。

PCB installed in SSD for enterprise use

にあり、高品質で低コストなプリント回路板の実現が難しくなってきている。

ここでは、ストレージプロダクツの一つであるエンタープライズ向けSSDに搭載されているプリント回路板(図1)の開発において、その設計段階で製造品質や、生産性、コストなどを考慮したDFM (Design for Manufacturability)を適用した例について述べる。

# 2 プリント回路板開発でのDFM適用の概要

#### 2.1 プリント回路板開発の流れ

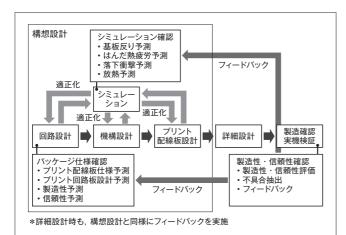

プリント回路板開発の流れを図2に示す。回路設計や,機構設計,プリント配線板設計,シミュレーションなどを行う構想設計から始まり,詳細設計,製造性確認,実機検証の順に開発を進めている。

このように設計プロセスは、製品仕様を決めていくなかで様々な仕様を模索する構想設計段階と、構造を具体化させて製品としての作り込みを行う詳細設計段階に分かれている。

#### 2.2 DFM 適用の概要

一般にDFMとは、製造のしやすさを考慮した製品設計手法の総称であるが、ここでのDFMは、構想設計段階など上流の設計工程で、はんだ接合信頼性などの品質確保、製造能力への適合化などによる生産性確保、及びプリント配線板最適化などによるコスト低減を実現するための設計手法としている。

自社工場で実施している製造性確認や実機検証結果を設計ルールやシミュレーションモデルにフィードバックし、設計手法の妥当性を確認して見直すことにより、DFMとしての精度を高めるプロセスを構築している。

# 3 パッケージ仕様の決定及びプリント配線板の設計

#### 3.1 設計上の懸念点

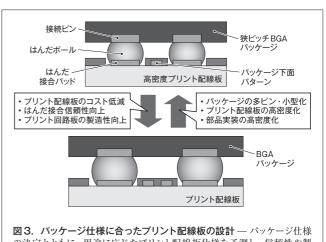

パッケージ仕様は、プリント配線板の仕様に関わるため、プリント配線板の製造性やコスト、及び電子部品実装時の製造性やはんだ接合信頼性に影響する。作り直しは容易にできないため、パッケージ仕様の決定は、構想設計段階において重要である。

特にコントローラは、パッケージサイズが大型で接続ピン数

図2. プリント回路板開発の流れ — 設計プロセスは、様々な仕様を模索する構想設計段階と、構造を具体化させて製品としての作り込みを行う詳細設計段階に分かれている。

Flow of PCB development

も多く、開発費や購入価格も高い重要部品のため、仕様の最 適化が必須となる。

例えば、高密度化に対応して実装面積を抑えるため、BGA パッケージを採用するとともに接続ピンを狭ピッチ化して小型 化した場合は、電極サイズが小さくなることで、はんだ接合強 度の低下やはんだ付け状態のばらつきなど、製造性が悪化する懸念がある。また、狭ピッチで接続ピン数が増えることで、パッケージ下面での接続ピンからのパターンレイアウト領域が 制限されてしまうため、複雑で作りにくい高密度なプリント配 線板が必要となり、高価になってしまう懸念がある。

#### 3.2 DFM

設計上の懸念点を解決するために、パッケージ仕様の決定に合わせ、プリント配線板では、上流の設計工程でDFMを適用している。この中で、パターンレイアウトの引出し性などパターンレイアウト設計の確認や、信頼性と製造能力に適合するはんだ接合パッドサイズの決定など実装設計の確認、一般の貫通プリント配線板など用途に応じたプリント配線板仕様への適合性確認などを行う(図3)。

### 4 シミュレーションの活用

製造時や市場で想定される様々な負荷に対して生じるプリント回路板の挙動を,各種シミュレーションにより早い段階で予測して設計にフィードバックしている。

## 4.1 基板の反りシミュレーション

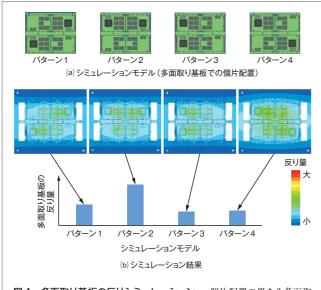

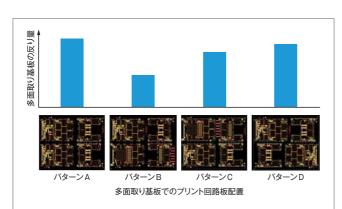

プリント回路板のリフロー後の反りを抑制することは、製造品質向上のために重要である。多面取り基板を製造用ジグにセットした状態をモデルとし、リフロー工程での温度プロファイルを模擬した温度負荷をモデル全体に与え、反り量を予測したシミュレーションを行う。多面取り基板での個片(プリント回路板)の配置方法を変えた複数のモデルでシミュレーショ

図3. パッケージ仕様に合ったプリント配線板の設計 — パッケージ仕様の決定とともに、用途に応じたプリント配線板仕様を予測し、信頼性や製造性の適合確認を行う。

PWB design in accordance with package specifications

図4. 多面取り基板の反りシミュレーション — 個片配置の異なる多面取 り基板で、それぞれに対するリフロー後の反り量を予測した。

Warpage simulation of multi-piece PCBs after reflow process

ンを行い、コスト及び製造性も考慮した最適な個片配置を決 定している。多面取り基板の反りシミュレーション結果の例を 図4に示す。

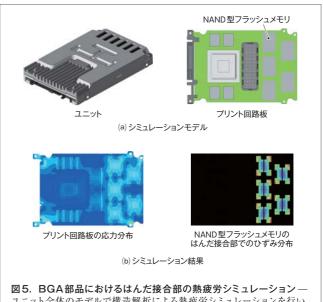

#### 4.2 はんだ熱疲労シミュレーション

プリント配線板に実装した部品のはんだ接合部では、製品 使用時の電源オン/オフによる温度上昇/下降の繰り返しに よって、部品と基板の熱膨張率の差に起因する熱疲労が発生 する。そこで、筐体(きょうたい)や基板の設計段階で、筐体 や、 基板、 主要部品などのユニット全体をモデル化して温度サ イクル試験を模擬したシミュレーションを実施し、主要部品の 最適配置などを設計にフィードバックしている。熱疲労シミュ レーション結果の例を図5に示す。

# 4.3 落下衝撃シミュレーション

大容量のデータを扱うストレージプロダクツでは, 耐衝撃性 の確保も重要な課題である。設計の後戻りを防止するには、 筐体内部でのプリント回路板の変形挙動を設計の早期段階で 予測して危険箇所を把握し, 対策を行う必要がある。 落下衝 撃シミュレーションの概要を図6に示す。部品どうしの予期し ない干渉の確認や、負荷が大きい箇所の把握などを行い、設 計段階で信頼性向上につなげている。

### 4.4 放熱シミュレーション

近年、エンタープライズ向けSSDではデータ処理の高速化な どによりコントローラからの発熱が大きくなってきているため、 NAND型フラッシュメモリのパッケージの温度が動作可能温 度域に収まるように放熱設計を行う必要がある。そのためシ ミュレーションにより事前に十分な放熱検討を行っている。エ ンタープライズ向けSSDがサーバ内に設置された状態のとき に想定される空気の流れを条件にし、製品動作時の消費電力

ユニット全体のモデルで構造解析による熱疲労シミュレーションを行い、 はんだ接合部の信頼性を評価した。

Thermal fatigue simulation of solder joints of ball grid array (BGA) package on PCB

に基づいて各部品の温度上昇を予測し、設計にフィードバック している。

#### 5 実機検証. 製造性確認事例

DFMの効果検証のため、実機を用いた製造性やはんだ接 合信頼性を確認している。

特

**図7. 基板間コネクタのはんだ接合性向上** - 基板間コネクタのキャップ に穴を開けることで、リフロー炉内での熱伝導性が上がり、はんだ接合に 適切な温度管理が可能になった。

Improvement of solderability of board-to-board connector

図8. 多面取り基板の反り量 一 配置の違いにより、リフロー後の多面取り基板の反り量が異なる。 反りが小さいほうが実装性や実装品質が良い。 Results of warpage measurements of multi-piece PCBs after reflow process

# 5.1 製造性

プリント回路板については、安定した量産品質を保つため、試 作段階での問題点の洗い出しと早期改善が重要となっている。

プリント回路板どうしを接続する基板間コネクタを**図7**に示す。 従来は、接触ピンの保護及び実装時の吸着部として、キャップがコネクタ全面を覆う仕様であったため、リフロー炉の熱がキャップに遮られ、はんだ接合部の温度が十分に上がらなかった。そこで、接触ピン保護と製造性の確保が可能なキャップ穴を設計し、熱伝導率を最適化することで、この課題を解決した。

多面取り基板のリフロー後の反り量を図8に示す。この反り量が大きくなると、次工程の部品実装やユニット組立など製造性で大きな課題となる。そこで、プリント回路板の配置の方向を工夫することで、リフロー後のプリント回路板の反りを低減させ、次工程の製造性と実装品質を向上させている。また、4.1節で説明したシミュレーションの結果とこの実測結果をすり合わせることで、シミュレーションの精度向上も図っている。

このように、製造性の向上及び実装品質の改善を試作段階で実施し、製品の量産品質を確保している。

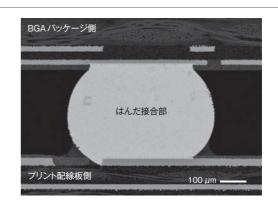

# 5.2 はんだ接合の信頼性

はんだ接合の信頼性評価として、実際の製品を模擬した評価用のプリント回路板を用いて温度サイクル試験を実施している。この評価で用いるBGAパッケージは、電気抵抗をモニタ

図9. 温度サイクル試験後のはんだ接合部の断面 — BGA パッケージにおいて、温度サイクル試験後もはんだ接合部に損傷がないことを確認した。 Cross-sectional image of solder joint after temperature cycle test

リングすることではんだ接合部の故障サイクルを検出できる配線となっている。

温度サイクル試験後のBGAパッケージにおけるはんだ接合部の断面を図9に示す。温度サイクル試験後も故障の発生はなく、はんだ接合部にクラックなどの損傷も見られず、良好な状態であることが確認できている。このように、はんだ接合の信頼性が重要な部品においては、故障サイクルの検出による熱疲労寿命と接合部の状態の確認を早期に実施し、結果を量産設計へフィードバックしている。

### 6 あとがき

当社は、ストレージプロダクツの設計と製造を自社工場で行っている強みを生かし、プリント回路板へのDFM適用と、その効果検証を繰り返すことで、設計ルールやシミュレーションモデルの最適化を進めている。今後も、ストレージプロダクツの更なる大容量化や高密度化に対応しつつ、高品質で低コストなプリント回路板の開発を積極的に進めていく。

#### 石崎 聖和 ISHIZAKI Kiyokazu

ストレージ&デバイスソリューション社 半導体研究開発センター パッケージソリューション技術開発部主務。実装設計・開発に従事。

Center for Semiconductor Research & Development

#### 石井 憲弘 ISHII Norihiro

ストレージ&デバイスソリューション社 半導体研究開発セン ター パッケージソリューション技術開発部主務。実装要素 技術開発に従事。

Center for Semiconductor Research & Development

#### 梶 桂子 KAJI Keiko

ストレージ&デバイスソリューション社 半導体研究開発センター パッケージソリューション技術開発部主務。機械系のCAE業務に従事。

Center for Semiconductor Research & Development