特 集 SPECIAL REPORTS

# 半導体製品の耐ノイズ設計を支援する EMC評価・実装シミュレーション技術

EMC Design Evaluation and Simulation Technologies to Support Noise-Tolerant Semiconductor Product Design

岡野 資睦 今泉 祐介 辻村 俊博

■ OKANO Motochika ■ IMAIZUMI Yusuke ■ TSUJIMURA Toshihiro

車載を中心に電磁波ノイズによる電子機器の誤動作の防止が安全確保の観点から最重要項目として挙げられ、ECU (Electronic Control Unit) メーカーが半導体部品を選定する際に、機能、サイズ、及びコストの他にEMC (Electro Magnetic Compatibility:電磁両立性)耐性も重要な評価項目となってきている。

そこで東芝は、半導体部品のEMC耐性についての情報をいつでも提示できるように、IEC (国際電気標準会議)が規定する 半導体EMC評価方法に関するIEC 61967シリーズ (EMI (電磁干渉) 試験) とIEC 62132シリーズ (EMS (電磁感受性) 試験) に基づいた試験環境を構築した。また、試験結果が思わしくなかった場合に原因と対策を抽出するための実装シミュレーション技術を構築し、半導体部品に問題があった場合には即座に半導体設計へフィードバックし、周辺回路に問題があった場合には顧客に具体的な対策案を提示できる環境を実現した。これにより、半導体製品の開発強化ができるとともに、EMC耐性が高いECU製品の開発にも貢献できる。

With the expanding use of in-vehicle electronics in recent years, malfunctions of electrical equipment caused by electromagnetic noise have become a safety issue in the automotive field. In particular, electromagnetic compatibility (EMC) tolerance is an important evaluation item for electronic control unit (ECU) manufacturers when selecting semiconductor devices, in addition to performance, compactness, and cost.

In order to provide customers with information on the EMC tolerance of its semiconductor products at any time, Toshiba has constructed test environments complying with the IEC (International Electrotechnical Commission) 61967 series standards for electromagnetic interference (EMI) and IEC 62132 series standards for electromagnetic susceptibility (EMS). We have also established EMC simulation technologies to determine whether an abnormality is caused by our product or the printed circuit board (PCB) when the test result is unsatisfactory. In the event that a problem is identified in our semiconductor product by such simulation, we can immediately feed back the necessary countermeasures to the design. If a problem is identified in the peripheral circuit, on the other hand, we can provide customers with a specific solution based on the evaluation result. Our EMC design evaluation and simulation technologies can therefore not only strengthen semiconductor product development capabilities, but also contribute to the development of ECUs with high EMC tolerance.

# 1 まえがき

近年の電子機器の急速な発展により、メカニカル制御されていた部分の多くが電子化され、これまで困難であった複雑な制御が可能になるなど、生活環境の利便性が急速に高まっている。しかし、それに伴い電磁波ノイズによる電子機器の誤動作は、安全問題にも関わることから、そのリスクが社会問題として大きくクローズアップされるようになり、EMCに関する規制も強化され始めている。

特に車載用電子機器では、国際連合が定めた安全規則 ECE Regulation No.10に基づき、国内でも「道路運送車両の保安基準」に関わる新たな基準が国土交通省から告示され、EMC規制の対象が、これまで"自動車"そのものであったのに対し、"自動車に搭載される電子機器で永続的に設置されるもの"、すなわちECUにまで拡大された(注1)。これに伴い、ECUメーカーは製品の基板に搭載する半導体部品を選定する際の評価項目として、機能、サイズ、及びコストの他に、EMC耐性の

レベルも挙げるようになった。

そこで、東芝は事前に、あるいは要求されれば即座に、提供する半導体部品のEMC耐性について、その実力を提示できるように、IECの半導体EMC評価方法に関する規格IEC 61967シリーズ(EMI試験)とIEC 62132シリーズ(EMS試験)に基づいた試験環境の構築を行った( $\mathbf{表1}$ )。

また、試験結果が思わしくなかった場合に、原因が半導体部品にあるのか、それ以外の周辺回路にあるのかを切り分けるための、EMCシミュレーション環境も同時に構築した。これにより、半導体部品に問題があった場合は即座に半導体設計へフィードバックし、周辺回路に問題があった場合は顧客に具体的な対策案を提示することが可能になった。

<sup>(</sup>注1) 2016年8月1日以降に生産された新型車に続き, 2016年10月28日 以降に生産された継続生産車にも順次適用となり, 販売条件の義務 化が行われた。

特

### 表1. 半導体EMCの試験方法と国際規格

EMC test methods and IEC standards for semiconductor devices

| 項目  | 試験方法        | 対象ノイズ | 国際規格        |

|-----|-------------|-------|-------------|

| ЕМІ | 一般条件と定義     | -     | IEC 61967-1 |

|     | TEMセル法      | 放射    | IEC 61967-2 |

|     | 表面走査法       | 放射    | IEC 61967-3 |

|     | 1 Ω /150 Ω法 | 伝導    | IEC 61967-4 |

|     | WBFC法       | 伝導    | IEC 61967-5 |

|     | MP法         | 伝導    | IEC 61967-6 |

|     | ICストリップライン法 | 放射    | IEC 61967-8 |

| EMS | 一般条件と定義     | _     | IEC 62132-1 |

|     | TEMセル法      | 放射    | IEC 62132-2 |

|     | BCI法        | 伝導    | IEC 62132-3 |

|     | DPI法        | 伝導    | IEC 62132-4 |

|     | WBFC法       | 伝導    | IEC 62132-5 |

|     | ICストリップライン法 | 放射    | IEC 62132-8 |

|     | 表面走査法       | 放射    | IEC 62132-9 |

WBFC: Workbench Faraday Cage MP: Magnetic Probe 放射:空間を伝わるノイズの評価方法 伝導:配線やケーブルを伝わるノイズの評価方法

# 2 半導体製品を取り巻くEMC規制環境

# 2.1 半導体 EMC の評価方法に関する規格

EMI試験とEMS試験には、表1に示すように複数の試験 方法があり、どの試験方法を選択するかは、目的に応じて顧客 と決める必要がある。よく採用される試験方法としては、EMI では1 Ω /150 Ω法及び TEM (Transverse Electromagnetic) セル法が、EMSではDPI (Direct Radio Frequency Power Injection) 法, BCI (Bulk Current Injection) 法, 及びTEM セル法が挙げられる。

# 2.2 半導体EMCの評価基板

半導体EMCの評価基板については、IEC 61967-1及びIEC 62132-1に仕様が記載されている。以下に評価基板の主な仕 様を記載する。

- (1) サイズは、10(幅)×10(長さ)cmで、特にTEMセル法 及びIC ストリップライン法では必須である。

- (2) 基板端は、少なくとも5mm以上をすず又は金でめっ きする。

- (3) ビアは、基板端から少なくとも5 mm以上離す。

- (4) 四隅に穴を開け、ねじで固定できるようにする。

- (5) 基板層数は、4層以上を推奨する。

- (6) 評価対象ICを表面側に配置し、それ以外の部品は全 て裏面側に配置する。

- (7) 空き領域は、可能な限り接地線で覆う。

- (8) ビア間隔は, 10 mm以下とする。

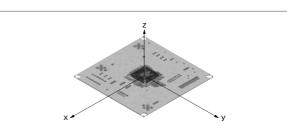

実際に製造した半導体EMC評価基板の例を図1に示す。

## 2.3 BISS規格

表1のIEC規格には、試験方法だけが記載されており、判

**図1. 半導体EMCの評価基板の例** — IEC 61967-1 及び IEC 62132-1の 仕様に基づいて設計している。

Example of PCB for EMC evaluation of semiconductor devices

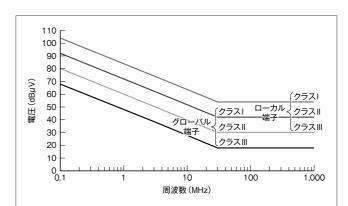

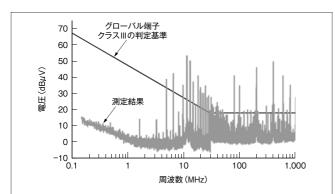

図2. BISS 規格における150 Ω法の判定基準 — 端子の接続先や用途 に応じて異なる判定基準を設けている。

Acceptance criteria of 150  $\Omega$  direct coupling method according to BISS standards

定基準は記載されていない。国内では顧客の社内基準への 対応要求が多いが、欧州ではZVEI(ドイツ電気・電子工業連 盟) による仕様書 Generic IC EMC Test Specification (通 称BISS (Bosch, Infineon, Siemens VDO) 仕様書) に記載 されている判定基準への対応を要求されることが増えている。 BISS規格における150 $\Omega$ 法の判定基準を示したのが**図2**で ある。IC端子の用途に応じてグローバル端子とローカル端子 に分類され、更にその中がクラスⅠ、Ⅱ、及びⅢの3段階に分 類される。グローバル端子はECU外部との入出力に使用する 端子であり、ローカル端子はECU内部で使用する端子であ る。クラスⅢは車両制御系ICに、クラスⅡは情報通信系IC に、クラスIはそれ以外のICに適用される。したがって、図2 からわかるように車両制御系ICでECU外部との入出力に使 用する端子にもっとも厳しい判定基準が適用される。

#### 3 実機での検証

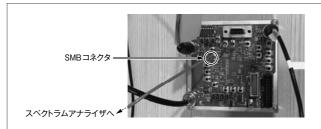

車載モータ制御用マイコンを評価対象とした。150 Ω法での 測定のようすを示したのが**図3**である。これは、IC端子から の伝導ノイズを測定することを目的としており、EMIの測定再 現性も高い。

$<sup>*1\</sup>Omega/150\Omega$ 法は通称 VDE (ドイツ電気技術者協会)法とも呼ばれる \*IEC 61967-7, IEC 62132-6, 及びIEC 62132-7は欠番

図3. 車載モータ制御用マイコンでの150  $\Omega$ 法測定のようす — SMB コネクタ (評価端子) とスペクトラムアナライザをケーブルでつないで測定する。 Measurement of microcontroller for automotive motor controllers using 150  $\Omega$  direct coupling method

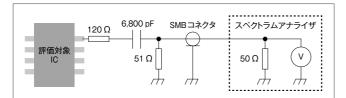

150 Ω法では評価対象のIC端子に対して図4に示すように抵抗、コンデンサ、及び評価端子としてのSMB (Sub Miniature Type B) コネクタをIC端子近傍に実装し、SMBコネクタに出てくる伝導ノイズをスペクトラムアナライザで測定している。全ての端子に対してこのような測定ポートを設けるのは困難なため、電源端子及びグローバル端子から優先的に評価対象にしていく。ローカル端子は、用途や重要度に応じて選択する。

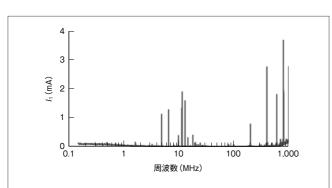

図3の車載モータ制御用マイコンの電源端子を対象に、 $150 \Omega$  法で測定した結果が図5である。ただし、この結果はコンデンサが電源に実装されていない、実使用状態とは異なる状態で得られたものである。電源端子のごく近くに $0.1 \mu$ Fと $0.01 \mu$ Fのデカップリングコンデンサを実装したときの測定結果が図6

図4. 150 Ω法で用いる評価用回路 — 評価端子ごとにこの回路網を実装して測定を行う。

Evaluation circuit used in 150  $\Omega$  direct coupling method

図5. 電源端子の150 Ω法での測定結果 — 電源にコンデンサが実装されていない状態での測定結果であり、ノイズが大きい。

Result of measurement of noise level at 1.2 V power supply terminal using 150  $\Omega$  direct coupling method

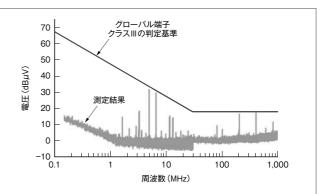

図6. デカップリングコンデンサ追加後の150 Ω法での測定結果 — デカップリングコンデンサを適切に配置することで、ノイズが大幅に低減する。

Result of measurement of noise level at 1.2 V power supply terminal after addition of decoupling condenser using 150  $\Omega$  direct coupling method

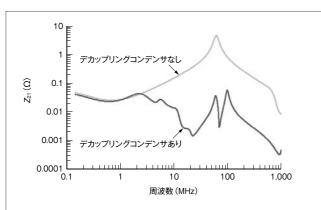

である。デカップリングコンデンサの追加により、大きなノイズ低減効果が得られることが確認できる。

# 4 電磁界解析による検証

3章では、デカップリングコンデンサを最適配置で実装する ことで十分なノイズ低減効果が確認できたが、事前にこの実 装効果を電磁界解析から予測できないかを検証した。

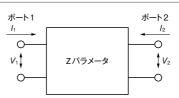

まず、評価基板 (IC パッケージ配線モデルを含む) の解析モデル (**図7**) を作成し、IC のチップ端 (ポート1) -SMBコネクタ (ポート2) 間のZパラメータを求める。

次に、このZパラメータからポート1での電流モデルを求める。Zパラメータを用いた4端子回路網を図8に示す。このと

図7. 評価基板の解析モデル — IC パッケージを実装し、その配線モデルも含んだ解析モデルを作成して電磁界解析を実施する。

Simulation model of PCB for evaluation

図8. 4端子回路網 — ポート1をICのチップ端に、ポート2をSMBコネクタにした4端子回路網のZパラメータを解析に用いる。

Four-terminal network configuration

特

き,各ポートの電圧 $V_i$  (i=1, 2) と電流 $I_i$  (i=1, 2) の関係は、式(1)で表される。

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} Z_{11} & Z_{12} \\ Z_{21} & Z_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

(1)

ここで、 $Z_{11}$ 及び $Z_{22}$ はインプット及びアウトプットインピーダンスで、 $Z_{12}$ 及び $Z_{21}$ はトランスファーインピーダンスである。ポート2側からの電流  $I_2$ は0と考えられるので、ポート1での電流  $I_1$ は、式(2)で算出できる。

$$I_1 = V_2 / Z_{21} \tag{2}$$

$V_2$ は、デカップリングコンデンサなしでの150  $\Omega$ 法におけるポート2での測定電圧なので、Zパラメータの $Z_{21}$ を用いて電流 $I_1$ を抽出することが可能になる。抽出した電流モデルを**図9**に示す。

最後に、デカップリングコンデンサを追加した解析モデルを作成し、これを用いた電磁界解析を行う。デカップリングコンデンサの有無による $Z_{21}$ の比較を**図10**に示す。 $0.1~\mu$ F及び $0.01~\mu$ Fのデカップリングコンデンサを電源端子近傍に実装することで、 $3\sim 1,000~\mathrm{MHz}$ の帯域で $Z_{21}$ が下がっていることが

**図9. 作成した電流モデル** — 150  $\Omega$ 法の測定結果とZパラメータから電流モデルが求まる。

Current model extracted from measurement and simulation results

図10. デカップリングコンデンサの有無による $Z_{21}$ の比較 — デカップリングコンデンサの実装により、 $3\sim 1{,}000~{

m MHz}$ の帯域で $Z_{21}$ が小さくなる。Comparison of transfer impedance ( $Z_{21}$ ) with and without decoupling condenser

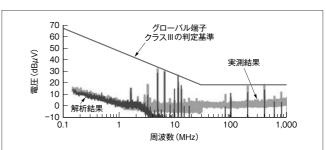

**図11. 解析結果と実測値との比較** — ピークのある周波数は、両者でよく一致しており、誤差は約 $5\,\mathrm{dB}_{\mu}\mathrm{V}$ 以内であった。

Comparison of simulation and measurement results

確認できる。

解析結果を**図11**に示す。デカップリングコンデンサ追加基板(図10のデカップリングコンデンサありでの $Z_{21}$ )に、図9の電流モデルを付加したときの150  $\Omega$ 法の解析結果である。図6のデカップリングコンデンサ追加後の150  $\Omega$ 法測定結果も併せて記載してある。強くピークが出ている周波数はよく一致しており、誤差もおおむね5 dB $\mu$ V以内に収まっている。誤差の原因としては、測定時の他の端子からのクロストークによる結合や解析モデルでの主要部品以外の簡略化などが挙げられる。

デカップリングコンデンサなしの状態で作成した電流モデルから、デカップリングコンデンサありの状態を電磁界解析で予測できることを確認した。この電流モデルは顧客が設計した基板にも適用でき、事前にレイアウト検証が可能になる。

# 5 あとがき

当社は、IECの半導体EMC規格に準拠した試験環境と、 試験結果を検証するための実装シミュレーション技術を構築 した。今後、これらをベースに、半導体製品の開発強化にと どまらず、顧客とともにEMC耐性の強いECU製品の開発に 貢献していく。

### 岡野 資睦 OKANO Motochika, Ph.D.

ストレージ&デバイスソリューション社 半導体研究開発センターパッケージソリューション技術開発部参事,博士(工学)。CAD/CAEの設計環境構築及びモジュールを中心とした設計に従事。Center for Semiconductor Research & Development

### 今泉 祐介 IMAIZUMI Yusuke

ストレージ&デバイスソリューション社 半導体研究開発セン ター パッケージソリューション技術開発部主務。EMC評価 環境の構築及びアンテナ設計に従事。

Center for Semiconductor Research & Development

### 辻村 俊博 TSUJIMURA Toshihiro

ストレージ&デバイスソリューション社 半導体研究開発センター パッケージソリューション技術開発部主務。電気及び熱のシミュレーション業務に従事。

Center for Semiconductor Research & Development