# HIGHLIGHTS 2012

### 電子デバイス

電子デバイス分野では、最先端プロセス技術と設計・応用技術力を核として、"トータルストレージイノベーション"を牽引する新たなキーデバイスの開発に注力しています。19 nm世代 NAND型フラッシュメモリを積層した高性能メモリや、HDDにNAND型フラッシュメモリを搭載したハイブリッドドライブ、プロセッサの消費電力の削減を可能にする MRAM (磁性体メモリ) など新規開発に取り組んでいます。

- ▲ Visconti<sub>™</sub>2を用いた先進運転支援システム Application of Visconti<sub>™</sub>2 image recognition processor to advanced driver assistance system (ADAS)

- ▼ Visconti<sub>TM</sub>2 各モジュールの演算性能と消費電力 Performance and power consumption of each module of Visconti<sub>TM</sub>2

| モジュール           | 演算性能<br>(GOPS) | 消費電力 (W)<br>電源電圧1.1 V,<br>25 ℃の場合 | 消費電力当たり<br>の演算性能<br>(GOPS/W) |

|-----------------|----------------|-----------------------------------|------------------------------|

| メディアプロセッシングエンジン | 46.8           | 0.1206                            | 388.1                        |

| アフィン変換アクセラレータ   | 10.6           | 0.1082                            | 98.4                         |

| HOGアクセラレータ      | 25.5           | 0.1302                            | 196.1                        |

| ヒストグラムアクセラレータ   | 5.3            | 0.0420                            | 126.7                        |

| フィルタアクセラレータ     | 230.4          | 0.2931                            | 786.2                        |

| マッチングアクセラレータ    | 145.2          | 0.0546                            | 2659.3                       |

| 合計              | 463.9          | 0.7486                            | 619.7                        |

GOPS: Giga Operation per Second HOG: Histogram of Oriented Gradients

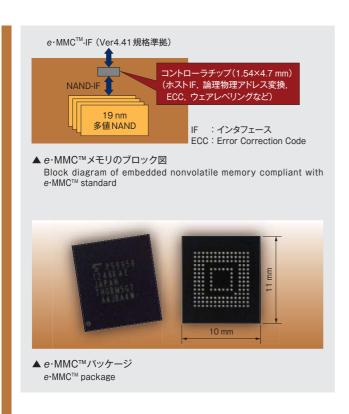

## ■ 19 nm 世代 NAND型フラッシュメモリを 搭載した高性能・小型e・MMC™メモリ

$e \cdot \text{MMC}^{\text{TM}}$ は、スマートフォンやタブレットなどに組み込まれる不揮発性メモリとして急速に市場が拡大している。今回、新開発の高性能コントローラと、19 nmプロセスを用いた世界最小 $^{(注)}$ チップサイズの64 Gビット及び32 GビットNAND型フラッシュメモリ(多値2ビット/セル)を多段積層した、小型で高性能の $e \cdot \text{MMC}^{\text{TM}}$ メモリを開発した。

コントローラ内のMPU (Micro Processing Unit) ファームウェアのアルゴリズムを工夫し、コントローラのチップサイズやコストを抑えながら、性能を大幅に向上させている。特にスマートフォンなどの操作性や使い勝手に大きく影響するランダム書込み速度は、24 nm世代の製品に比べて4倍以上と業界トップクラスの高い性能を実現した。

また、 $16 \sim 64$  Gバイトの大容量ながら、 $11 \times 10$  mmや  $11.5 \times 13$  mmなどの小型パッケージをラインアップしている。

(注) 2012年11月現在, 当社調べ。

(セミコンダクター& ストレージ社)

# ■ 高性能・低消費電力画像認識プロセッサ Visconti<sub>™</sub>2

近年、侵入者を検知し自動通報する監視カメラや、自動車事故を未然に防ぐ先進運転支援システムなどカメラベースのセンシング技術を応用した製品が急速に拡大している。特に人を検知するには、膨大な計算をリアルタイムに行う高い並列演算性能が必須であり、これらの機器は高温下でも低消費電力が求められる。

今回、低消費電力のマルチコアと画像処理アクセラレータ群を搭載することで、人や車両などの複数の対象を同時に検知する高い画像処理性能を、組込み機器で使用可能な低消費電力で実現した画像認識プロセッサVisconti<sub>TM</sub>2シリーズを開発した。最大4台までのカメラ映像をリアルタイムに処理できる。

サンプル並びにソフトウェア開発キットをリリース中であり、また順次ラインアップもそろえるなど、更なる市場ニーズに応えていく。

関係論文: 東芝レビュー. 67, 10, 2012, p.25-28.

(セミコンダクター& ストレージ社)

# ▲ TL1F1シリーズ (フラットトップタイプ) TL1F1 series flat-top type white light-emitting diode (LED) lamp

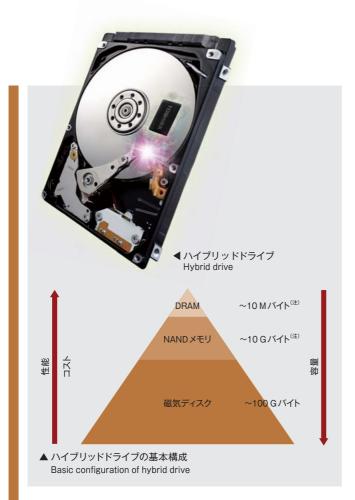

### ■ 新コンセプトのストレージ ハイブリッドドライブ

1 Tバイト<sup>(注)</sup>の記憶容量を持つ2.5型 HDD (ハードディスクドライブ) に、キャッシュメモリとして8 GバイトのNAND型フラッシュメモリを搭載し、大容量と高性能を両立したハイブリッドドライブ MQ01 ABD100H などを開発した。

ユーザーのデータアクセスパターンを動的に学習するアルゴリズムにより、データをDRAM、NAND型フラッシュメモリ、及び磁気ディスクの3層の記憶デバイスに適正配置し、使用頻度の高いデータをNAND型フラッシュメモリに保持することで、読出しの高速化を実現した。

PC (パソコン) に適用する場合、例えばアプリケーション起動時間では約40%の短縮が可能である。また、従来の2.5型 HDD と形状及びインタフェースが同じことから置換えが可能で、既存システムのパフォーマンス向上に貢献できる。

(注) Mバイトは10°バイト、Gバイトは10°バイト、Tバイトは10<sup>12</sup>バイトで計算。関係論文:東芝レビュー、67,9,2012、p.37-40.

(セミコンダクター&ストレージ社)

# ■ GaN-on-Si LED素子を採用した 白色LEDランプ

家庭やオフィスなどの照明に使用される1Wタイプの白色LED(発光ダイオード)ランプを開発した。当社が米国ブリッジラックス社と共同開発した白色用LED素子を搭載し、業界の標準的なパッケージをラインアップした。

窒化ガリウム (GaN) 層をシリコン (Si) 基板にエピタキシャル成長させた白色用LED素子の採用により、LEDで主流のサファイア基板に比べ材料コストを抑えた。また、当社の高い製造技術の活用により、LED業界最大(注)の直径200 mmの大口径ウェーハでの量産を実現した。これらを組み合わせることで、直径50~100 mmのサファイア基板を用いる場合に比べ、大幅なコスト削減を実現した。

更に、電球、直管、及びシーリングライト用の0.2~0.6 W の低電力タイプの開発・製品化も進めており、より広範な 照明セットに対応した白色 LED ランプの展開を進めている。

(注) 2012年12月現在, 当社調べ。

(セミコンダクター&ストレージ社)

# HIGHLIGHTS 2012

# 電子デバイス

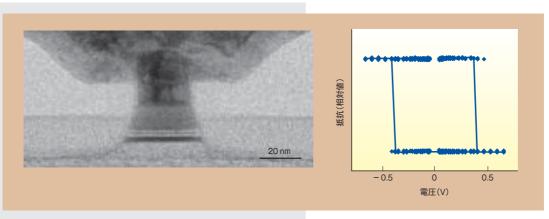

# ▲ 新たに開発した p-STT-MRAM 素子の電子顕微鏡写真と素子特性 Electron microscope image and typical memory characteristics of newly developed perpendicular spin-transfer torque magnetoresistive random access memory (p-STT-MRAM)

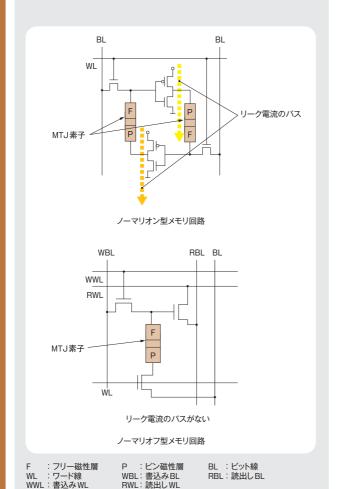

▲ 従来のノーマリオン型メモリ回路と新たに開発したノーマリオフ型 メモリ回路

Conventional normally-on and newly developed normally-off type memory circuits

# ■ プロセッサの消費電力を削減する 高速・低消費電力MRAM

スマートフォンやタブレットなどに搭載されるモバイルプロセッサでは、キャッシュメモリ容量が年々増大する傾向にあり、それに伴って消費電力が増大している。そこで当社は、大容量不揮発性メモリとして、垂直磁化方式の磁性体メモリ(p-STT-MRAM:perpendicular-Spin Transfer Torque-Magnetoresistive RAM)を開発した。

当社は、2007年に世界で初めてp-STT-MRAMの開発に成功し、その後もこのメモリ技術の開発をリードしている。今回、メモリ素子構造を改良し、素子サイズを30 nmに微細化することで、従来困難であった、高速処理性能と低消費電力動作の両立を実現し、プロセッサのキャッシュメモリとして使えることを示した。これにより、動作時の電力消費エネルギー量を従来の約1/10に低減することができた。更に、メモリ部のリーク電流パスがないノーマリオフ型メモリ回路を導入し、待機時だけでなく動作時のリーク電流も削減した。

電力評価用に開発したp-STT-MRAMをキャッシュメモリとして搭載したプロセッサシミュレータにより、標準的なモバイル向けプロセッサと比べて消費電力が1/3程度に低減することを確認した。従来のMRAM技術では動作時の消費電力が大きいためプロセッサ消費電力は逆に増大する結果となっており、低減を確認したのは世界初(注)である。今後、プロセッサ消費電力を1/10以下にすることを目指して開発を進める。

(注) 2012年12月, International Electron Devices Meeting (IEDM) 2012で発表。

(研究開発センター)

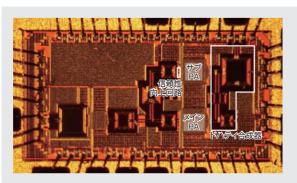

▲ 2.4 GHz 1.1W CMOS ドハティ PA 2.4 GHz 1.1 W complementary metal-oxide semiconductor (CMOS) Doherty power amplifier

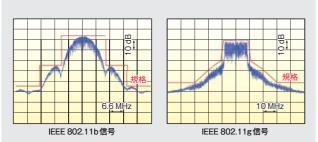

▲ IEEE 802.11b/g 無線 LAN 信号増幅時の出力スペクトル Output spectra of wireless LAN (IEEE 802.11b/g) signals

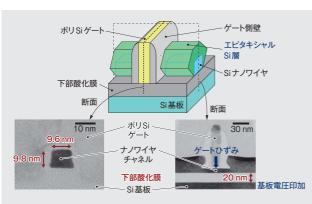

▲ 10nm径ナノワイヤトランジスタの模式図と断面電子顕微鏡写真 Schematic and cross-sectional electron microscope images of 10 nmdiameter nanowire transistor

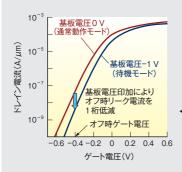

# ■ 10 nmナノワイヤトランジスタの電流 - 電圧特性

Current-voltage characteristics of 10 nm-diameter nanowire transistor

### ■ 1 W級CMOSドハティパワーアンプ

携帯端末向けRF (Radio Frequency) パワーアンプ (PA) では、小型・低コスト・高機能化のためCMOS (相補型金属酸化膜半導体) 化が求められているが、出力電力及び電力効率に課題があった。そこでメインPA、サブPA、及び合成器から成り、低出力時にサブPAをオフして電力効率を改善するドハティPA技術を高出力仕様に対応させてCMOS PAに適用し、出力電力1 W 級 2.4 GHz帯 CMOS ドハティPAを開発した。

今回,65 nm CMOSプロセスで開発したドハティ合成器は、素子間の磁界干渉抑制を図り、従来の1/2以下の合成器面積で、CMOSドハティPAとしては世界最高(注)の最大出力1.1 Wと、無線LANでの指標となる出力電力6 dB低減時の電力付加効率23%を達成した。また微細・低しきい値CMOSプロセスのドハティPAで問題になるデバイス信頼性の低下を軽減する回路も開発し、IEEE(電気電子技術者協会)規格の802.11b(無線LAN)信号での理論動作寿命を約75%向上させる見積結果を得た。

(注) 2012年6月, 2012 IEEE Symposium on VLSI Circuitsで発表。

(研究開発センター)

# ■ 超低消費電力LSI向け 10 nmナノワイヤトランジスタ

超低消費電力LSIの実現に向けて、直径10 nmのSiナノワイヤトランジスタを開発した。

ナノワイヤ径を10 nmまで小さくすることにより、ゲートの支配力を高め、オフ時のリーク電流を大幅に抑制した。また、ソース及びドレインのSiエピタキシャル成長とゲートひずみ技術の導入により、従来の小ナノワイヤ素子で問題となったオン時の駆動電流劣化を抑制し、消費電力低減と高性能動作の両立を実現した。

更に、下層酸化膜を20 nmまで薄膜化したナノワイヤトランジスタに基板電圧を印加することにより、LSI待機モード (携帯電話の待受時など、LSI回路の動作頻度が少ない状態) 時の消費電力を1桁低減することにも成功した。

この研究の一部は、独立行政法人 新エネルギー・産業 技術総合開発機構 (NEDO) プロジェクト「ナノエレクトロ ニクス半導体新材料・新構造ナノ電子デバイス技術開発」 の委託を受けて実施した。

関係論文: 東芝レビュー. 67, 11, 2012, p.41-44.

(研究開発センター)