# 般論文

# 19 nm世代のNANDフラッシュメモリを用いた クライアントSSDを実現する高性能コントローラ技術

High-Performance Control Technologies for SSD Using 19 nm-Generation NAND Flash Memory for PC Market

浅野 滋博 大嶋 貴志 小山内 建樹

■ ASANO Shigehiro ■ OSHIMA Takashi ■ OSANAI Take

SSD (ソリッドステートドライブ) は記憶メディアにNANDフラッシュメモリ (以下, NANDメモリと略記) を使用しているため, HDD (ハードディスクドライブ) に比べて, 高速データ読出し, 耐衝撃性, 低消費電力など優れた特長を持つが, 容量単価が高いことが普及を妨げている。 したがって, 今後よりいっそうの普及を目指すためには, 更なる微細化による容量単価の低減が不可欠であるが, NANDメモリでは微細化に伴ってデータ転送速度や信頼性の低下を招くおそれがある。

そこで東芝は、これらを解決する高速化技術、誤り訂正技術、及び低消費電力化技術を搭載した高性能コントローラを開発し、最先端プロセスである19 nm世代のNANDメモリを用いたクライアントSSDを実現した。

Solid-state drives (SSDs) using NAND flash memory have several advantages, including higher speed data readout, higher shock resistance, and lower power consumption, compared with hard disk drives (HDDs). As the capacity of SSDs per unit cost still remains lower than that of HDDs, increased capacity per unit cost with the shrinkage of the manufacturing process for NAND flash memory is essential for the dissemination of SSDs in the mainstream PC market.

In keeping with this trend, Toshiba has now developed an SSD using its leading-edge 19 nm-generation NAND flash memory for the PC market. To overcome the degradation of reliability and data transmission speed resulting from miniaturization, we have newly developed an SSD controller incorporating an advanced error correction function, a parallel data processing function, and energy-saving functions.

#### 1 まえがき

近年、半導体プロセスの微細化をけん引している原動力はNANDメモリである。東芝は19 nm世代のNANDメモリの量産を既に開始し、このNANDメモリを記録メディアとして採用した様々なSSDを開発している。SSDはHDDに比べて、小型軽量、高速データ読出し、耐振動性や耐衝撃性、低消費電力などの優れた特長を持っている。特に、モバイル用途においていっそうの普及が期待されているが、そのためには微細化の進展による容量単価の低減が不可欠である。しかし微細化に伴って、NANDメモリの信頼性やデータ転送速度の低下が予想されるため、SSDにはこれらの課題を解決するシステムレベルの高性能コントローラ技術が要求される。

そこで当社は、高速化のための並列化技術、強力な誤り訂正能力を持つECC (Error Correcting Code)、及び低消費電力化技術を搭載した高性能コントローラを開発した。ここでは、19 nm世代のNANDメモリを用いたクライアントSSDを実現するこれらのコントローラ技術について述べる。

# 2 コントローラのアーキテクチャ

今回開発したコントローラは、SATA (Serial Advanced Technology Attachment) Generation-3をホストインタフェー

表 1. コントローラ諸元

Specifications of SSD controller

| 項目           |            | 仕 様                        |

|--------------|------------|----------------------------|

| ホストインタフェース   |            | SATA 6 Gビット/s (Gen-3)      |

| NANDフラッシュメモリ |            | 19 nm MLC, toggle2         |

| NANDインタフェース  |            | 8チャネル, 4インタリーブ             |

| 性能           | シーケンシャルリード | 520 Mバイト/s (4 Kバイトアクセス時)   |

|              | シーケンシャルライト | 320 M バイト/s (4 K バイトアクセス時) |

|              | ランダムリード    | 75 k IOPS (4 K バイトアクセス時)   |

|              | ランダムライト    | 30 k IOPS (4 K バイトアクセス時)   |

| プロセス         |            | モバイル用40 nm, 7層配線           |

|              |            |                            |

MLC: Multi Level Cell IOPS: Input Output per Second

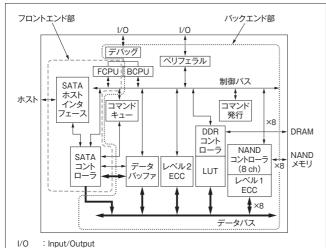

スとするSSDコントローラである。その諸元を**表1**に, ブロック図を**図1**に示す。

このコントローラは、SATAホストインタフェース及びSATAコントローラから成るフロントエンド部と、NANDメモリへのアクセスを含めたコマンド実行処理を行うバックエンド部に大別される。CPUをフロントエンド部とバックエンド部それぞれに1個ずつ設けたマルチプロセッサ構成を採用して、並列化による高速化を図っている。バックエンド部には、フロントエンド部からのコマンドを複数蓄積するコマンドキュー、及びデータのバッファリングを行うデータバッファがある。コマンドキューはSATAインタフェースで既定されているNCQ (Native Com-

FCPU: Front-end CPU BCPU: Back-end CPU ch: チャネル

図1. 開発したコントローラのブロック図 — コントローラは、複数のプロセッサ、ハードウェアエンジン、NANDメモリへのインタフェース、及びホストへのインタフェースがバスで結合された構造を持っている。

Block diagram of SSD controller

mand Queueing)を用いて高速化を図る仕組みであり、複数のコマンドを受け付けて順不同でそれらの処理を行う。データバッファはホストからのアクセスとNANDメモリの速度をマッチングさせる役割や、複数のデータをまとめてNANDメモリに書き込む役割などを持つ。

LBA (Logical Block Address: 論理アドレス) とNANDメモリの物理アドレスの関係を管理するLUT (Look Up Table)は、コントローラ外部に接続されたDRAMに格納されたアドレス管理テーブルにアクセスするため、DDR (Double Data Rate) コントローラを内蔵している。NANDメモリにアクセスするためのNANDコントローラは、19 nm世代のMLC (Multi Level Cell)型NANDメモリ及びtoggle2インタフェースに対応し、データ転送のバンド幅を向上させるために8チャネル及び4インタリーブをサポートした。NANDコントローラはレベル1 ECC ブロックを内蔵し、NANDメモリに格納されるデータを保護する。また、レベル2 ECC ブロックをNANDコントローラ外に設けている。これらECC ブロックの動作については4章で述べる。

ここで、LBAとNANDメモリのアドレスを必ずしも一致させることなく、LBAとNANDメモリのアドレス間にマッピング関係を構築する理由について述べる。一般にLBAのアクセスパターンは必ずしも均一ではないため、もしLBAとNANDメモリのアドレスを一致させると、特定のLBAだけに書き込むようなケースでは、その部分に対応するNANDメモリ部分だけ書込み回数が増えてしまう。NANDメモリの書込み回数は信頼性を確保するために上限が設けられており、特定のNANDメモリだけに書込みが集中することは望ましくない。そのた

めNANDメモリの書込み回数を全体的に均一化するウェアレベリングと呼ばれる手法を実行する。ウェアレベリングを行うには、LBAとNANDメモリの間にマッピング関係を構築する LUTが必要となるためである。

次に、基本的なリード及びライト処理の流れについて述べる。ホストからのSATAリード系コマンドは開発したコントローラのフロントエンド部を経由してコマンドキューに送られる。コマンドキューに入ったリード系コマンドはLUTに送られて、LBAで指定されたリードアドレスがNANDメモリの物理アドレスに対応付けられる。その後、リードコマンドは、物理アドレスに対応した適切なチャネルのNANDコントーラに送られてデータを読み出す。そしてリードデータはデータバッファに転送された後、フロントエンド部を経由してホストへ送られる。

また、ホストからのライトでは、フロントエンド部を経由して、ライトデータ、LBA、及びデータ属性がデータバッファに送られる。次に、LUTにLBAとNANDメモリの物理アドレスの対応情報が設定され、データバッファからNANDメモリに書き込まれる。また、レベル1ECC及びレベル2ECCはこのとき生成され、ライトデータとともにNANDメモリに書き込まれる。

# 3 高速化技術

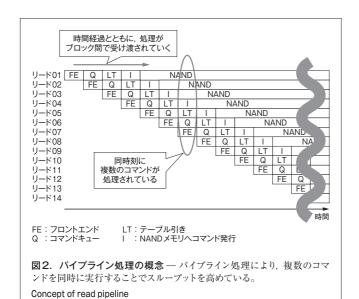

SATA Generation-3に準拠したデータ転送速度を実現するため、開発したコントローラのコマンド処理をパイプライン化した。すなわち、コントローラの処理を内部ブロックに分割するにあたり、その処理内容を整理し、前段から後段に向かって、ブロック間でコマンドを受け渡していくブロック定義を行った。その際、ブロックに割り付ける処理量をほぼそろえるように配慮した。各ブロックの入出力部に内部バッファを設けることにより、あるコマンドの処理を終了したブロックは後段のブロックにそのコマンドを受け渡し、前段のブロックから別のコマンドを受け取って処理を開始するように動作する。これにより、各ブロックは同時に互いに別々のコマンドを処理することになり、全体としては複数コマンドが並列処理される。パイプラインの概念を図2に示す。図2では、複数のリードコマンドが間断なく処理されることがわかる。

コマンドのパイプライン処理の実行は、SATAのNCQにより、一つのSATAコマンドの実行が終了する前に、ホストから次のSATAコマンド発行が許されることによって行われる。

これにより、このコントローラでは、4 K バイトアクセス時に、シーケンシャルリード 520 M バイト/s、シーケンシャルライト 320 M バイト/s、ランダムリード 75 k IOPS(Input Output per Second)、及びランダムライト 30 k IOPS という高い性能を実現している。

#### 4 信頼性向上技術

NANDメモリに格納されたデータの信頼性を確保するためにレベル1及びレベル2の誤り訂正機能を設けており、誤り検出時には、まず低レイテンシであるレベル1での誤り訂正を試み、次に訂正不能だった場合にだけレイテンシの大きいレベル2の誤り訂正を実施する。

微細化が進んだDRAMはソフト誤りの問題があるとされており<sup>(1)</sup>,信頼性確保のためにブロック符号によるワード単位でのデータ保護機能のほか、一定サイズのブロック単位でマトリクス状に配置されたパリティビットを用いて誤りビットを特定して誤りを訂正する。このような手法をとることで、誤り訂正符号によるDRAMの使用率低下を抑えながらも高い信頼性を確保した。

コントローラ内のSRAMに対してもワード単位でECCを付

ボスト

データ CRC

SATA ホストインタフェース

データ CRC E3D

SATA コントローラ

データ E3D

データ E3D

NAND コントローラ

STructure of end-to-end error detection (E3D) coding

加し、誤り発生の検出と訂正を行う機構を設けた。

ユーザーデータに関しては、End to EndのError検出 (E3D) 符号を付加し、データ読出し機能を設けて、データ転送の過程で発生する誤りを検出可能とし、誤りのあるユーザーデータを外部に出力することがないようにしている。E3D符号の付加プロセスを図3に示す。

# 5 低消費電力化技術

性能向上に伴う消費電力の増加を抑えて低消費電力化を図るため、次の技術を導入した。

コントローラ設計では、スタンバイ時のリーク電流を低減するためにHigh Vthセルの使用を基本とするとともに、各ブロックや機能ごとに個別のクロックゲートを用意して未動作の回路を極力小さな単位で停止できるようにした。またシステム全体を低消費電力状態にする場合には、PLL (Phase Locked Loop)動作自体を止めることも可能にした。

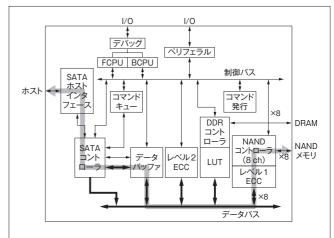

更にデータ転送時は、**図4**に示すように、ユーザーデータが DRAMを経由することなく内部バッファだけを介してNAND メモリとの間でデータ転送を行うアーキテクチャを採用した。これによって、DRAMコアの消費電力及びDRAMインタフェースの消費電力を抑えることができる。

NANDメモリインタフェースに関しては専用PLLを搭載し、その設定はコントローラファームウェアから制御できる。SSDシステムと搭載NANDメモリの特性に応じてインタフェース速度を制御することで、性能と消費電力のトレードオフを改善することが可能である。

SSDシステムとしては、スタンバイ時の消費電力低減を図るためにDRAMやNANDメモリといったSSDを構成するチップに供給する電源の遮断制御機能を設けており、SSDスタン

図4. ユーザーデータの転送経路 — DRAMを経由しないユーザーデータの転送経路により、低消費電力化を図っている。

User data path in SSD controller

バイ時に動作不要なコントローラ周辺チップも含めて消費電力 を抑えられる。

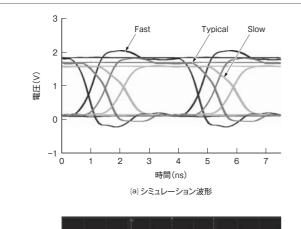

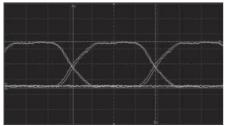

#### 6 伝送路設計

NANDインタフェースのDDR対応に伴い、64 Gバイトモデルから1 T (テラ: $10^{12}$ ) バイトモデルまでの伝送路シミュレーションを実施しており、DDR動作において問題がないことを確認した。また、伝送路のシミュレーション波形と実測波形がよく一致していることを確認した( $\mathbf{図5}$ )。

# 7 LSIの実装

開発したコントローラは40 nm世代のモバイル用途向けのスタンダードセル設計であり、配線層として7層を使用している。5章で述べたとおり、リーク電流の少ないHigh Vthセルを基本としながら、タイミングが厳しいパスだけしきい値電圧Vthを下げた高速なセルを使用している。

40 nm世代のプロセスの大規模設計では配線遅延が問題となる。長距離配線が集中するバスマトリックスに少し多めにフリップフロップを配置して配線を分割することで遅延を減らし、レイアウト時の自動配置配線の自由度を上げている。

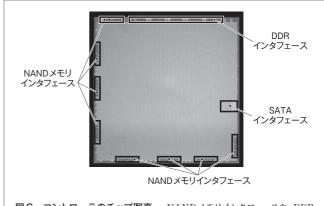

開発したコントローラのチップ写真を図6に示す。チップの

(b) 実測波形

**図5. 伝送路のシミュレーション波形と実測波形** — NAND 伝送路のシミュレーション波形と実測波形は、よく一致していることを確認した。

Results of simulation and measurement of NAND transmission line signal waveforms

図6. コントローラのチップ写真 — NANDメモリインタフェースや、DDR インタフェース、SATAインタフェースなどを外周部に配置している。

SSD controller chip

3辺を8チャネルのNANDメモリインタフェースとDDRインタフェースが占有している。

#### 8 あとがき

ここでは、19 nm世代のNANDメモリに対応した高速化のための並列化技術、信頼性向上技術、及び低消費電力技術について述べた。今回開発した技術をベースに、今後の微細化には更なる誤り訂正能力の強化などが求められる。更に、現在ホストシステムとの接続にはSATAインタフェースを用いているが、今後いっそうの高速化に対応するためSATA以外のインタフェースについても検討を行っている。

#### 文 献

(1) Shroeder, B. et al. "DRAM erros in the wild: a large-scale field study". Proceedings of the eleventh international joint conference on Measurement and modeling of computer systems (SIGMETRICS '09). Seattle, WA, USA, 2009-06, ACM. New York NY, USA, ACM, 2009, p.193 - 204.

#### 浅野 滋博 ASANO Shigehiro

研究開発センター コンピュータアーキテクチャ・セキュリティ ラボラトリー研究主幹。マルチプロセッサ及びSSDの研究・ 開発に従事。IEEE会員。

Computer Architecture & Security Systems Lab.

#### 大嶋 貴志 OSHIMA Takashi

セミコンダクター&ストレージ社ストレージプロダクツ事業部ストレージプロダクツ設計生産統括部参事。SSDコントローラLSIの設計に従事。

Storage Products Div.

#### 小山内 建樹 OSANAI Takeki

セミコンダクター&ストレージ社ストレージプロダクツ事業部ストレージプロダクツ設計生産統括部参事。SSDコントローラLSIの設計に従事。

Storage Products Div.