# 直径 10 nm のシリコンナノワイヤを備えた 超低消費電力 LSI用トランジスタ

Silicon Nanowire Transistor with Nanowire Diameter of 10 nm for Ultralow-Power LSIs

太田 健介 田中 千加 齋藤 真澄

■ OTA Kensuke

■TANAKA Chika

■ SAITOH Masum

近年, 超低消費電力LSI用としてナノワイヤトランジスタに注目が集まっている。ゲート支配力が大きいため, オフ時のリーク電流(以下, オフ電流と略記)を抑制でき, ナノワイヤ径が小さいほどその抑制力が高まる。しかし, 細線中を電流が流れるため, オン時の駆動電流(以下, オン電流と略記)が小さく, 回路の動作速度が遅くなってしまうという問題があった。

東芝は、直径10 nmのトライゲートナノワイヤトランジスタを作成し、オフ電流抑制と高性能動作を両立できることを実験的に示した。ソースやドレインの最適化とひずみ技術によって、寄生抵抗の低減と移動度向上を実現し、高いオン電流を達成した。一方、ナノワイヤトランジスタ下の埋込み酸化膜を薄膜化し、基板に電圧を印加することによってしきい値調整ができることを実証した。更に、基板電圧を用いたしきい値調整を用いて、消費電力と性能の動的な制御が可能であることを示した。

Nanowire transistors have been attracting considerable attention in recent years as a solution for the realization of ultralow-power large-scale integrations (LSIs). Off-leakage current can be suppressed in a nanowire transistor due to its strong gate controllability. However, low circuit speed because of degradation of the on-current, due to the fineness of the wire through which the current flows, is a crucial issue.

Toshiba has developed a silicon nanowire transistor with a nanowire diameter of 10 nm, which achieves high on-current both by reducing parasitic resistance through optimization of the cross-sectional areas between the source and the drain, and by enhancing channel mobility through a stress memorization technique (SMT) process. Experiments on a prototype have verified the balance between suppression of off-leakage current and high performance. We have also demonstrated threshold voltage control in a tri-gate nanowire transistor with a thin buried oxide, and have confirmed that management of the dynamic power and performance can be attained by using the substrate bias for threshold voltage control.

### 1 まえがき

LSIの基本構成要素であるMOS (金属酸化膜半導体)トランジスタは、ゲート長の縮小 (スケーリング)により、集積度の向上、動作電圧の低減、及び動作速度の向上を実現してきた。しかし近年、過度なスケーリングによるオフ電流と、それによる消費電力の著しい増大が問題となっている。この問題を解決するため、トランジスタ構造を従来の平面型から立体型に変更した立体構造トランジスタが盛んに研究されている(1)。なかでも、細線形状のシリコンを用いるシリコンナノワイヤトランジスタは、究極のトランジスタ構造として期待されている。

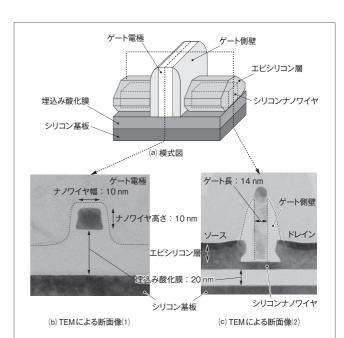

ナノワイヤトランジスタの模式図を**図1**(a)に示す。電流が流れる細線シリコン (ナノワイヤ)上にゲート電極がかかっており、ゲートの両側にソース・ドレイン領域が形成されている。ゲートがナノワイヤを上面と左右側面から覆うためにゲートの電気的な支配力が強く、オフ電流を強力に抑制できる。ナノワイヤの直径を小さくするほどゲート支配力が大きくなり、リーク電流をよりいっそう抑えることができる。

このようにナノワイヤトランジスタはオフ電流が小さい一方で、オン電流が小さくなり、回路の動作速度が低下するという問題があった。特にナノワイヤ径が小さい直径10 nmのナノワ

図1. ナノワイヤトランジスタの模式図と透過型電子顕微鏡 (TEM)による断面像 — 直径10 nmのナノワイヤをゲートが3方向から覆うことでオフ電流を抑制する。ソース及びドレインはエピタキシャル成長により断面積を増やすことで、寄生抵抗を低減する。

Schematic and transmission electron microscope (TEM) images of nanowire transistor

イヤトランジスタでは、細線状のソース及びドレインの巨大な 寄生抵抗とゲート下のチャネル領域の移動度低下のため、オン 電流が小さくなるという問題があった。

また、従来トランジスタではシリコン基板に電圧を加えること(基板バイアス)によって、しきい値電圧を調整するという手法が使われてきたが、ナノワイヤトランジスタはナノワイヤ下に厚い埋込み酸化膜が存在するため、ナノワイヤ部分に電界がかかりにくく、この手法はほとんど試されてこなかった。

東芝は、ナノワイヤトランジスタのソース及びドレインにシリコンをエピタキシャル成長させ(以下、成長させたものをエピシリコンと呼ぶ)、寄生抵抗を低減し、ひずみによりチャネル移動度を向上させることで、オン電流向上を実現する技術を開発した。また、ナノワイヤトランジスタとしてはしきい値電圧を調整するのに十分な大きさのしきい値電圧の変化を基板バイアスによって実現した。

## 2 ナノワイヤトランジスタの作成方法

ナノワイヤトランジスタの作成には酸化膜上にシリコン層を 形成したSOI (Silicon-on-Insulator)基板を用いた。厚さ 20 nmの埋込み酸化膜上にリソグラフィとドライエッチングによ り、シリコンナノワイヤを形成した。ゲート酸化膜の二酸化ケ イ素 (SiO<sub>2</sub>) を形成後、ポリシリコンのゲート電極を堆積した。 ゲート加工後、ゲート側壁両側のソース・ドレイン領域で、選 択的にシリコンをエピタキシャル成長させた。エピタキシャル 成長によりソース・ドレイン領域の断面積が増加することで、 寄生抵抗の低減が可能になる。

当社で作成した直径10 nmのナノワイヤトランジスタの透過型電子顕微鏡(TEM)による断面像を図1(b), (c)に示す。厚さ20 nmと薄い埋込み酸化膜上に直径10 nmナノワイヤトランジスタが形成されていることがわかる。

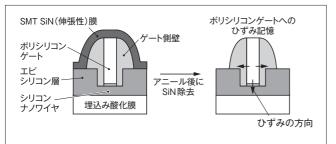

当社はゲート下のナノワイヤ中の移動度を向上させるため、 ひずみ技術を用いた。この技術で使用するひずみ印加は、 SMT (Stress Memorization Technique) という手法を用い

図2. SMTプロセスの概略 — SiN膜の堆積とアニールによってナノワイヤへひずみを印加する技術で、最終的にはSiN膜を除去するため完成構造は変わらない。

Outline of SMT process

た。図2に示すように、ナノワイヤトランジスタを覆うようにシリコン窒化 (SiN) 膜を堆積させる。続いて、1,000 ℃程度の高温でアニール (熱処理) を行う。このアニール中にはゲートポリシリコンの結晶化に伴う体積膨張が上部 SiN 膜によって抑制されるため、ゲート電極からナノワイヤを圧縮するひずみが発生する。この後 SiN 膜を剝離すると、ナノワイヤトランジスタは SMTを用いない場合と比べてデバイス構造は変わらないが、ポリシリコンゲート中に発生したひずみは残存するため、仕上がったナノワイヤトランジスタにはひずみが加えられた状態となる。

## 3 ナノワイヤトランジスタの動作性能

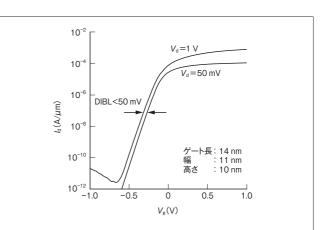

直径 10 nmのナノワイヤトランジスタにおけるドレイン電流  $(I_d)$  – ゲート電圧  $(V_g)$  特性の測定結果を図3に示す。14 nm という短いゲート長でも,ほぼ理想的なトランジスタ動作が実現できている。リーク電流が多い場合,ドレイン電圧  $(V_d)$  が  $1 \text{ V} \succeq 50 \text{ m} \text{V}$ のしきい値に差が出る。このしきい値の差を DIBL (Drain Induced Barrier Lowering) と呼ぶ。この値が小さいほどオフ電流が少なく,理想的なトランジスタ動作と言える。図3の特性から $V_d$  1 V 当たりのしきい値の差が 50 m V 以内と非常に小さいDIBLであることがわかる。すなわち,ナノワイヤ径を10 nm と細くしたことで,ゲート支配力が強くなり,オフ電流を抑制できるようになったことが示された。

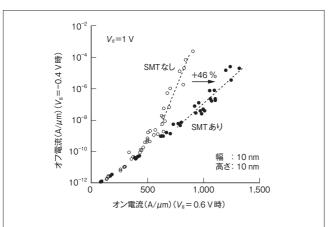

SMTプロセスを適用した場合と適用しなかった場合のオン電流 – オフ電流特性の測定結果を**図4**に示す。オン電流とオフ電流はそれぞれ $V_g$ が0.6 Vと-0.4 Vのときの $I_d$ である。SMTプロセスを適用すると,同一オフ電流で比べたときのオン電流が46%も向上していることがわかる。SMTによって,シリコンナノワイヤへ垂直方向の圧縮ひずみが印加される。こ

図3. ゲート長14 nmでのナノワイヤトランジスタの $I_{\rm d}$ - $V_{\rm g}$ 特性 — ナノワイヤの直径を $10~{\rm nm}$ まで細くすることで、オフ電流が抑制され、 $50~{\rm mV}$ 以内という非常に小さいDIBLが実現された。

Drain current vs. gate voltage characteristics of 14 nm-gate-length nanowire transistor

図4. ナノワイヤトランジスタのオン電流ーオフ電流特性 — オン電流と オフ電流は  $V_{\rm g}$  がそれぞれ 0.6  $\rm V_{\rm r}$  -0.4  $\rm V$  のときの  $I_{\rm d}$  である。SMT プロセス によってオン電流が 46 %向上する。

On-current vs. off-current characteristics of nanowire transistors with and without SMT process

れにより、シリコンナノワイヤ中の移動度が向上し、オン電流が向上したと考えられる。また、SMTによるオン電流向上には寄生抵抗が低減される効果も含まれていることが過去の実験から明らかになっている<sup>(2)</sup>。

これまで述べたように、ナノワイヤ径を10 nmと細くすることによるオフ電流の抑制、及びSMTによるオン電流の向上により、高性能かつ、超低消費電力動作が可能であることが示された。

## 4 基板バイアスによるしきい値電圧調整

ここでは、直径10 nmのナノワイヤトランジスタの基板バイアスによる。しきい値電圧調整について述べる。

シリコン基板に電圧を印加することで埋込み酸化膜に電界がかかり、ナノワイヤの電位を変化させることができる。これにより、しきい値電圧を調整できる。従来のナノワイヤトランジスタは埋込み酸化膜の厚さが100 nm以上あり、シリコン基板に電圧を印加しても電界がかかりにくく、十分なしきい値電圧調整ができなかった。当社は2章で述べたように、埋込み酸化膜厚を20 nmという薄さにすることによって十分な大きさのしきい値電圧を調整できることを検証した。

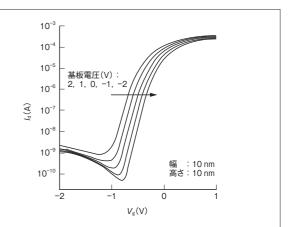

基板に印加した電圧を変化させたときの、ナノワイヤトランジスタの $I_{\text{d}}$ - $V_{\text{g}}$ 特性を**図5**に示す。基板に電圧を印加することによって $I_{\text{d}}$ - $V_{\text{g}}$ 特性がシフトしていることがわかる。すなわち、基板バイアスによるしきい値電圧変調が可能であることがわかる。

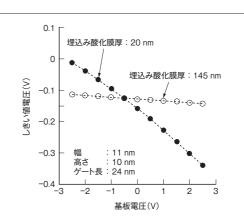

しきい値電圧変調を定量的に調べるために,しきい値電圧 - 基板電圧特性の測定結果を図6に示す。比較のために,埋 込み酸化膜が145 nmと厚い従来のナノワイヤトランジスタ特性も示す。従来の厚い埋込み酸化膜では基板電圧によってし

図5. 薄い埋込み酸化膜上のナノワイヤトランジスタにおける基板電圧 印加時の $I_{\rm d}$ - $V_{\rm g}$ 特性 — 基板電圧印加によってしきい値電圧の変調が可能 になる。

Drain current vs. gate voltage characteristics of nanowire transistors on thin buried oxide with various substrate voltages

図6. ナノワイヤトランジスタの基板電圧印加時のしきい値電圧-基板電圧特性 — 埋込み酸化膜を薄くすることで基板電圧印加によるしきい値電圧変調が大きくなる。

Threshold voltage vs. substrate voltage characteristics of nanowire transistor on thin buried oxide

きい値電圧を変調することがほとんどできないのに対し、今回 の薄い埋込み酸化膜では基板電圧を±1 V 印加することで、 ナノワイヤトランジスタのしきい値電圧を 0.1 V 以上も変調でき ることがわかる。

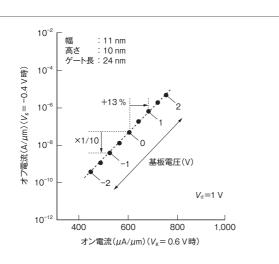

次に基板バイアスによるしきい値電圧調整が、オン電流-オフ電流特性に与える影響を考察する。基板電圧を-2 Vから2 Vまで変化させたときのオン電流-オフ電流特性の変化を図7に示す。基板電圧を1 V印加することで、13 %のオン電流を増加できる。又は、基板電圧を-1 V印加することで、オフ電流を1桁低下させることができる。オン状態とオフ状態において、それぞれ正と負の基板電圧を印加することで動的な消費電力と回路性能の最適化を行えることが示された。

図7. 薄い埋込み酸化膜上のナノワイヤトランジスタにおける基板電圧 印加時のオン電流ーオフ電流特性 — 基板電圧を1 V 印加することによってオン電流を13% 向上させることができ、-1 V 印加することによってオフ電流を1/10 に抑制できる。

On-current vs. off-current characteristics of nanowire transistors on thin buried oxide with various substrate voltages

レクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」で実施したものである。

## 文 献

- Bangsaruntip, S. et al. "High Performance and Highly Uniform Gate-All-Around Silicon Nanowire MOSFETs with Wire Size Dependent Scaling". Technical digest: International Electron Devices Meeting (Tech. Dig. IEDM.). Washington DC, USA, 2009-12, IEEE. 2009, p. 297 - 300

- (2) Saitoh, M. et al. "Understanding of Short-Channel Mobility in Tri-Gate Nanowire MOSFETs and Enhanced Stress Memorization Technique for Performance Improvement". Tech. Dig. IEDM. San Francisco, CA, USA, 2010-12, IEEE. 2010, p.780 - 783.

# 5 あとがき

直径 10 nmのナノワイヤトランジスタを作成し SMTによるひずみ印加を行った。ナノワイヤ径を小さくすることによるオフ電流の抑制と、ひずみによる高いオン電流を実現した。また、20 nmの埋込み酸化膜上に直径 10 nmのナノワイヤトランジスタを作成し、埋込み酸化膜を薄くしたことで基板バイアスによるしきい値電圧変化が大きくなるため、十分にしきい値電圧を調整できることを示した。更に、しきい値電圧調整によって、オン電流とオフ電流を制御できることがわかった。ここで述べたナノワイヤトランジスタは、動的制御が可能な超低消費電力LSIとして非常に有用である。

この研究の一部は、独立行政法人 新エネルギー・産業技術総合開発機構 (NEDO) から受託したプロジェクト「ナノエ

#### 太田 健介 OTA Kensuke, Ph.D.

研究開発センター LSI 基盤技術ラボラトリー,博士 (学術)。 ナノスケール MOSFET に関する研究に従事。応用物理学会 会員。

Advanced LSI Technology Lab.

#### 田中 千加 TANAKA Chika, Ph.D.

研究開発センター LSI 基盤技術ラボラトリー研究主務,博士 (理学)。ナノスケール MOSFETに関する研究に従事。応用 物理学会、日本物理学会会員。

Advanced LSI Technology Lab.

#### 齋藤 真澄 SAITOH Masumi, Ph.D.

研究開発センター LSI 基盤技術ラボラトリー研究主務,博士 (工学)。ナノ電子デバイス中のキャリア輸送に関する研究に 従事。IEEE,応用物理学会会員。

Advanced LSI Technology Lab.