# 無線通信LSIの低消費電力化技術

Low-Power-Consumption Driving Technologies for Wireless Communication LSIs

テー チェン コン 藤田 哲也 櫛田 桂一

■TEH Chen Kong

■ FUJITA Tetsuya

■ KUSHIDA Keiichi

近年の無線技術の発展に伴い、そこに使われる無線通信LSIの大規模化と高性能化が進み、消費電力も増大を続けている。 これらに使われる無線通信LSIはバッテリーを電源として動作するため、低消費電力化の技術が極めて重要になる。

この要求に応えるため東芝は、スイッチング電力とリーク電力それぞれの低減に有効な、低消費電力フリップフロップ(以下、FFと略記)とオンチップ電源制御の回路技術を開発し、無線LANベースバンドLSIやTransferJet™(注1) LSIなどの製品に適用した。また、更なる低消費電力化を目指して、SRAM (Static RAM)の低消費電力回路技術の研究開発も進めている。

Wireless communication technologies including Bluetooth<sup>®</sup> and wireless LAN have been widely utilized for smartphones and personal information devices in recent years. As wireless communication large-scale integrations (LSIs) are basically powered by the battery of the device, low-power-consumption driving technologies for these LSIs have become essential.

Toshiba has developed two technologies, low-power flip-flops and on-chip voltage control circuits, that effectively reduce switching power and leakage power, respectively. These technologies have been applied to our products including a wireless LAN baseband LSI and a TransferJet™LSI. In order to achieve further reductions in power consumption, we are also engaged in the research and development of circuit technologies for low-power static random access memories (SRAMs) used in LSIs.

# 1 まえがき

近年、Bluetooth®(注2)や無線LANといった無線通信技術が一般的となり、スマートフォンや携帯情報端末の通信手段として広く利用されるようになってきた。これに伴い、無線通信LSIの大規模化と高性能化が進み、消費電力も増加を続けている。無線通信LSIは、基本的にバッテリーを電源として動作するため、低消費電力化は、設計においてもっとも重要な課題となっている。これを実現するため、アーキテクチャレベルから回路、レイアウトレベルに至る様々な設計段階で、低消費電力化のための対策が行われている。

このうちアーキテクチャレベルでの対策がもっとも効果が大きく、無線通信LSIでは、通信を行っていないときに不要なブロックの動作を停止するモードを設け、電力の削減を図っている。また機能及び回路レベルでは、同等の機能を少ない回路規模で実現するための論理の最適化や、回路の不必要な動作を低減するためのクロックゲーティング技術が適用されている。更にレイアウトレベルでは、セル配置の最適化やトランジスタサイズの最適化による、負荷容量の低減で低消費電力化を行っている。

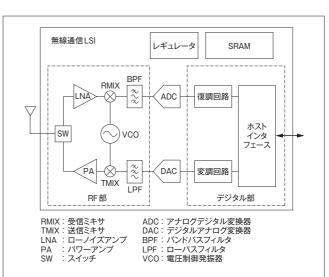

無線通信LSIの基本的な構成を図1に示す。RF (高周波

図1. 無線通信LSIの基本的な構成 — RF部や、デジタル部、レギュレータ、SRAMなどのブロックで構成される。

Block diagram of wireless communication LSI

回路) 部や、デジタル部、レギュレータ、SRAMなどで構成され、消費電力を低減するには、それぞれのブロックに応じた技術を適用する必要がある。

ここでは、無線通信LSIの低消費電力化を目指して東芝が開発している技術として、デジタル部の低消費電力化に効果がある低消費電力FFとオンチップ電源制御の回路技術、及びSRAMの低消費電力化技術、更にこれらを無線通信LSI

<sup>(</sup>注1) TransferJetは、一般社団法人 TransferJetコンソーシアムがライセンスしている商標。TransferJetは、ソニー(株)の商標。

<sup>(</sup>注2) Bluetooth は、Bluetooth SIG, Inc. の登録商標。

へ適用したときの効果について述べる。

# 2 低消費電力化技術

バッテリーで動作するLSIでは、動作時のスイッチング電力 削減と同様に、待機時のリーク電力削減が重要になる。 当社 は、スイッチング電力とリーク電力それぞれの削減に有効な低 消費電力FFとオンチップ電源制御の回路技術,及び低消費 電力SRAMを開発した。

## 2.1 低消費電力FF回路

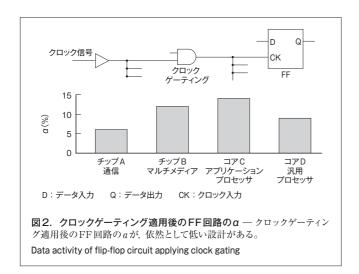

現在の同期設計を行うLSIでは、データを一時的に保持す るためのFF回路が大量に必要になり、スイッチング電力の半 分近くをクロック分配とFF回路で消費している。 そのため、 動作に関係しないFF回路へのクロック信号を停止するクロッ クゲーティング技術が広く用いられている。しかし、制御回路 のオーバヘッドを考えると、ある程度まとまった単位でFF回 路のクロック制御を行う必要があり、その場合、クロックゲー ティングを十分に行えないFF回路が増えていくと予想される。 いくつかの設計において、クロックゲーティングを適用した後 のFF回路のアクティブ率 $({}^{(\pm 3)}\alpha$ を、図**2**に示す。クロックゲー ティングを適用してもαが低い設計があり、FF回路自身の低 消費電力化も必要であることがわかる。

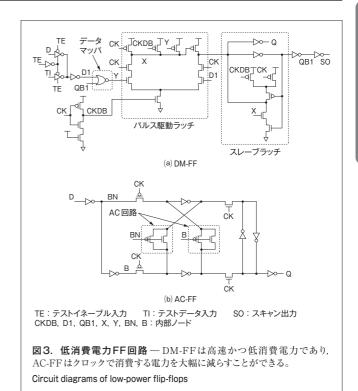

低消費電力化を図ったFF回路として, 当社は, DM-FF (DM: Data Mapping) 回路 (図3(a)) を開発した<sup>(1)</sup>。高速の パルス駆動ラッチをベースに、パルス駆動ラッチの欠点であっ たむだなプリチャージ遷移を、制御回路 (データマッパ)を追 加することで抑制し、標準的に用いられるTG-FF(TG: Transfer Gate) に比べ、25%高速でかつ20%の消費電力低 減 ( $\alpha = 0.1$ のとき) という性能を実現した。また、高速である ため低電圧化やFF以外の回路を小さくでき、更なる低消費電 力化を行える。

(注3) クロック変化に対するデータ変化の比。

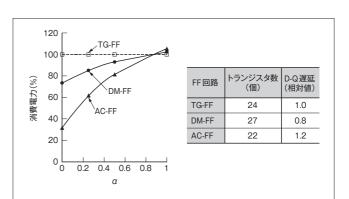

更に当社は、クロックが入力されることで消費する電力を大 幅に減らした AC-FF (AC: Adaptive Coupling) 回路 (図3(b)) を開発した<sup>(2)</sup>。AC-FF回路は、データ書込み時に、データ保 持側の能力を適性化し、書込みをアシストする当社独自のAC 回路を用いることにより, 従来はクロック信号で制御を行って いた回路を省略できる。この結果、クロック信号で動作するト ランジスタ数をTG-FFの12個から4個に減らせ、クロック入 力で消費する電力を大幅に削減できる。各FF回路のαに対 する消費電力 (相対値) の依存性を図4に示す。AC-FFは. TG-FFに比べて $\alpha = 0.1$ のときに60%の電力削減が行える。 また、D-Q遅延(注4)はAC-FFでは悪化するため、TG-FFや DM-FFと併用し、それぞれの長所を生かした設計を行うこと が望ましい。

図4. FF回路の消費電力及び遅延時間 — 消費電力の削減量はAC-FF が大きく、遅延時間はDM-FFが優れている。

Power consumption and delay time of each flip-flop

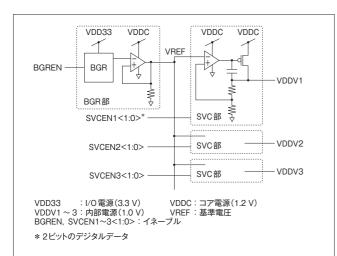

図5. オンチップレギュレータ回路 — 基準電圧を生成するBGR 部 及 び制御と出力を行うSVC部から構成され、ブロックの電源制御と電源遮

Block diagram of on-chip regulator circuit

#### 2.2 オンチップ電源制御回路

当社はまた、デジタル部電源の制御と遮断を行うためのオン チップレギュレータ回路を開発した。オンチップレギュレータ を搭載することにより、ブロックの性能に合った電源電圧を個 別に設定できるほか、電源電圧の変動も抑えられ、更にブロッ クを使用していないときには電源の供給を遮断することもでき るため、動作時のスイッチング電力と待機時のリーク電力をと もに削減する効果がある。

オンチップレギュレータの回路構成を図5に示す。基準電圧 を生成するBGR (バンドギャップ リファレンス) 部. 及び制御と 出力を行うSVC (サプライボルテージ コントローラ) 部から構成 される。SVC部は複数個を用い、電源制御を行いたいブロック それぞれの周辺に配置した。またBGR部は複数のSVC部が 共有するようにして、I/O (Input/Output) 領域に配置した。

レギュレータに加え、電源遮断専用のオンチップ電源スイッ チセルや、内部状態を保持したまま電源電圧を低下させて リーク電力の削減を行うためのリテンションレギュレータも実 用化した。実用化したオンチップ電源制御回路の主な仕様を 表1に示す。いずれも、きめ細かな電源制御を行うために重 要な回路技術である。

#### 2.3 低消費電力SRAM

無線通信LSIでは通信データ用バッファに多くのSRAMを 使用している。そのためSRAMには、高速動作と同時に低消 費電力の性能が求められる。当社はこの相反する課題を解決 するため、2電源駆動のSRAMを開発した。

2電源駆動 SRAMでは、SRAMセルアレーの電源を高電

クロック信号が入力されるより前に入力データを確定しておくのに必 (注4) 要なセットアップ時間と、クロック信号が入力されてからデータが出 力されるまでの遅延時間の合計。

#### 表 1. 実用化したオンチップ電源制御回路の主な仕様

Main specifications of newly developed on-chip voltage control circuits

| 項目             |      | レギュレータ         |                 | 電源スイッチ         |     | リテンション<br>レギュレータ |

|----------------|------|----------------|-----------------|----------------|-----|------------------|

| プロセス<br>テクノロジー | (nm) | 90             | 65              | 65             | 40  | 65               |

| 入力電圧           | (V)  | 1.2 ± 0.1      | 1.8 ± 0.2       | 1.2            | 1.1 | 1.2 ± 0.1        |

| 出力電圧           | (V)  | 1.0 ± 0.05     | 1.2 ± 0.1       | 1.2            | 1.1 | $0.8 \pm 0.08$   |

| 出力電流           | (mA) | 1 ~ 100        | 0 ~ 150         | _              |     | 0.5 ~ 30         |

| 消費電流           | (μA) | 260 ~ 850      | 13 ~ 600        | -              |     | 4 ~ 20           |

| リーク削減能力(µA)    |      | 20             | 20              | 10未満*          |     | -                |

| 使用素子           |      | LVMOS及び<br>MOM | HVMOS及び<br>MOM  | LVMOS及び<br>MOM |     | LVMOS及び<br>MOM   |

| 外付け素子          |      | なし             | コンデンサ<br>(1 μF) | なし             |     | なし               |

LVMOS: 低耐圧 MOSトランジスタ HVMOS: 高耐圧MOSトランジスタ MOM: Metal-Oxide-Metal (配線間の静電容量を利用した, 実効的なコンデンサ) \*遮断ブロックの消費電流による

圧化し、アクセス時間に影響を与えるセル電流を高めて高速化 を図りつつ、消費電力の大半を占めるビット線振幅と周辺回路 には低電圧電源を適用した。これにより、動作電力を抑える ことを可能にした。

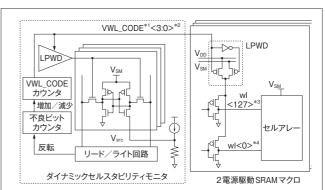

更に、この2電源の出力電圧を組み合わせて、PVT(注5)の 変動に応じたワード線電圧を生成する。 ダイナミックセルスタ ビリティモニタ回路(3)を提案した(図6)。セルの読出しと書込 みの特性を最適化することによりセルの動作マージンを広げ. SRAMの更なる低電圧化や小型化につながる回路技術として 研究開発を続けている。

LPWD: プログラマブルワード線電位発生回路

V<sub>src</sub>: セル安定性モニタ用ソース電位 V<sub>SM</sub>: SRAMセルアレー電源 -- ド純 V<sub>DD</sub>: デジタル部電源

- \*1:信号名

- \*2:4ビットのデジタルデータ \*3:128本目のワード線 \*4:1本目のワード線

- 図6. 低消費電力SRAM 高速動作と低消費電力の性能を実現する 2電源 SRAMと、低電圧・小型化につながるワード線電圧制御回路によっ て、SRAMの更なる低消費電力化を図る。

Block diagram of high-speed and low-power SRAM with dual power supply and word-line voltage control circuit

(注5) プロセス, 電源電圧,及び温度。

# 3 無線通信LSIへの適用

低電力FFのDM-FFとオンチップ電源制御回路を,90nm CMOS (相補型金属酸化膜半導体) プロセステクノロジーで製 造する無線LANベースバンドLSIに適用した(図7)。無線 LANベースバンドLSIの主な仕様を**表2**に示す。DM-FFの 高速性とαを考慮した最適化を行うことにより、デジタル部の 動作電力を23%削減した。また、CPU、ベースバンド、及びホ ストの三つの電源ドメインにおいてそれぞれオンチップレギュ レータ回路を用い、1.2 Vの外部電圧を1.0 Vの内部電圧に降 圧して低消費電力化を図った。この結果, ノーマル動作時の 消費電力を80 mW, スリープ時の消費電力を10 mW に抑え た。更に、自律復帰用のタイマだけが動作しているディープス リープモードでは、ゲーティッド I/O や厚膜プリミティブセルな ども適用して, 0.007 mWの消費電力を実現した(4)。 複数のオ ンチップレギュレータ回路を搭載すると、電源ドメイン間の電 圧がアンバランスになる可能性がある。当社は、電圧係数を 用いてアンバランスが発生するタイミングを予測する手法を独 自に開発し、設計検証に活用している(5)。

また、TransferJet<sup>TM</sup> LSI (TC35420) には、1.8 Vの外部電圧を1.2 Vの内部電圧に降圧するオンチップレギュレータと、待機時にデジタル部の電源を0.8 Vまで低下させるリテンショ

図7. 無線LANベースバンドLSIチップ — 低消費電力化回路技術を適用した,90 nm CMOSプロセステクノロジーで製造する無線LANベースバンドLSIのチップである。

Chip of wireless LAN baseband LSI fabricated with 90 nm complementary metal-oxide semiconductor (CMOS) technology

#### 表2. 無線LANベースバンドLSIの主な仕様

Main specifications of wireless LAN baseband LSI fabricated with 90 nm CMOS technology

| 項目     | 1     | 仕 様                                                            |  |  |  |

|--------|-------|----------------------------------------------------------------|--|--|--|

| プロセステク | ノロジー  | 90 nm CMOS 6層メタル                                               |  |  |  |

| 電源電圧   | (V)   | 3.3 (I/O部), 1.0 (CPU, ベースバンド, 及びホストの各電源<br>ドメイン), 1.2 (その他の回路) |  |  |  |

| ゲート規模  |       | ランダムロジック: 2.0 M ゲート, メモリ: 3.4 M ビット                            |  |  |  |

| 動作周波数  | (MHz) | 20, 40, 80, 及び160 (スタンバイ時周波数: 32 kHz)                          |  |  |  |

| CPU    |       | 32 ビット RISC×1                                                  |  |  |  |

| 消費電力   | (mW)  | ノーマル時:80, スリープ時:10, ディープスリープ時:0.007                            |  |  |  |

RISC: Reduced Instruction Set Computer

ン用のレギュレータとオンチップ電源スイッチを搭載し, 待機 時の消費電力削減と部品点数の削減を行った。

AC-FFや低消費電力SRAMに関しては、65 nmや40 nm CMOSプロセステクノロジーでテストチップを試作し、性能や低消費電力化の効果を確認した。

## 4 あとがき

動作時のスイッチング電力と待機時のリーク電力それぞれの低減に有効な低消費電力化技術として、低消費電力FFとオンチップ電源制御の回路技術を開発し、90 nm CMOSテクノロジーの無線LANベースバンドLSIや65 nm CMOSテクノロジーの TransferJet™ LSIなどに適用し、低消費電力化や部品点数の削減を行った。

更なる低消費電力化に向け、2電源駆動のSRAMやワード 線電圧を最適化するSRAMの研究開発も進めている。

# 文 献

- Teh, C. K. et al. Conditional Data Mapping Flip-Flops for Low-Power and High-Performance Systems. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 14, 12, 2006, p.1379 - 1383.

- (2) Teh, C. K. et al. "A 77 % Energy-Saving 22-Transistor Single-Phase-Clocking D-Flip-Flop with Adaptive-Coupling Configuration in 40nm CMOS". 2011 IEEE ISSCC Digest of Technical Papers. San Fransisco, CA, USA, 2011-02, IEEE. 2011, p.338 340.

- (3) Kushida, K. et al. "A Trimless, 0.5V-1.0V Wide Voltage Operation, High Density SRAM Macro Utilizing Dynamic Cell Stability Monitor and Multiple Memory Cell Access". Proc. Technical Papers of 2011 IEEE A-SSCC. Jeju, Korea, 2011-11, IEEE. 2011, p.161-164.

- (4) Taki, D. et al. "A 7uW deep-sleep, ultra low-power WLAN baseband LSI for mobile applications". Proc. 2011 IEEE Cool Chips XIV. Yokohama. 2011-04. IEEE, 2011. p.1 - 3.

- (5) Shiozawa, T. et al. "A New Timing Closure Methodology for an SoC with Multiple On-chip Regulators". Design Automation Conference. Anaheim, CA, USA, 2010-06, DAC. 2010, User Track 7U.4S.

テー チェン コン TEH Chen Kong, D.Eng.

セミコンダクター&ストレージ社 半導体研究開発センター 先端ワイヤレス・アナログ技術開発部主務, 博士 (工学)。低 消費電力回路及びデジタル電源回路の研究・開発に従事。 Center for Semiconductor Research & Development

#### 藤田 哲也 FUJITA Tetsuya

セミコンダクター&ストレージ社 半導体研究開発センター 先端ワイヤレス・アナログ技術開発部主務。低消費電力回路, オンチップ電源スイッチ回路, 及びレギュレータ回路の研究・開発に従事。 Center for Semiconductor Research & Development

## 櫛田 桂一 KUSHIDA Keiichi

セミコンダクター&ストレージ社 半導体研究開発センター 先端ワイヤレス・アナログ技術開発部主務。低消費電力回路 及びスタティックメモリ回路の研究・開発に従事。

Center for Semiconductor Research & Development