# 半導体マスク製造技術の革新

**Advanced Mask Manufacturing Technologies**

# 伊藤 正光

■ITOH Masamitsu

半導体デバイスはリソグラフィと呼ぶ転写技術により大量生産される。転写する回路パターンの原版がマスクであり、半導体 回路の微細化に伴いマスクパターンの微細化も進んでいる。マスクパターンに欠陥があると製造歩留りを大きく低下させること になるため、マスク製造技術が重要になる。

東芝は、グループ企業やパートナー企業と共同でマスク製造の技術革新を推し進め、大日本印刷(株)(以下、DNPと略記)と設立したマスク製造会社ディー・ティー・ファインエレクトロニクス(株)(以下、DTFと略記)で量産化と半導体微細化に取り組んでいる。近年、露光装置の短波長化が進み、極端紫外光(EUV: Extreme Ultraviolet)リソグラフィの開発が行われており、多層膜ミラーという従来マスクとは異なる構造を持つEUVマスクに対して、新たな各種製造装置の開発を進めている。

Lithography technologies are applied to high-volume manufacturing of semiconductor devices using a mask to print an image of a circuit pattern. With the increasing shrinkage of mask patterns accompanying the ongoing shrinkage of semiconductor devices, technologies for the manufacturing of masks without defects are becoming essential to achieve a high yield rate in advanced semiconductor manufacturing processes.

Toshiba is promoting the innovation of mask manufacturing technologies in cooperation with the Toshiba Group and its business partners, and has established D. T. Fine Electronics Co., Ltd. (DTF) with Dai Nippon Printing Co., Ltd. in order to supply masks that serve as a key driving force for the shrinkage of semiconductor devices. We are now developing advanced mask manufacturing technologies and equipment for extreme ultraviolet (EUV) lithography that have different structures from conventional deep ultraviolet (DUV) masks.

# 1 まえがき

半導体デバイスはリソグラフィと呼ぶ転写技術により大量生産 されるが、回路パターンを転写するための原版がマスクである。

マスクは152×152 mmで厚さが約6 mmの石英ガラス板上に紫外光(UV:Ultraviolet)透過率が低い金属材料で回路パターン(吸収体パターン)を形成したものである。半導体回路の微細化に伴ってマスクパターンの微細化も進み、現在では50 nm程度のサイズのパターンまで形成できるようになっている。更にそのパターンは、マスク全面でのばらつきが2 nm以下という精緻な均一性を持っている。また、マスクパターンは原版であるので、欠けや付着異物などの欠陥があると、半導体製造の歩留りを大きく低下させる。このため、全てのマスクは30 nm程度の大きさのパターン欠陥まで厳密に検査され、欠陥が見つかれば修正されて無欠陥の状態が常に維持されている。これは、例えば関東平野に存在するゴルフボールを1個も見逃さないというレベルの厳密さに相当する。

このようなマスクは、パターンを描画する電子ビーム描画装置や、描画されたレジストを現像してレジストパターンにする現像装置、レジストパターンからUV吸収体を加工して吸収体パターンにするエッチング装置、吸収体パターンの欠陥の有無を検査する欠陥検査装置、見つけた欠陥を修正する欠陥修正装

置, 異物を除去する洗浄装置, パターンの寸法を計測する測 長装置などの装置群により製造されている。

東芝はグループ企業やパートナー企業と共同で,これらの装置について新しい技術を世界に先駆けて開発して投入し,マスク製造技術の革新を推し進めている。

ここでは、現在開発を進めている波長13.5 nmの極端紫外光 (EUV: Extreme Ultraviolet) によるリソグラフィのEUV マスクを製造するための技術的課題と、それを解決するために開発した新技術について述べる。

# 2 EUVマスク製造技術

従来用いられているDUV (Deep Ultraviolet: 遠紫外光) 用のマスクは透過型であるが、EUVマスクは、DUV用とは異なって反射型である。これは、ほとんどの材料のEUVに対する透過率が非常に小さく、例えば石英基板の場合でも、DUVは十分に透過させるがEUVは透過させないためである。

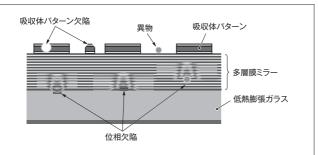

EUVマスクの構造を**図1**に示す。厚さ約3 nmのモリブデン (Mo) 層と厚さ約4 nmのシリコン (Si) 層が交互に約80層積み重なった多層膜ミラーを低熱膨張ガラス上に形成する。更にその上に、タンタル (Ta) を主成分とするEUVを吸収する材料により、回路パターンを形成している。この多層膜ミラー

特

図1. EUVマスクの断面構造 — EUVマスクには、多層膜ミラー位相欠 陥と呼ばれる新しい種類の欠陥が内部に生じて、その部分では反射率が 局所的に小さくなるという課題がある。

Cross-sectional structure of EUV mask

は、従来のマスクにはない構造で、EUVマスクで初めて採用 したものであるが、位相欠陥と呼ばれる新しい種類の欠陥が 内部に生じて、その部分では反射率が局所的に小さくなるとい う課題がある。

位相欠陥の原因としては、80回もの成膜を繰り返す多層膜ミラーの形成の途中で混入した異物や、基板となっている低熱膨張ガラス表面に生じている凹凸などが考えられる。この多層膜ミラーに生じた欠陥は後で修正するのが困難であるため、欠陥の数は少ないほど良い。しかし、現状ではなくすことは難しいので、EUVマスク用基板メーカーが位相欠陥の位置を特定し、EUVマスクメーカーと、チップメーカーなどのEUVマスクユーザーが連携してその欠陥を管理していくことが求められている。

当社はEUVマスク用基板メーカーなどとともに、(株)EUVL 基盤開発センター(以下、EIDECと略記)でマスクブランク欠 陥検査装置の開発を始めている。

### 2.1 電子ビーム描画

EUVマスクは従来のマスクと同様に、電子ビーム描画装置でパターンを形成する。

当社は、電子ビーム描画装置をグループ企業の(株)ニューフレアテクノジー(以下、NFTと略記)と共同で開発を進め、EUVマスクにも対応する描画装置EBM-8000を世界で初めて<sup>(注1)</sup>開発し、DTFへ導入した。NFTが製造する電子ビーム描画装置は世界の主なチップメーカーやマスクメーカーが採用し、業界標準機となっている。

電子ビーム描画装置は50 kVという高い加速電圧を使っているので、レジストが塗布されているマスク用基板上に電子ビームが照射されるとその一部が後方散乱電子として近傍に反射する。後方散乱した電子は入射した電子と同じようにレジストを感光させてしまうために、その量をあらかじめ予測して入射する電子の量を変化させていく必要がある。この操作を近接効果補正と呼ぶ。

(注1) 2010年3月時点, 当社調べ。

近接効果補正は後方散乱した電子の広がりとその量から補正量を決定するが、従来のマスクとEUVマスクでは後方散乱する電子の範囲と量が異なる。これは、Taを主成分とする吸収体の密度が従来のマスクの材料であるMoSiよりも高いことや、多層膜ミラーなどが存在することが原因である。EBM-8000はEUVマスクに対応した近接効果補正機能を備えている。

#### 2.2 レジスト現像

レジスト現像とは、電子ビーム描画装置で描画されたレジストを現像することで、これによってレジストパターンを形成する。 レジストパターンの形成には、次の三つの重要な課題がある。

- (1) ローディング効果 (回路パターンの疎密による寸法変動が生じる現象) の低減

- (2) マスク面内における回路パターン寸法の均一性向上

- (3) パターン欠陥の低減

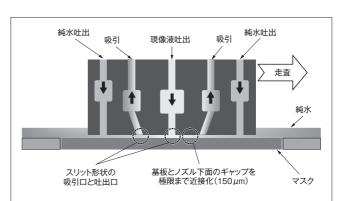

(1)と(3)を阻害する要因としては、現像反応により性能劣化した現像液が除去されずに滞留して、現像反応の進行を阻害することが挙げられる。この対策としては、性能が劣化した現像液をマスク基板上からいち早く除去して、新鮮な現像液を供給し続けることが非常に有効である。これを実現するため、現像液を吐出する現像ノズルに吸引機構も併せて設け、また、現像ノズルとマスク基板の距離を加工・組立精度の限界である150μmにまで近づけた構造の現像ノズルを開発した(図2)。これにより、現像液の吐出と吸引動作を連続的に行うことで現像液を高速で流し、性能が劣化した現像液をいち早く除去し新鮮な現像液に置換する機能を実現した。

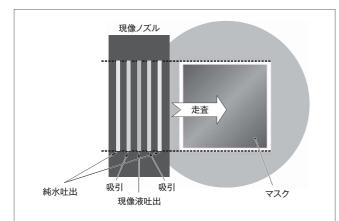

(2)を実現するためには、現像ノズルの現像液吐出スリット長をマスク基板の縦方向の一辺の長さと同等にして、吐出スリットの両側に吸引スリットを配置し、ノズルをスリットの長辺と垂直な方向に走査する構造とした(図3)。吐出スリットから前後の吸引スリットへ現像液の流れを形成し、現像液が存在する領域を両吸引スリットの間だけにした状態でマスクの端から

図2. 走査型現像装置のノズル断面図 — スリット状の現像液吐出口と 吸引口を持つ構造とすることで、現像反応により生じる性能劣化した現像 液をマスク基板上から即座に吸引して除去しながら、新鮮な現像液を供給 し続ける。更に、現像ノズルとマスク基板の距離を150 µmに近接させる ことで、よりいっそう現像液の置換効率が向上する。

Cross-sectional view of nozzle for scanning-type developer

図3. 走査型現像装置の上視図 — ノズルの現像液吐出スリットの長さをマスク基板の縦方向の一辺の長さと同等にし、ノズルをスリットの長辺と垂直な方向に等速で走査できる構造にすることで、現像液の供給量をマスク面内でそろえることを可能にして、面内寸法の均一性を格段に向上させた。

Top-down view of scanning-type developer

端までノズル走査を行うことで、マスク基板上の各位置に供給 される現像液量を厳密にそろえ、回路パターン寸法の均一性 を確保した。

当社は、これらの機能を併せ持つことでマスクのパターン加工における三つの重要な技術課題を一気に解決できる、PGSD (Proximity Gap Suction Development) 方式の走査型マスク量産用現像装置を東京エレクトロン(株)と共同で開発した。3台の量産機を2007年から2010年にかけてDTFへ導入し、既に多くの高精度マスク製造に寄与するとともにEUVマスク製造にも対応している。

この技術をマスク技術の国際学会Photomask Japanや SPIE (the International Society of Optics and Photonics) / BACUSなどで発表し、多くの優秀論文に選ばれている<sup>(1)-(3)</sup>。 また、第44回市村産業賞 貢献賞の受賞が決定した。

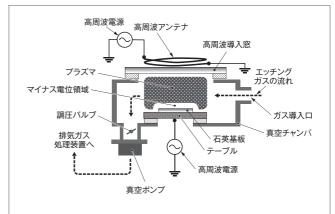

#### 2.3 吸収体エッチング

エッチング装置は、レジストパターンをエッチングマスクにしてTa吸収体を加工し、吸収体パターンを形成する。当社はグループ企業の芝浦メカトロニクス(株)と共同でマスク用のドライエッチング装置を開発した(図4)。2009年にDTFへ量産機を導入し、先端マスク製造に寄与している。

この装置は高効率なDAP (Divided Antenna Plasma)をプラズマソースに採用し、小容量で大排気量のプロセスチャンバにすることでエッチングガスの滞留時間を最小化し、更にチャンバをシンメトリ構造にすることでプラズマの均一性を向上させた。これらにより、高選択比とエッチングレートの均一性を両立させている。また重要な性能である低ダスト性能については、当社で長年培ってきたウェーハドライエッチングの知見を生かして内装パーツの材料及び設計を最適化した。これにより、他社の装置に対して一桁少ない低ダスト性能を達成した。

図4. ドライエッチング装置のチャンバ構造 — 高効率なDAPをプラズマソースに採用し、プラズマの均一性向上により、高選択比とエッチングレートの均一性を両立させている。

Chamber structure of dry etching system

## 2.4 パターン欠陥検査・修正

欠陥検査装置は、吸収体パターンが設計した形状に形成されているかを確認するため、パターン欠陥検査を行う。この検査にはNFTと共同で開発して従来のマスクに使っている、DUVを用いた欠陥検査装置を使うことが可能である。ただし、EUVマスクは従来のマスクより微細なパターンで、かつ反射像だけの検査になることから、偏光照明など、EUVマスク検査のための新たな機能を付加した。

当社は更に、より微細なパターン検査に対応するために電子 ビームを用いた欠陥検査装置の開発も進めている。

一般に、走査型電子顕微鏡(SEM)に代表される電子ビームを用いた撮像は非常に高い分解能を持つことが知られている。しかし従来のマスクでは基板が帯電するため、適用することが困難だった。一方EUVマスクは、基板のほぼ全面が多層膜ミラーに覆われているために導電性を持っており、電子ビームを用いた欠陥検査が可能になってきている。そこで、電子ビームを用いた欠陥検査として、SEMと同じ原理で数nmから数十nmの径に収束させた電子ビームをパターン面上に走査させてその反射電子や二次電子などを検出してパターン像を取得する方法が検討されている。しかしこの方法には、解像力を高くすれば検査速度が遅くなるというトレードオフの問題がある。

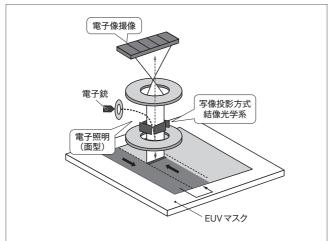

このようななかで当社は、(株) 荏原製作所と共同で写像投影方式の電子ビームを用いた欠陥検査装置の開発を世界に先駆けて進めた。この方式の最大の特長は、電子ビームを点状になるまで収束させず、100×100 μm程度の広がりを持った面としてパターン面上に照射し、照射したパターン面から放出される反射電子や二次電子などを結像電子光学系により撮像素子に結像させてパターン像を取得することである(図5)。

これにより、一度に広い領域のパターン像を取得でき、SEM タイプと比較すると格段に検査速度を向上できる。また、DUV で問題になる波長による解像力限界は、電子ビームでは十分に

特

図5. 写像投影方式電子ビームを用いた欠陥検査装置 — 電子ビームを 収束させた "点" ではなく広がりを持った "面" でパターン面上に照射し、 高感度検査と高速検査を両立させている。

Defect inspection tool with projection electron optics

精細であるために問題にならない。加えて、低エネルギーの電子ビームを照射することでマスク表面上の帯電コントラストを高感度に検出して結像できるため、従来の光学式検査では検出が難しい極薄の異物検査を可能にし、20 nmという極小の異物の検出に成功している。この装置は既にDTFへ導入しEUVマスクのパターン欠陥検査と異物検査に用いている。

当社は更に、DNPとともにEIDECで次世代の写像投影方式 電子ビームを用いたEUV欠陥検査装置の開発を始めている。

パターン欠陥検査で見つかった欠陥は、マスクでも用いられている電子ビームを用いた欠陥修正装置で修正できる<sup>(4)</sup>。

欠陥修正後のパターンを保証するため、EUVマスクパターンの3D(3次元)像を特殊なSEMで取得して、その3D像をリソグラフィシミュレーションすることで、ウェーハに転写されたとき

マスクパターンの3D像を得る アスクパターンの3D像を得る が状計測 ウェーハ上のパターンを予測する ウェーハイメージで判断

図6. 欠陥修正箇所の保証技術 — EUVマスクパターンの欠陥修正箇所の3D 像を特殊なSEMにより取得して、その3D 像をリソグラフィシミュレーションすることでウェーハに転写されたときの空間像を予測する。

Technologies for verification of repaired patterns

の空間像を予測する手法の開発を進めている(5)(図6)。

3D像を取得できる特殊なSEMはグループ企業の(株)トプコンと共同で開発した。T-MOL (Tilting and Moving Object Lens)と呼ぶ電子光学系により、真上からのSEM像、及び上下左右にそれぞれ5°傾けた位置からのSEM像を取得し、それらの画像から3D像を合成する技術である。この技術の特長は8,000×8,000画素という超高精細の3D画像を低ひずみで取得できることであり、これにより必要なリソグラフィシミュレーション精度を得ることが可能になっている。この装置もDTFへ2011年に導入し、EUVマスクの欠陥修正箇所のウェーハ上での転写特性を、実際に転写することなく確認できるようにしている。

## 3 あとがき

当社は、リソグラフィとマスクの両方を開発していることを最大限に生かし、リソグラフィ動向を的確に予測して将来のマスクに求められる機能を早期に把握してきた。そしてその結果に基づき、EUVマスク製造に必要な技術と装置をグループ企業やパートナー企業とともに世界に先んじて開発し導入してきた。DTFで稼働しているマスク・EUVマスク製造装置の多くは当社が開発した技術を採用しており、当社の半導体ビジネスを支えている。

今後もこの強力な開発体制を基に、次世代の技術革新を実現していく。

## 文 献

- Sakurai, H. et al. Performance of Proximity Gap Suction Development (PGSD). Proc. SPIE. 4889, 2002, p.737 - 745.

- Itoh, M. et al. Novel Resist Development System for Photomasks. Proc. SPIE. 4889, 2002, p.746 - 753.

- (3) Ooishi, K. et al. New development method eliminating the loading and micro-loading effect. Proc. SPIE. 5130, 2003, p.67 - 77.

- (4) Itoh, M. et al. "EUV Mask Readiness in 2012". SEMATIC homepage. <a href="http://www.sematech.org/">http://www.sematech.org/</a>, (accessed 2012-02-20).

- (5) Yamanaka, E. et al. "3D measurement SEM for EUV mask pattern quality assurance based on lithography simulation". SEMATIC homepage. <a href="http://www.sematech.org/meetings/archives/litho/8939/pres/MA-P18.pdf">http://www.sematech.org/meetings/archives/litho/8939/pres/MA-P18.pdf</a>, (accessed 2012-02-20).

伊藤 正光 ITOH Masamitsu 研究開発センター デバイスプロセス開発センターグループ長。 リソグラフィフォトマスクの技術開発に従事。 Device Process Development Center