# 垂直磁化方式のMTJ記憶素子を用いた スピン注入書込みMRAM

Spin-Transfer Torque Writing MRAM with Perpendicular Magnetic Tunnel Junction Devices

# 與田 博明

■ YODA Hiroaki

磁気抵抗メモリ (MRAM: Magnetoresistive RAM) は高速のデータ読込み・書込みと無限大の書換え回数を実現できる 唯一の不揮発性メモリであり、夢のメモリと言われている。しかし磁界書込み原理を用いたMRAMは、書込み効率が悪く、大容量化が困難であったため、近年、スピン注入書込み原理を用いたMRAMの研究が活発に行われている。

東芝は、従来の面内磁化方式に代えて、垂直磁化方式のMTJ (P-MTJ: Perpendicular Magnetic Tunnel Junction) 記憶素子を開発した。2007年に世界で初めて<sup>(注1)</sup>P-MTJ 記憶素子のスピン注入書込みを実証して以来、数十 $\mu$ Aの低電流での書込みと200% を超える抵抗変化率 (MR) を実現するなど、Gビット級の大容量化技術を構築してきており、実用化に向けた研究開発を進めている。

Field writing magnetoresistive random access memories (MRAMs) have been actively developed as nonvolatile working memories because of their attributes including unlimited endurance and fast read/write speed, exceeding those of other nonvolatile memories. However, field writing MRAMs lack scalability due to their inefficient writing. In response to this situation, intensive efforts have been focused on spin-transfer torque writing MRAMs in recent years.

Toshiba has developed a magnetic tunnel junction device with perpendicular anisotropy (abbreviated as P-MTJ device) for storage devices to extend scalability. Since we demonstrated the world's first spin-transfer writing on P-MTJ devices in 2007, we have achieved small-current writing of several tens of microamperes and a large magnetoresistance (MR) of more than 200%. We are now engaged in research and development of practical applications for the realization of a large-capacity gigabit-class memory.

## 1 まえがき

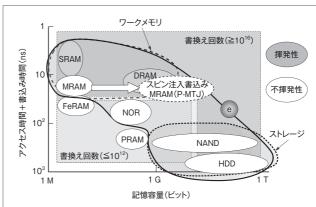

既存のメモリや新たに開発されたメモリなどのアクセス時間 + 書込み時間と記憶容量の関係を整理して**図1**に示す。高速 化と大容量化が進むメモリ分野において、高速で書換え回数 に制限のないものはワークメモリとして、大容量のものはストレージとして広く使用されている。ストレージはHDD(ハードディスクドライブ)に代表されるように不揮発性であるが、ワークメモリはDRAMの誕生以来揮発性となっていた。

一般的に、揮発性メモリであるDRAMを搭載した機器は、ストレージから読み出された情報をDRAMに書き込んで初めて使用可能になる。パソコン (PC) ではこの時間が1分以上かかるため電源を入れた状態にする場合が多くなり電力を浪費している。また、使用中にも数十msごとにデータを書き直す (リフレッシュ) 必要があり、多くの電力を消費している。そこで、必要なときに瞬時に電源を入れて使用できる省エネ性の高い機器を実現するため、不揮発性のワークメモリが求められている。

ワークメモリを不揮発性にするため強誘電体メモリ (FeRAM: Ferroelectric RAM) などが開発されてきたが、情報の書換え

(注1) 2007年9月にIWFIPT (International Workshop on Future Information Processing Technologies)で発表, 当社調べ。

SRAM: Static RAM NOR : NORフラッシュメモリ e:電子PRAM: Phase Change RAM NAND: NANDフラッシュメモリ

図1. メモリ及びストレージのアクセス時間+書込み時間と記憶容量のマッピング — 不揮発で高速な、かつ書換え回数が無制限で、Gビット級の大容量ワークメモリの出現が望まれる。

Map of memory and storage allocations for access time + write time vs. bit density

に際して記憶素子内の原子が移動するため書換え回数に制限 がある。そのため、真のワークメモリとは成りえていない。

磁気抵抗メモリ (MRAM: Magnetoresistive RAM) では, 情報の書換えに際してMTJ (Magnetic Tunnel Junction) 記

特

憶素子の記憶層の磁化を反転させる。このとき、原子の移動はなく、電子のスピンが反転するため書換え回数に制限がない。2006年に製品化された磁界書込み原理を用いたMRAMでも無限回の書込みが保障されたが、磁界書込みの書込み効率の悪さが問題となり、その高集積化が停滞した。それに代わり、スピン注入書込み原理を用いたMRAMの開発が活発になったが、書込み電流値が大きく、大容量化ができなかった。

この壁を突破するため東芝は、従来からの面内磁化方式に代えて、垂直磁化方式のMTJ (P-MTJ: Perpendicular-MTJ) 記憶素子を開発し、2007年にP-MTJ 記憶素子へのスピン注入書込みを世界で初めて実証した<sup>(1)</sup>。当社はその後もこの分野で開発を先導しており、2011年には書込み電流値を一桁以上低減するとともに200%を超える抵抗変化率 (MR)を確保することに成功し、Gビット級の高集積化に道を開いた<sup>(2)-02</sup>。ここでは、P-MTJ 記憶素子の実用性と垂直磁化方式による優位性を述べるとともに、P-MTJ 記憶素子の更なる実用化技術について述べる。

# 2 P-MTJ記憶素子の実用性

#### 2.1 データ書込みの確実性

磁界書込み原理は、HDDと磁界書込みMRAMの製品化など、データ書込みの確実性に関しては実績がある。しかし面内磁化方式のスピン注入書込み原理では、back hoppingと呼ばれる誤書込み現象が頻発することが課題であった。

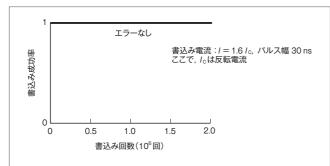

そこで当社は、これが面内磁化方式に固有の現象であることを示し、P-MTJ記憶素子では図2に示すように誤書込みが発生しないことを実証した<sup>(2)</sup>。

### 2.2 書換え回数

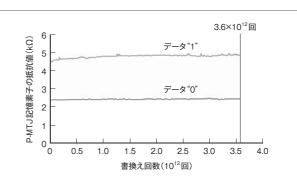

P-MTJ 記憶素子では、磁化反転に際して電子の移動だけが起こり原子の移動は発生しないため、原理的には無限回数の書換えが可能である。そこで $3.6 \times 10^{12}$ 回までの書換えを行ってP-MTJ 記憶素子の抵抗値の変化がないかどうかを調べた

図2. P-MTJ記憶素子の書込みの確実性検証 — 反転電流の1.6倍の書込み電流によって2×10<sup>6</sup>回の書込みテストを行ったが、誤書込みを一度も観測しなかった。

Verification of accurate data writing to P-MTJ devices

図3. P-MTJ記憶素子の書換えテスト —  $3.6 \times 10^{12}$  回の書換えテストを行ったが素子抵抗値の顕著な劣化は観測されなかった。

Results of write cycling tests of P-MTJ devices

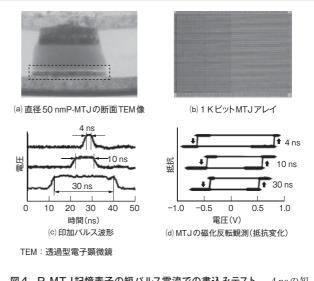

図4. P-MTJ記憶素子の短パルス電流での書込みテスト — 4 ns の短パルス電流で書込みができることが確認された。

Results of short pulse writing tests of P-MTJ devices

結果、図3に示すように抵抗値の劣化は観測されなかった。

#### 2.3 書込みの高速性

P-MTJ記憶素子に高速の書込みが可能かどうかを調べるために、 $1 \, \mathrm{K} \, \mathrm{E}$  ビットチップを試作して短パルスでの書込みテストを行った。その結果、**図4**に示すように最短のパルス幅が4 nsの短パルスを用いた書込みでも磁化反転を観測した<sup>(3), (4)</sup>。 更に、垂直磁化方式のGMR (Giant Magnetoresistance) 記憶素子を用いた書込みテストも行い、パルス幅が500 p(ピコ: $10^{-12}$ )sの短パルスでも書込みができることを確認している<sup>(5)</sup>。

#### 3 垂直磁化方式による優位性

垂直磁化方式には、前述したデータ書込みの確実性という 本質的なメリットに加えて、以下に述べるメリットがある。

#### 3.1 微細サイズでの不揮発性の実現

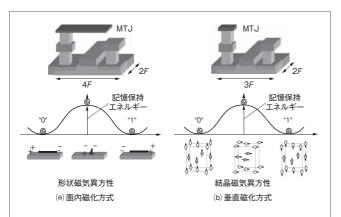

MRAMでは記憶層の磁化の向きに対してデータの"0"と

"1" を対応させる。10年間の不揮発性を持たせるためには、 "0" の状態と "1" の状態間に $60 k_B T$ 程度のエネルギーバリア (記憶保持エネルギー) が必要になる。ここで、 $k_B$ はボルツマン定数、Tは絶対温度である。

面内磁化方式の場合は、図5(a)に示すようにMTJ記憶素子の平面形状に $1:2\sim1:3$ 程度のアスペクト比を持たせることでエネルギーバリアを作る。これを形状磁気異方性エネルギーと言い、結果として長辺方向で磁化が安定になる。

垂直磁化方式の場合は、図5(b)に示すように結晶格子に磁気異方性を持たせてエネルギーバリアを作る。これを結晶磁気異方性エネルギーと言い、結果として垂直方向で磁化が安定になる。バルク材料では結晶磁気異方性エネルギーは $10^7$  erg/ccが可能であり、薄膜でもバルク材料と同等の結晶磁気異方性エネルギーが実現できれば、10 nm程度に微細化しても60 k<sub>B</sub>T程度の記憶保持エネルギーを確保できる。これが垂直磁化方式の第二の本質的なメリットである。

#### 3.2 DRAMと同等の微細セルサイズの実現

面内磁化方式のMTJ記憶素子では、前述のようにMTJ記憶素子の平面形状にアスペクト比を持たせる必要があるため $8F^2$  (F: 配線のハーフピッチ)を超えるセルサイズとなり、DRAMと同等の高集積化を実現することは極めて困難である。一方P-MTJ記憶素子では、その平面形状を円とすることができるため、DRAMと同等の $6F^2$ のセルサイズにすることができる。これが垂直磁化方式の第三の本質的なメリットである。

## 3.3 書込みの高効率性

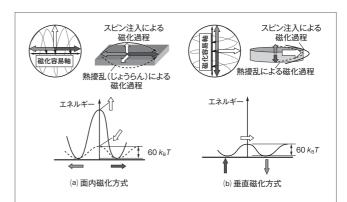

面内磁化方式と垂直磁化方式のスピン注入書込みによる 磁化反転について、図6を用いて説明する。

面内磁化方式の場合は、(a)に示すようにスピン注入により 磁化の歳差運動を増大させるため、その反転途中で磁化に垂 直成分を持たせなければならない。このときの反磁界エネル ギーは記憶保持エネルギーに比べ一桁以上大きいため、面内

図5. 面内磁化方式と垂直磁化方式の不揮発性の起源 — 面内磁化方式は素子の平面形状の異方性が、垂直磁化方式は結晶の異方性が不揮発性の起源である。

Origins of nonvolatility of MTJ and P-MTJ devices

図6. 面内磁化方式と垂直磁化方式のスピン注入書込みによる磁化反転のようす — 面内磁化方式の場合、磁化反転の途中で膜面垂直方向の反磁界エネルギーを超える必要があるため、エネルギー効率が非常に悪い。 Magnetization switching of MTJ and P-MTJ devices

磁化方式のスピン注入書込みはエネルギー効率が非常に悪い。 一方、垂直磁化方式の場合は、(b)に示すようにスピン注入 により磁化を反転させるために超えなければならないエネル ギーバリアは記憶保持エネルギーと同じ60 k<sub>B</sub>T 程度であるこ とからエネルギー効率が非常に良い。

面内磁化方式の反転しきい値電流  $(I_{cl})$  及び垂直磁化方式の 反転しきい値電流  $(I_{cp})$  は、それぞれ式(1)及び(2)で示される。

$$I_{\rm cl} = \frac{2e}{\hbar} \frac{\alpha}{g(\theta)} (2 \times 60 \ k_{\rm B}T + 2\pi M_{\rm S}^2 t F^2)$$

(1)

$$I_{\rm cp} = \frac{2e}{\hbar} \frac{\alpha}{g(\theta)} \quad (2 \times 60 \, k_{\rm B}T) \tag{2}$$

e :電子の電荷h : ディラック定数α : ダンピング定数g(θ):スピン注入効率

θ :参照層と記憶層の磁化の成す角度

Ms: 飽和磁化t: 記憶層の膜厚F: 記憶層の幅

反磁界エネルギーに相当する式(1)の第2項が式(2)には存在 しないことから、垂直磁化方式では本質的に大きな反転しき い値電流が必要にならない。これが垂直磁化方式の第四の 本質的なメリットである。

## 4 P-MTJ記憶素子のブレークスルー技術

これまで述べてきたように、垂直磁化方式は原理的に書込み電流値を大幅に低減できる。しかし、2006年に報告された電流値は1 mAを超える大きなものであった。その主な原因は、ダンピング定数が大きかったこと、及び MR が小さかったことである。これらを解決する、当社が開発したブレークスルー

特

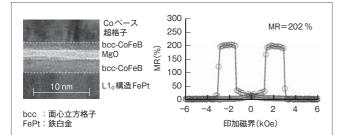

**図7. P-MTJ積層膜の構造変更によるMR向上** — 目標である150 % を超える202 %のMRを実現した。

Large MR ratio in P-MTJ stacks

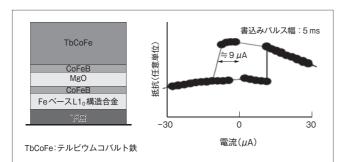

図8. P-MTJ記憶素子での反転電流低減 — Feベースの記憶層を用いることにより、数十 $\mu$  Aの目標を超える7~9 $\mu$ Aでのスピン注入磁化反転を実現した。

Reduction in write current switching of P-MTJ devices

技術について以下に述べる。

## 4.1 垂直磁化方式での高MR化

2006年まではP-MTJ記憶素子でのスピン注入磁化反転の報告はなく、GMR記憶素子での報告例だけであり、MRは $1\sim2\%$ と非常に小さかった。

当社は、垂直材料と酸化マグネシウム (MgO)トンネル障壁との間に鉄 (Fe) やコバルト鉄ボロン (CoFeB)を挿入することで、MRを向上させることができることを示し、最近では目標である 150% を超える 202% の MRを実現している (6)-(8) (図7)。

## 4.2 垂直磁化方式での書込み電流値の低減

当社は2007年にP-MTJ 記憶素子へのスピン注入磁化反転 例を報告 (1)して以来, 記憶層のダンピング定数を小さくすることにより反転電流値の低減を行い, 図8に示すように $7\sim9\,\mu$ A の書込み電流でのスピン注入磁化反転を実証した (9)-(11)。

## 5 あとがき

垂直磁化方式のスピン注入書込みを2007年に当社が実証して以来、スピン注入書込み原理MRAMの開発は目覚ましい発展を遂げており、これまでGビット級の大容量MRAMの実現の指標である数十μAを下回る低電流での磁化反転と、200%を超えるMRが達成された。最近では65 nm世代のCMOS (相補型金属酸化膜半導体)技術を用いた64 Mビット

のアレイを開発した[12]。

現在、高速で書換え回数に制限のない不揮発性ワークメモリの候補としてはMRAMしか存在していない。今後、生産技術などの開発を加速し、高速でGビット級大容量の不揮発性メモリの実現を目指していく。

この研究の一部は、独立行政法人 新エネルギー・産業技術総合開発機構 (NEDO) の委託事業「スピントロニクス不揮発性機能技術プロジェクト」で実施したものである。

# 文 献

- (1) Yoda, H. et al. "Potential of MRAM for High speed & High Density Application". 7th International Workshop on Future Information Processing Technologies(IWFIPT), Session II c. Dresden, 2007-09, IWFIPT, 2007.

- (2) Aikawa, H. et al. "A STUDY OF ROBUSTNESS TO SWITCHING ERROR IN A PERPENDICULAR TMR ELEMENT". Nanomagnetism, Spin Electronics and Quantum Optics(NSEQO) 2009 digest. Rio de Janeiro, 2009-11, CBPF(Centro Brasileiro de Pesquisas Físicas), 2009, p.39.

- (3) Yoda, H. et al. "Study of a spin torque transfer MRAM with perpendicular magnetization TMR elements as a high density non-volatile memory". Meeting Abstracts MA 2008-02, Pacific Rim Meeting on Electrochemical and Solid-State. Science (PRIME) 2008, Honolulu, HI, 2008-10, Electrochemical Society, 2008, abs.2108.

- (4) Kishi, T. et al. "Lower-current and fast switching of a perpendicular TMR for high speed and high density spin-transfer-torque MRAM". Electron Devices Meeting(IEDM) 2008 digest. San Francisco, CA, 2008-12. IEEE. 2008, p.1-4.

- (5) Tomita, H. et al. High-speed spin-transfer switching in GMR nanopillars with perpendicular anisotropy. IEEE Trans. Magnetics. 47, 6, 2011, p.1599 - 1602.

- (6) Yoshikawa, M. et al. Tunnel Magnetoresistance Over 100% in MgO-Based Magnetic Tunnel Junction Films With Perpendicular Magnetic L10-FePt Electrodes. IEEE Trans. Magn. 44, 11, 2008, p.2573.

- (7) 永瀬俊彦 他. "TMR比200%超垂直磁化方式トンネル接合". 第33回日本磁気学会学術講演会概要集. 長崎, 2009-09, 日本磁気学会. 2009, p.249.

- Nishiyama, K. et al. "Large tunnel magnetoresistance of over 200% in MgO-based magnetic tunnel junction with perpendicular magnetic anisotropy". Digests of 11th Joint MMM-Intermag Conference. Washington, DC, 2010-01, IEEE. 2010, p.1089.

- (9) Nagase, T. et al. "Spin transfer torque switching in perpendicular magnetic tunnel junctions with Co based multilayer". 2008 American Physical Society(APS) March meeting. New Orleans, Louisiana, 2008-03, APS. 2008, C1.00331.

- (0) 吉川将寿 他. "垂直磁化L10-FePd記憶層のスピン注入磁化反転" 第33回日本磁気学会学術講演会概要集. 長崎, 2009-09, 日本磁気学会. 2009, p.250.

- (11) Daibou, T. et al. "Spin transfer torque switching in Magnetic Tunnel Junctions using L10-ordered Fe based alloys for Ferromagnetic Electrodes". Digests of 11th Joint MMM-Intermag Conference. Washington, DC, 2010-01, IEEE, 2010, p.810.

- (12) Tsuchida, K. et al. "A 64Mb MRAM with Clamped-Reference and Adequate-Reference Schemes". Solid-State Circuits Conference Digest of Technical Papers(ISSCC). San Francisco, CA, 2010-02, IEEE. p.258 - 259.

與田 博明 YODA Hiroaki 研究開発センター デバイスプロセス開発センター技監。 MRAMの研究開発に従事。IEEE会員。 Device Process Development Center