55

## SIN MOSFETを用いた 乱数生成素子の長寿命化技術

### 使用法の工夫で高い安全性と長期 信頼性を備えた乱数生成回路を実現

乱数は、セキュリティ技術の信頼性を決める暗号化技 術の要です。これまでモバイル機器やICカードでは擬似 乱数を用いてきましたが、近年、より高度なセキュリティ 環境を構築するために、再現が不可能な物理現象を利用 して生成する真性乱数の必要性が高まっています。

これまで東芝は、SiN膜(シリコン窒化膜)を蓄積層と するMOSFET (金属酸化膜半導体型電界効果トランジスタ) をノイズ源素子とした物理乱数生成回路を開発し、高い安全 性を持つ乱数生成回路を実現してきました。 更に、 今回 ノイズ特性の経年変化を抑制するメカニズムを解明して. 10年間の長期使用に耐えうる素子動作技術を開発しました。

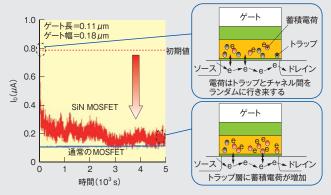

#### SIN MOSFET **麦**子構造 ゲート 1.0 制御酸化膜 蓄積電荷 0.9 /トラップ トラップ層 (SiリッチSiN) 0.8 トンネル サSIN) ソース e e e e ドレイン \_\_ 酸化膜 0.7 通堂のMOSFFT 1.0 1.1 1.2 1.3 1.4 1.5 1.6 Siチャネル 時間(s) ノイズ源素子 乱数変換回路 10010110 •

図1. 乱数生成の仕組み — ノイズ源素子のSiN MOSFET で生成されたノイ ズ信号を乱数変換回路でデジタル化します。

図2. I<sub>D</sub>と素子中トラップの経年変化 — トラップ層に電荷が蓄積することで、 しきい値がシフトし、Inが時間とともに減少します。

# ため、長期信頼性の確保が課題となっ

銀行取引などが携帯電話を用いて気 軽にできるようになった一方。セキュリ ティに関する問題も近年多く発生して います。このため、どんなときでも高い セキュリティレベルを維持できること が、ネットセキュリティでの最重要事項 です。従来、モバイル機器では擬似乱 数が多く利用されていますが、近年、乱 数の基準は厳しくなる傾向にあり、より 安全性の高い物理乱数が必要になって きました。

安全性の高い乱数

しかし物理乱数生成回路には、回路 規模の拡大や性能のばらつきなどの課 題があります。性能のばらつきはセキュ リティの穴となり、ハッカーなどの標的 となります。東芝がノイズ源として開発し たSiN MOSFET(1)は、従来のトランジス タと異なり、多量のトラップを内蔵し、か つ、高い頻度で捕獲と放出を繰り返す ていました。

#### 乱数生成の仕組み

SiN MOSFETの基本構造はフロー ティングゲート型FETと同様で、ゲート 絶縁膜上に通常のSiN膜(Si<sub>3</sub>N<sub>4</sub>)より も過剰にSiを含む非化学量論的SiN膜 を用いることにより、膜中のダングリン グボンドがトラップとして働きます。直 接トンネル効果によって、Siチャネルと ダングリングボンド間でキャリア(e:電 子) の捕獲と放出が高速かつランダムに 起こり、ドレイン電流(ln)にノイズが生 じます (**図1**)。このI<sub>D</sub>のランダムノイズ を乱数変換回路でデジタル変換して. 乱数を生成します。擬似乱数では生成 できない予測不可能性を持つ乱数が得 られ、安全性の高い乱数を高速生成す

ることが可能なことから、モバイル機 器に最適な小型回路を実現できます。

#### IDの経年変化と乱数の質

SiN MOSFETは、トラップとなる欠 陥がSiN膜中に多量に含まれ、かつ欠 陥が高い頻度で発生するため、一定電 圧を印加し続けた場合、トはランダムな 揺らぎを持ちながら、素子のしきい値 が経年変化します(図2)。乱数変換回 路で "1" 又は "O" に振り分ける基準値 からInが大きく外れると、1と0の発生 頻度のバランスが崩れ、生成される乱 数の質を劣化させるおそれがあります。 そこで当社は、経年変化を抑制するた め、素子を断続的に使用する技術を開 発しました。素子はどのタイミングでも オンとオフができ、用途に応じて自由に 変更できるという特長があります。

1.2

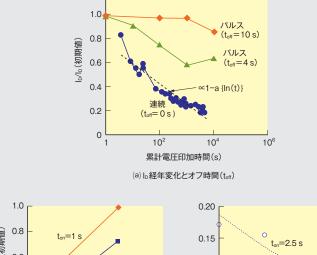

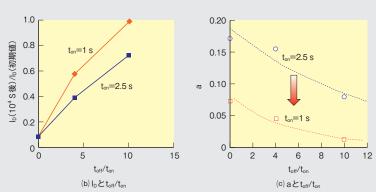

図3. 経年変化によるIpの減少 — Ipは時間経過とともに指数関数的に減少します。累計動 作時間が同じでもtonが小さいほどIpの経年変化は小さくなり、aも小さくなります。

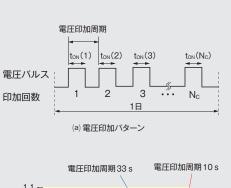

No: 1日当たりの使用回数

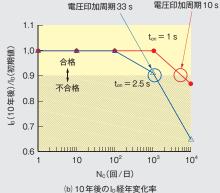

図4. In 経年変化率の電圧印加周期依存性 -- 1パル スのtonが1sのとき, 周期10sで10年間使用してもID の経年変化は10%以下にできます。

### 乱数の使用頻度と素子寿命の関係

電圧印加時には、時折深い準位に電 子が捕獲されて放出されにくくなるとと もに、電圧印加時間が長いほど浅い準 位にトラップされていた電子も深い準位 に移行しやすくなり、蓄積電荷が増加し ます。しかし、印加電圧を適宜オフにす ることで、トラップに捕獲された電子は Siチャネルへ放出され、ノイズ源素子の しきい値は初期に近い状態へ戻ります。

電圧印加周期をパラメータとして、こ のメカニズムによって、経年変化による lpの減少レートがどのように変化するか を図3に示します。 ln(初期値)をlnの 初期値, aを経年変化レートとすると, lpは時間(t)が経過するにつれて式(1) で示すように指数関数的に減少します。

$(|I_D|/|I_D(初期値)|=1-a\{ln(t)\}$  (1)

図3(b), (c)から, 1回当たりのオン時 間(ton)が短いほうが、累計電圧印加 時間は同じであってもしの経年変化は 小さくなることがわかります。これは. SiN MOSFETが多量のトラップを含ん でおり、長時間の電圧印加により、 しが 対数的に減少するという特性のためで す。更に解析により、各パルス周期で の10の経年変化を予測した結果、1パル スのtonが1 sのとき、周期10 sで10年 間使用しても10の経年変化は10%以 下にできることを確認しました(図4)。

これは、連続的に使用したときにし の経年変化が90%以上になることと 比較すると、「」の変化を大幅に抑制で きたことになります。また、ID平均値の 変化が10%以下であれば、出力乱数に 影響を及ぼすこともなく、この物理乱数 生成回路を用いることにより、10年間の 長期信頼性を確保することができます。

#### 今後の展望

その他には、1パルスのtonが1sより 長い場合でも、オフ時間 (toff) を長くす ることで「Dの経年変化を軽減できます。 更に、電圧を調整することでいっそう の軽減が見込まれます。これらの結果 は、高い安全性と長期信頼性を兼ね備 えた物理乱数生成回路の実現に大きく 寄与すると期待されます。

#### 文 献

(1) 松本麻里 他. SiリッチSiN MOSFETを用 いた高速乱数生成器. 東芝レビュー. 62, 7, 2007. p.39 - 42

#### 松本 麻里

研究開発センター LSI基盤技術ラボラトリー

54 東芝レビュー Vol.66 No.5 (2011) SiN MOSFETを用いた乱数生成素子の長寿命化技術