一般論文 FEATURE ARTICLES

# LSIやメモリの高集積化を目指すナノカーボン配線技術

Nanocarbon Interconnect Technologies for Future LSIs and Memories

酒井 忠司 山崎 雄一 片桐 雅之

■SAKAI Tadashi ■YAMAZAKI Yuichi

LSIやメモリの高集積化に向け、トランジスタだけでなく配線にも、いっそうの微細化や3次元化への対応が求められている。一方、現在の金属配線は、細線化に伴い電流密度耐性の低下や表面散乱などによる抵抗の上昇が顕在化しつつある。これらの課題に対して、カーボンナノチューブ (CNT: Carbon Nanotube) やグラフェンなどのナノカーボン材料の適用が期待されている。東芝は、NEDO (独立行政法人 新エネルギー・産業技術総合開発機構)の「次世代半導体材料・プロセス基盤 (MIRAI) プロジェクト」を通じてCNTを微細配線へ適用する技術の開発に取り組み、半導体プロセスと整合性のある低温で多層CNTの高速成長と世界最高(注1)の高密度成長2×10<sup>12</sup>本/cm²を実現するとともに、縦方向配線の基盤となる微細ビアアレイ (ビア: 多層配線の層間接続配線)へのCNT選択形成プロセスを開発した。

■ KATAGIRI Masayuki

With the higher integration of large-scale integrations (LSIs) and memories in recent years, finer and three-dimensional (3D) interconnects are becoming essential. However, the decrease in current carrying capacity and increase in resistance of existing metal interconnects are serious issues accompanying the thinning of interconnects. As a solution to these issues, so-called nanocarbon materials, such as carbon nanotubes (CNTs) and graphene, are expected to overcome the technical limitations of conventional interconnects.

Through a project of the New Energy and Industrial Technology Development Organization (NEDO), Toshiba has developed nanocarbon interconnect technologies for future LSIs and memories that provide the following results: (1) low-temperature growth of CNTs as well as (2) high-density growth compatible with semiconductor processes, and (3) selective growth into fine via-hole arrays.

These results are applicable to the realization of a high-aspect-ratio vertical contact plug, which is required for future 3D memory interconnects.

# 1 まえがき

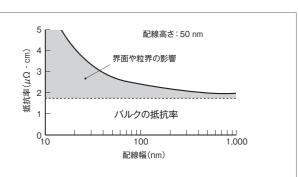

半導体デバイスには、論理回路やメモリセルを構成する CMOS (相補型金属酸化膜半導体)トランジスタどうしを接続するために銅 (Cu) などの多層金属配線が用いられている。半導体の高集積化には、トランジスタだけでなくこれら配線の微細化や3次元化が求められている。一方、配線の微細化や薄膜化は配線抵抗の顕著な増大をもたらすことが懸念されている。図1に示すように<sup>(1)</sup>、配線幅が100 nmを下回ると、結晶粒界や界面での電子の非弾性散乱が顕著となり、抵抗率は急激に増大すると予測されている。また最近では、半導体業界のロードマップ (ITRS: International Technology Roadmap for Semiconductors)<sup>(2)</sup>において、微細化に伴う配線の電流密度耐性に関する予測が大幅に見直され、電流密度耐性の増大に対して有効な解を見いだせない状況となっている。

以上のような微細化に伴う配線の課題に対して、量子閉じ込め効果などにより微細寸法領域で散乱の少ない伝導特性が期待できる、カーボンナノチューブ(CNT: Carbon Nanotube) やグラフェンなどのナノカーボン材料が新しい配線材料として期

図1. Cu配線抵抗率の配線幅依存性 — 配線幅の微細化に伴い, Cu配線の抵抗率は急激に上昇することが予想されている。

Dependence of copper (Cu) interconnect resistivity on interconnect width

待されている<sup>(3)</sup>。ここでは、ナノカーボン材料の配線応用の可能性と開発課題について概観し、東芝が「次世代半導体材料・プロセス基盤 (MIRAI) プロジェクト」への参画を通じて開発した、世界最高クラスの多層 CNT 高密度成長技術と微細CNT ビア集積プロセス技術について述べる。

## 2 ナノカーボン材料の配線応用の可能性と課題

グラフェンとはグラファイトを構成する炭素(C)の六員環構

(注1) 2010年9月現在, 多層CNTの成長密度として, 当社調べ。

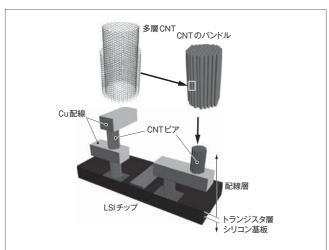

図2. CNT及びCNTビアの構造 — 多層CNTはグラフェンシートから成る筒が重なった構造であり、多層CNTの束 (バンドル)をビアに用いる。 Structure of multiwall CNT and CNT via

造から成る単層シートを指し<sup>(4)</sup>、CNTは**図2**に示すように、グラフェンがnmオーダの直径で筒状に巻かれた構造をしている<sup>(5)</sup>。

いずれもC-C間の $\sigma$ 結合による高い機械的強度を持つとともに、 $\pi$ 結合に由来する面方向の電子伝導を示す。 $\pi$ 電子は、金属では表面散乱が顕著となる極微細領域でも、相対的に散乱の影響を受けにくい。理論的には、 $10\,\mathrm{nm}$ 幅を下回る微細領域においても抵抗率の顕著な上昇を生じないことが予測されており<sup>(6)</sup>、実験的にも、CNTとグラフェン細線はともにCuに対して桁違いに高い電流密度耐性、熱伝導率、平均自由行程などを示すことが報告されている (表1)<sup>(7)</sup>。

以上のような特徴から、ナノカーボン材料は新たな半導体 微細配線材料として研究が活発化しつつあるが、実際の配線

#### 表 1. Cuとナノカーボン材料の配線関連の物性比較

Interconnect-related properties of Cu. multiwall CNT, and graphene

| 項目                    |                      | 多層CNT                 | グラフェン                 | Cu                    |

|-----------------------|----------------------|-----------------------|-----------------------|-----------------------|

| 最大電流密度                | (A/cm <sup>2</sup> ) | > 1 × 10 <sup>9</sup> | > 1 × 10 <sup>9</sup> | < 1 × 10 <sup>7</sup> |

| 熱伝導率                  | (W/(cm·K))           | 3,000                 | 5,000                 | 385                   |

| 300 K における平均自由行程 (nm) |                      | > 25,000              | 1,200                 | 40                    |

へ適用するためには、半導体プロセスと整合した成長技術として、成長温度の低温化及びCNTの高品質化や高密度化が必要である。更に、配線集積化技術として、微細ビアホールへの成長や低抵抗の電極接合形成が不可欠である。次章では、これらの課題のうち、当社が取り組んできたCNTの低温高品質成長技術と高密度化技術、及び最小70 nm径の微細ビア集積プロセス技術について述べる。

## 3 CNTの低温高品質成長技術

CNTの成長には、触媒金属を形成した基板を600 ℃以上に加熱し、C源となるガスを導入して触媒上で反応させる化学気相反応法(CVD: Chemical Vapor Deposition)が用いられる。CVDによるCNT成長を半導体プロセスに適用するためには、低誘電率の絶縁膜を含む周囲の材料の耐熱性と整合する400 ℃以下への低温化が必要である。当社は、この低温化にプラズマCVDで取り組むとともに、プラズマCVDの課題であるCNT結晶品質の向上を図った。

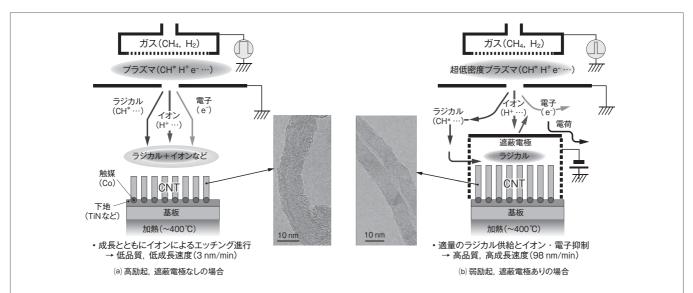

プラズマ発生源を含めたCVD装置の構成と、それにより成長させたCNTの透過電子顕微鏡 (TEM) 観察像を図3に示す<sup>(8)</sup>。

図3. プラズマCVDの構成と合成されたCNTのTEM写真 — 高励起プラズマを遮蔽電極なしで用いた場合、CNTは屈曲が多く低品質であった。パルス励起により弱励起とし、遮蔽電極を設けることで、品質、成長速度ともに向上した。

Remote-plasma chemical vapor deposition (CVD) schematics and transmission electron microscope (TEM) images of CNTs obtained by plasma CVD

C源ガスはメタン ( $CH_4$ ) で、これをキャリアガスの水素 ( $H_2$ ) とともにシャワーノズルから導入し、ノズルと対向電極との間に電圧を印加することでプラズマを生成した。図3(a)は、生成したプラズマをそのまま基板ステージに導いて反応させた基本構成で、プラズマなしでは反応しない400  $\mathbb C$  で  $\mathbb C$   $\mathbb C$

そこで、図3(b)のように、極微小パワーのパルス励起でプラズマを生成し、かつ遮蔽電極を用いて、イオンと電子の両成分をスクリーニングしたうえで基板ステージに導いた。これらの対策により、基板ステージ面でのイオン電流を3桁低減できた。この構成で得たCNTの結晶品質は大幅に改善され、成長速度も98 nm/minと約30倍に増大した。プラズマ生成量の最適化と基板面への電荷成分の遮蔽が、Cのエッチングを抑えて高品質化をもたらすとともに、結果として成長の高速化に寄与したと考えられる。

## 4 CNTの高密度成長技術

配線用CNTの成長において、低温化に次ぐ重要な課題はCNTの高密度化である。CNTは、同一断面積のCuに比べ、単体では高い電流密度耐性を示すが、ビア内では複数のCNTの束 (バンドル) として用いられるため、バンドル中のCNT密度が実際の密度耐性を決める。当社は、成長の低温化で培ったプラズマCVD技術を基に、多段階のプラズマ処理による世界最高の高密度成長 $2\times10^{12}$ 本/cm²を実現した。

3段階プラズマCVDによる成長プロセスを**図4**に示す<sup>(9)</sup>。一般に、CNTは基板上の触媒微粒子にほぼ等しい直径で成長する。したがってCNTの高密度成長には、触媒粒子の微細化と高密度化が第一の鍵となる。しかし、10<sup>12</sup>本/cm<sup>2</sup>を超える超高密度を得るには、触媒は10 nmを下回るナノサイズとなり、いったん形成した後も成長時の加熱で容易に凝集し、大粒化、低密度化するという問題があった。

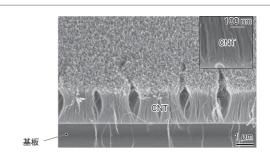

当社は図4に示すように、プラズマ照射で薄膜から高密度 微粒子を形成する (第1段階) とともに、比較的低い加熱温度 で C 源ガスプラズマ処理を行い、微粒子表面に C の核を形成した (第2段階)。このようにすることで、成長温度までの加熱時にも触媒微粒子の凝集が防止され、高密度の C N T バンドルを得ることができた (第3段階)。3段階法で成長した C N T の走査電子顕微鏡 (SEM) 観察像を図5に示す。C N T の本数密度は 1×10<sup>12</sup> 本/cm² と見積もられ、直線性の良好な C N T に特有のファンデアワールス力による集束構造が観察される。もっとも集束した部分でも断面積は基底部の50%程度と大きく、C N T の密度が理論上限近くまで到達しているこ

|      | 目的                 | プラズマ条件              |

|------|--------------------|---------------------|

| 第1段階 | ・触媒の微粒子化           | 高パワー<br>Ar又はH₂プラズマ  |

| 第2段階 | ・微粒子の固定<br>・CNTの成長 | 高パワー<br>CH4/H2プラズマ  |

| 第3段階 | ・CNTの成長            | 超低パワー<br>CH4/H2プラズマ |

図4. 3段階プラズマCVDによるCNTの高密度成長 ― 触媒のコバルト(Co) 層を薄膜で形成後,第1段階のプラズマ処理で触媒層を微粒子化し,第2段階で低温においてCの核を形成することで凝集を抑制し,第3段階で昇温後,高密度のCNTを成長させる。

High-density CNT growth applying 3-step plasma CVD

図5. 3段階プラズマCVDにより得た高密度CNTのSEM写真 — 450  $\mathbb{C}$ での成長例で,成長密度は $1\times10^{12}$ 本/cm $^2$ であった。直線性の良好なCNTに特有のファンデアワールス力による集束構造が見られる。

Scanning electron microscope (SEM) image of CNT obtained by 3-step plasma  $\ensuremath{\mathsf{CVD}}$

とが推測される。

更に、この3段階成長の発展形として、第1段階の次に窒素  $(N_2)$  + アルゴン (Ar) をプラズマ源とした処理を加え、触媒の 微細化と活性度の向上を狙った4段階成長法を開発しており、 CNT 密度を $2 \times 10^{12}$  本/cm² まで向上させることに成功した ( $^{(10)}$ )。

#### 5 CNTの微細ビア集積化技術

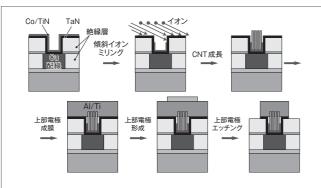

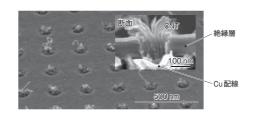

低温高密度成長CNTの配線集積化に向け、微細ビアへのCNT適用プロセスの開発を行った<sup>(11), (12)</sup>。 図6に示すように、Cu配線上の絶縁層に形成された最小直径70 nmのビアホールに、Cu配線の拡散防止と触媒活性の向上を狙った窒化チタン(TiN)/窒化タンタル(TaN)の積層膜を形成し、その上にコバルト(Co)の触媒層を形成する。次いで、基板に対して斜め方向からArイオンを照射する傾斜イオンミリングにより、ビアホール底以外の触媒を除去する。この後に多段階CVD成長を行うことで、ビアホール部にだけ選択的にCNTを成長させた。CNTを形成した70 nmビアアレイのSEM像を図7に

図6. 微細ビアへのCNT適用プロセス — 触媒を基板全面に形成後、 イオンミリングによりビアホール底部以外の触媒を除去する。次いでビア ホール部にだけCNTを成長させ、最後に上部電極を形成する。

CNT via integration process

図7. 微細ピアアレイに選択成長したCNTのSEM写真 — 多段階プラズマCVDによって微細ピアアレイに選択成長させたCNTのバンドルである。 SEM image of selective CNT growth into via array

示す。ビア部にだけCNTが観察され、絶縁層領域には成長していないことがわかる。最後に上部電極(アルミニウム(Al)/Ti)を形成してビア配線構造を完成させる。この方法は、成長したCNTにそのまま電極を重ねる簡易的な段階であるが、実際の多層配線構造に適用するためにはCNTビアの平たん化加工が必要である。現在、成長後のCNTを塗布型ガラス(SOG:Spin on Glass)で固め、化学機械平たん化(CMP:Chemical Mechanical Planarization)の適用プロセスの開発を進めている。

#### 6 あとがき

微細化や3次元化の進むLSIや半導体メモリへの適用を目指すナノカーボン配線技術の可能性と課題,及び開発成果について述べた。

ナノカーボン材料の中でも、CNTはそれ自体が持つ高アスペクト比構造から、微細で深い縦方向配線への適用が期待される。プラズマの超低パワー化や電荷成分低減により、半導体プロセスに求められる低温で高品質なCNTの成長を可能にした。また、プラズマ処理の多段階化により、多層CNTとして世界最高の高密度成長2×10<sup>12</sup>本/cm²と微細なビアホールへの成長を実現した。今後は、微細低抵抗配線としての機

能実証に向け、CNTと電極との低抵抗接合形成などの開発を 進めていく必要がある。更に、横方向の汎用微細配線への適 用が期待されるグラフェン配線を開発し組み合わせることで、 3次元メモリの高集積化への貢献を目指す。

この研究は、NEDOの「次世代半導体材料・プロセス基盤 (MIRAI) プロジェクト」において実施した。

# 文 献

- Steinhoegl, W., et al. Comprehensive study of the resistivity of copper wires with lateral dimensions of 100 nm and smaller, J. Appl. Phys. 97, 2, 2005, p.023706-1 - 023706-7.

- International Technology Roadmap for Semiconductors. "ITRS 2009 Edition". ITRS. <a href="http://www.itrs.net/Links/2009ITRS/Home2009.htm">http://www.itrs.net/Links/2009ITRS/Home2009.htm</a>, (accessed 2011-01-20).

- (3) 栗野祐二. カーボンナノチューブのLSIデバイスへの応用. 応用物理. 76, 10, 2007, p.1112-1122.

- (4) Geim, A. K.; Novoselov, K. S. The rise of grapheme. Nature Mat. 6, 3, 2007, p.183-191.

- Iijima, S. Helical microtubules of graphitic carbon. Nature. 354, 1991, p.56 - 58.

- (6) Naeemi, A.; Meindl, J. D. Conductance Modeling for Graphene Nanoribbon (GNR) Interconnects. IEEE EDL. 28, 2007, p.428 - 431.

- (7) Banerjee, K., et al. "Current Status and Future Perspectives of Carbon Nanotube Interconnects". 8th IEEE Conference on Nanotechnology. Arlington, Texas USA, 2008-08, IEEE, 2008, p.432 - 436.

- (8) Yamazaki, Y., et al. High Quality Carbon Nanotube Growth at Low Temperature by Pulse-Excited Remote Plasma Chemical Vapor Desposition. Applied Physics Express. 1, 2008, p.034004-1 - 034004-3.

- (9) Yamazaki, Y., et al. Synthesis of a closely packed carbon nanotube forest by a multi-step growth method using plasma-based chemical vapor deposition. Applied Physics Express. 3, 2010, p.055002-1 - 055002-3.

- (10) Yamazaki, Y., et al. "Extremely high-density carbon nanotube growth for interconnect application". Abstract DIAMOND 2010. Budapest, Hungary, 2009-09, Elsevier, 2010, p.O20.

- (11) Katagiri, M., et al. "Fabrication of 70-nm-diameter Carbon Nanotube Via Interconnects by Remote Plasma-Enhanced Chemical Vapor Deposition and Their Electrical Properties". Proc. IITC 2009. Sapporo, Japan, 2009-06, IEEE, 2009, p.44 - 46.

- (12) Katagiri, M., et al. "Improvement in Electrical Properties of Carbon Nanotube Via Interconnects". Proc. ADMETA 2010. Tokyo, Japan, 2010-10, Japan Society of Applied Phsics, 2010, p.10 - 11.

#### 酒井 忠司 SAKAI Tadashi

研究開発センター 電子デバイスラボラトリー研究主幹。 カーボン系材料の電子デバイス応用に関する研究・開発に従事。 応用物理学会会員。

Electron Devices Lab.

#### 山崎 雄一 YAMAZAKI Yuichi, D.Eng.

研究開発センター 電子デバイスラボラトリー研究主務, 博士 (工学)。 カーボン系材料の電子デバイス応用に関する研究・開発に従事。 応用物理学会会員。

Electron Devices Lab.

## 片桐 雅之 KATAGIRI Masayuki, D.Ph.

研究開発センター 電子デバイスラボラトリー 研究主務, 博士 (学術)。 カーボン系材料の電子デバイス応用に関する研究・開発に従事。 応用物理学会会員。

Electron Devices Lab.