一般論文 FEATURE ARTICLES

# 小面積・低消費電力・高速 A/D変換器

Small-Area Analog-to-Digital Converter Offering Low Power Consumption and High Speed

古田雅則野澤舞を紹介をおります。

■ FURUTA Masanori

■ NOZAWA Ma

■ITAKURA Tetsuro

CMOS (相補型金属酸化膜半導体) の微細化が進むなか, アナログ回路の面積低減の要求が加速度的に増加している。 最近のアナログ回路は, キャパシタなどの受動素子により面積が決まっている。 従来は, キャパシタの素子値そのものを小さく する小型化のアプローチを取っていたが, この方法では, 集積回路製造上の制約や素子の特性ばらつきの観点から課題があった。

今回, 無線LANなどの無線受信IC用途に向けた, 分解能<sup>(注1)</sup>10ビット, サンプル周波数<sup>(注2)</sup>40メガサンプル (MS)/sのアナログ デジタル変換器 (ADC) において, 大きな受動素子を用いながらも回路全体の面積を小型化できる回路技術を開発した。逐次比較 (SAR) 型を基本とした変換器で, 回路構成の工夫により, 省電力化を図りながら 0.06 mm² という世界最小サイズ<sup>(注3)</sup>を実現した。

High-resolution successive-approximation-register (SAR) analog-to-digital converters (ADCs) with a charge-redistribution digital-to-analog converter (DAC) are widely used in low-power applications, including complementary metal-oxide semiconductor (CMOS) wireless communication receivers, sensor networks, and medical instrumentation. With the progress of CMOS nanofabrication technologies, demand has been increasing for miniaturization of the circuit area of SAR ADCs consisting of analog and mixed signal integrated circuits (ICs) to reduce costs.

Toshiba has developed a miniaturization technology that makes it possible to reduce the total circuit area by means of a pipelined architecture despite the use of large passive devices, and has fabricated a prototype 10-bit, 40 megasamples/s SAR ADC. This 10-bit SAR ADC realizes the world's smallest active area of 0.06 mm<sup>2</sup> and a low power consumption of 1.21 W, achieved by innovation of the circuit configuration.

## 1 まえがき

通信分野、映像分野などで使われるICの開発では、アナログとデジタルの信号処理回路を1チップに混載させる需要が高く、両回路のインタフェースであるADCの重要性も依然として高い。省エネと低コストを強く求められる最近のIC開発では、要素回路の低消費電力化と小面積化が不可欠である。システムLSIを構成する要素回路の中でも、ADCは比較的消費電力、実装面積が大きく、この二つの改善が課題である。

以前から、消費電力と面積の課題を解決するための様々な 回路方式が開発されてきた。その一つの方式であるSAR型 は、最近、特に消費電力の削減に有利な回路方式として注目 されている。例えば、通信用途に開発されたものには、消費 電力が従来の約1/5のものが発表されている。SAR型の特 徴は、アナログ回路として従来は能動素子を使用してきた回 路を、受動素子を使用する回路に置き換えたことにある。し かし、受動素子の面積が大きく、小面積化が課題であった。

東芝は、無線LANなどの無線受信IC用に、小面積化と低消費電力化を目的とする分解能10ビット、サンプル周波数40MS/sを実現したSAR型ADCを開発した。従来のSAR型

ADCの課題であった,高い分解能を実現する際の受動素子の面積削減を実現するため、2段縦続接続式の回路構成を開発した。この回路を、65 nmCMOS技術を用いて試作を行い、面積削減の効果と性能の確認を行った。

ここでは、最近のADCの開発動向について述べた後、開発した2段縦続接続式SAR型ADCの概要と試作チップによる性能評価の結果について述べる。

# 2 ADCの開発動向とSAR型ADCの原理

### 2.1 ADCの開発動向

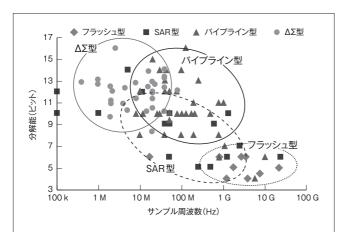

従来から、ADCを実現する回路として様々な方式が開発されており、これらは大きく $\Delta\Sigma$  (デルタシグマ)型、パイプライン型、SAR型、及びフラッシュ型の4種類のアーキテクチャに分類することができる。

図1は、主要な国際学会で過去5年間に発表された論文からADCの開発動向を見たもので、ADCの性能の中からサンプル周波数と分解能を抽出し、更に、前記の四つのADCアーキテクチャに分類し図示した。ADCに関する発表件数は多く、サンプル周波数、分解能も様々であるものの、アーキテクチャによりそれぞれ得意な領域があり、開発もアーキテクチャごとの特徴を生かした方針で行われている。 $\Delta \Sigma$ 型は高分解能で低サンプル周波数、フラッシュ型は低分解能で高速領域

<sup>(</sup>注1) アナログ信号をデジタル信号に変換する際の電圧の細かさ。

<sup>(</sup>注2) アナログ信号をデジタル信号に変換する際の速度。

<sup>(</sup>注3) 2010年2月のISSCC (国際固体素子回路会議)で発表、当社調べ。

図1. ADC の開発動向 — 主要な国際学会の発表論文から性能について分解能とサンプル周波数を抽出し、四つのアーキテクチャに分類した。

Trends in ADC development

での報告が多い。また、通信や映像の分野で求められる分解能8~10ビット、サンプル周波数50~200 MS/sの領域は、パイプライン型とSAR型の2方式による発表が多い。

分解能10ビット、サンプル周波数40 MS/sの性能を持つ ADCは、低消費電力化の要求が強い特に通信用途向けとし て開発が進んでいる。この用途のADCは、従来はパイプライ ン型が主力であったが、最近はSAR型の開発に関する発表 が多い。主な理由は、パイプライン型では能動素子で構成さ れる高性能な増幅器が複数必要であるのに対し、SAR型では 同じ機能を受動素子であるキャパシタ (容量デバイス) で置換 え可能な点である。これにより、パイプライン型の能動素子で 消費していた電力を削減することができる。回路の性質上、 制御ロジックの周波数がサンプル周波数の上限を決めており、 以前はサンプル周波数の向上が課題であったが、CMOS製造 技術の進歩によりこの課題が解決されてきた。パイプライン 型ADCと同じ分解能かつサンプル周波数のものが、微細 CMOS製造技術を用いることにより、約1/5の消費電力で実 現できている。一方、受動素子には、集積回路製造上の制約 や特性ばらつきの観点から大きな面積が必要であり、その改 善が課題である。

### 2.2 SAR型ADCの原理

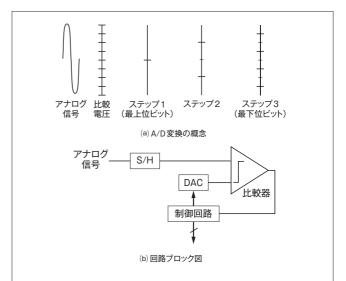

SAR型ADCの概念と回路ブロック図を図2に示す。基本原理は、2分探索法によるアナログデジタル(A/D)変換である。回路は、サンプルホールド(S/H)、デジタルアナログ変換器(DAC)、比較器、及び制御回路により構成される。S/H回路は入力信号を一定期間保持し、DACは図2(a)のように、2分探索のための基準電圧を生成するのに用いられる。この二つの信号を比較器により複数回比較することで、高い分解能のデジタル信号(入力信号>基準電圧のときは1、それ以外のときは0)が得られる。SAR型ADCでは、比較動作のための基準電圧が複数必要となり、今回は、基準電圧生成方法の一

図2. SAR型 ADC の A/D 変換の概念と回路ブロック図 — 2分探索法によりステップ 1から3で比較電圧を生成する (3ビットのSAR型 ADC の例)。回路はS/H, DAC, コンパレータ, 及び制御ロジックで構成され、DAC 回路の設計しだいで任意の分解能が得られる。

Principle of analog-to-digital (A/D) conversion and block diagram of SAR ADC

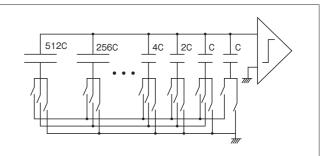

図3. 10ビットSAR型ADCにおけるキャバシタDACのブロック図 — Cに対し、2のべき乗の重みが付けられる。

Block diagram of capacitor DAC in 10-bit SAR ADC

つである電荷再配分技術を採用した。この方法では、S/HとDACをキャパシタとスイッチで構成でき、電力を常時必要とするアナログ回路が比較器だけとなるため、省電力化に優れた回路を実現できる。

SAR型ADCの具体的な回路を図3に示す。ADCの分解能は、無線LANの要求仕様から10ビットに設定した。2分探索のための電圧生成は、それぞれのキャパシタを単位容量値(C)に2のべき乗の重みを付けたものにすることで実現する。2分探索を正確に行うための重要なポイントは、キャパシタを2のべき乗の重みでばらつきなく製造することである。キャパシタの製造ばらつきにより各キャパシタ間でアンバランスが生じると、各ビット判断に用いる基準電圧が正確に得られず、誤判断につながる。

前述の制約条件に基づく回路設計の問題は、キャパシタの面積が大きいということで、図3の構成ではCを持つ基本キャパシタが全部で2<sup>10</sup>=1,024個必要となる。また、プロセスのばら

つきによるアンバランスを回避するため、ある程度大きいCが 必要になる。

## 試作チップによる性能評価

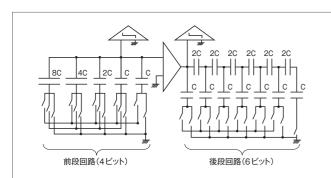

#### 3.1 回路設計

試作した2段縦続接続式SAR型ADCのブロック図を図4 に示す。面積を低減するためには、使用する基本キャパシタの 数を削減することが必要であり、これを実現するため、10ビッ トのSAR型ADCを4ビットと6ビットに分割した。これによ り、単純に24+26=80個にまで削減できるが、今回は、更なる 面積低減のため、後段回路を直並列の接続にしたことで、後 段のキャパシタの数を36個にまで削減できた。その結果、開 発したSAR型ADCでは、キャパシタの総数を従来比で70% 削減できた。

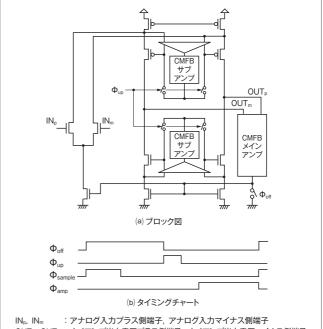

この回路では、前段から後段に向けて信号を受け渡すオペ アンプが必要である。オペアンプのブロック図とタイミング チャートを図5に示す。折返しカスコード回路を基本としたゲ インブースト型のオペアンプで、一般的な構成と比べ、メイン アンプのコモンモード制御端子とゲインブースト用のサブアン プの出力端子にスイッチが設けてある。OFF制御信号Φ off が "1" のとき、オペアンプは低消費電力モード (電源 OFF) に入 り、 $\Phi_{\text{off}}$ が "0" のときに回路は動作する。これにより、常時 ONの状態と比べて消費電力を30%低減できた。

ゲインブースト型のオペアンプの問題は、回路がOFF状態 からON状態へ復帰する時間が長い点である。この原因は、 サブアンプが復帰後にメインアンプが復帰することにある。 これを解決するため、二つのサブアンプの出力を適切なバイア ス電圧にいったんセットするスイッチを設けた。これにより、 約1 nsの時間でOFF状態からON状態に復帰可能となった。

## 3.2 評価結果

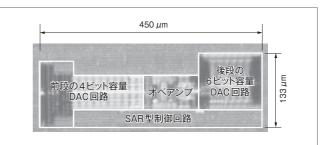

試作チップを図6に示す。図の左側が前段、右側が後段に あたり、中間に位置するのがオペアンプである。10ビットの

図4. 開発した回路のブロック図 - 前段は4ビット、後段は6ビットの 2段縦続接続式SAR型ADCのキャパシタDACの構成である。中間のオ ペアンプは残差演算に使用する。

Block diagram of newly developed SAR ADC

OUT<sub>p</sub>, OUT<sub>m</sub>: オペアンプ出力電圧プラス側端子, オペアンプ出力電圧マイナス側端子

CMFB コモンモード フィードバック回路 オペアンプをOFFする制御信号  $\Phi_{\text{off}}$

:オペアンプをOFF状態からON状態に復帰する制御信号 Фир

· : 入力信号サンプルの制御信号 Феат

:前段から後段へ信号を受け渡しする演算のための制御信号  $\Phi_{\text{amp}}$

図5. オペアンプのブロック図とタイミングチャート - 2段縦続接続式 SAR型 ADC でオペアンプの動作が必要なのは $\Phi_{amp}$ が "1" の期間だけで ある。この回路では、 $\Phi_{off}$ という制御信号でオペアンプをOFF状態にし ているため、常時 ON 状態のオペアンプと比べ消費電力が低減される。

Block diagram of operational amplifier and related timing diagram

図6. 試作チップの回路写真 - 65 nmCMOS技術により試作した。2段 式にすることで受動素子の面積が低減でき、小面積に集積できた。

Prototype SAR ADC chip

SAR型 ADCを65 nmCMOS技術により試作したところ、面 積は0.06 mm<sup>2</sup>となった。

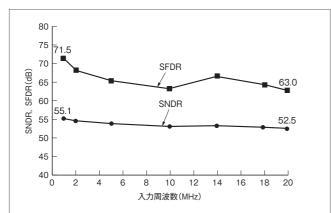

この試作チップについて動的特性であるSNDR (Signal-to-Noise plus Distortion Ratio) & SFDR (Spurious-Free Dynamic Range) を測定した結果を図7に示す。測定時の電源 電圧は1.1 Vで、サンプル周波数は40 MS/sである。入力信号 周波数が1 MHzのときのSNDR、SFDRはそれぞれ55.1 dB と71.5 dBであり、入力信号周波数が20 MHzのときのSNDR、 SFDR はそれぞれ 52.5 dB と 63.0 dB であった。 実行分解能の

図7. SNDRとSFDRの測定結果 — SNDRとSFDRの入力信号周波数依存性を測定したもので、サンプル周波数は40 MS/sである。入力周波数がナイキスト周波数 (サンプル周波数の半分) まで良好なひずみ特性を維持できている。

Results of measurement of signal-to-noise plus distortion ratio (SNDR) and spurious-free dynamic range (SFDR) (at 40 megasamples/s)

#### 表 1. 試作チップの性能評価結果

Results of performance evaluation of prototype chip

| 項目                      | 評価結果                                              |

|-------------------------|---------------------------------------------------|

| デバイスプロセス                | 65 nm CMOS                                        |

| ADC実装面積                 | 0.06 mm² (450 μm × 130 μm)                        |

| サンプリング周波数               | 40 MS/s                                           |

| 電源電圧                    | 1.1 V                                             |

| 入力レンジ                   | 1.0 V <sub>p-p</sub> , differential               |

| 0 dBフルスケール入力時の<br>SNDR  | 55.1 dB (入力周波数1 MHz 時)<br>52.5 dB (入力周波数20 MHz 時) |

| 0 dBフルスケール入力時の<br>SFDR  | 71.5 dB (入力周波数 1 MHz時)<br>63.0 dB (入力周波数 20 MHz時) |

| 実行分解能                   | 8.9ビット                                            |

| 消費電力                    | 1.21 mW (アナログ: 0.6 mW, デジタル: 0.61 mW)             |

| 1ビット・1変換周波数<br>当たりの電力効率 | 65 fJ/conversion-step                             |

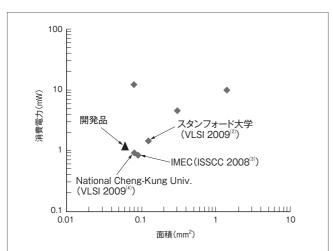

図8. 他研究機関のADCとの比較 — 同様の性能を持つ世界トップクラスのADCと比べ、消費電力を同等としながらも、実装面積を最小にできた。 Comparison of area and power consumption of ADCs with comparable performance

ピーク値は8.9 ビットで、無線LANの要求仕様ともマッチする。消費電力は1.21 mW であった。性能の評価結果をまとめて**表1** に示す。

この試作チップの面積と消費電力を,同等の性能を持つ他のADCと比較した結果 (2010年1月時点)を図8に示す。国際学会で今までに発表されたトップクラスの製品と同等の消費電力を実現できており,面積では世界最小サイズを実現できた<sup>(1)</sup>。

# 4 あとがき

当社は、65 nmCMOS技術を用い、無線LANなどの無線受信IC用途に向けた、分解能10ビット、サンプル周波数40 MS/sの世界最小サイズのSAR型ADCを開発した。2段縦続接続構成を採用することで、10ビットの分解能を0.06 mm²という小面積で実現し、OFF状態からON状態に高速で復帰できるスイッチングオペアンプにより、1.21 mWという世界トップクラスの低消費電力を実現した。

今後は、次世代の無線通信用を目指し、更なる高速化を進めていく。

# 文 献

- Furuta, M., et al. "A 0.06mm<sup>2</sup> 8.9b ENOB 40MS/s pipelined SAR ADC in 65nm CMOS". ISSCC 2010 Tech. Dig. Tech Papers. San Francisco, 2010-02, IEEE. p.382-383.

- (2) Hu, J., et al. "A 9.4-bit, 50-MS/s, 1.44-mW pipelined ADC using dynamic residue amplification". VLSI Circuits, 2008 IEEE Symposium. Honolulu, 2008-06, IEEE. p.216 - 217.

- (3) Giannini, V., et al. "An  $820\,\mu$ w 9b 40MS/s Noise-Tolerant Dynamic-SAR ADC in 90nm Digital CMOS". ISSCC 2008 Tech. Dig. Tech Papers. San Francisco, 2008-02, IEEE. p.238 610.

- (4) Liu, C., et al. "A 0.92mW 10-bit 50-MS/s SAR ADC in 0.13 µm CMOS process". VLSI Circuits, 2009 IEEE Symposium. Kyoto, 2009-06, IEEE. p.236 237.

#### 古田 雅則 FURUTA Masanori, D.Eng.

研究開発センター ワイヤレスシステムラボラトリー研究主務, 工博。高速・低消費電力A/D変換器の開発に従事。IEEE 会員。

Wireless System Lab.

# 野澤 舞 NOZAWA Mai

セミコンダクター社 半導体研究開発センター 先端回路技術 開発部。高速・低消費電力A/D変換器の開発に従事。 Center for Semiconductor Research and Development

## 板倉 哲朗 ITAKURA Tetsuro, D.Eng.

研究開発センター ワイヤレスシステムラボラトリー研究主幹, 工博。LCD用ドライバ, RFアナログLSI, デジタル信号処理 回路の開発に従事。IEEE, 電子情報通信学会会員。 Wireless System Lab.