一般論文 FEATURE ARTICLES

# シリコン (100) 及び (110) 面上 CMOSFETの ひずみによる高電界キャリア速度変調

Modulation of High-Field Carrier Transport by Strain in Si(110) and (100) CMOSFETs

齋藤 真澄 沼田 敏典

■ SAITOH Masumi

■ NUMATA Toshinor

近年、LSIの更なる高性能・低消費電力化に向けて、素子の微細化に頼らずにMOSFET (金属酸化膜半導体型電界効果トランジスタ)の性能を向上させるテクノロジーブースタ技術に注目が集まっている。有力なブースタ技術としては、チャネルひずみ技術と面方位技術 ((110) 面 CMOSFET (相補型MOSFET) 技術) が検討されているが、この二つの技術を短チャネルデバイスに導入した際の性能向上についてはまだ十分な理解がなされていない。

今回、機械ひずみを導入した短チャネル (110) 面MOSFETの電流評価を行った。 ひずみによる短チャネルデバイスの電流 増加が、 ひずみによる低電界移動度の変化と飽和速度 (高電界輸送) の変化の両方によって決定されることを見いだした。 更に、 ひずみ (110) 面 CMOSFETが従来の (100) 面 CMOSFETに対して高い性能を示すことを明らかにした。 ひずみ (110) 面 CMOSFET 技術は、 次世代以降の高性能・低消費電力 LSIの実現に向けて非常に有望である。

In recent years, technology boosters, which enhance the performance of metal-oxide-semiconductor field-effect transistors (MOSFETs) without scaling of the device size, have attracted attention to the development of large-scale integrations (LSIs) with higher performance and lower power consumption. Although channel strain engineering and surface orientation engineering ((110)-plane complementary MOSFETs (CMOSFETs)) have been considered to be promising boosters, performance improvement in short-channel strained (110) MOSFETs using these technologies has not yet been fully elucidated.

Toshiba has measured drain current in short-channel (110) MOSFETs with mechanically applied strain and found that the increase in current caused by strain in short-channel devices is induced by both a change in the low-field mobility and modulation of the saturation velocity resulting from the strain. We have also demonstrated that the strained (110) MOSFETs are superior to the conventional (100) MOSFETs. The strained (110) MOSFETs are highly promising for the realization of LSIs offering higher performance and lower power consumption in future technology nodes.

#### 1 まえがき

LSIを構成する基本デバイスであるMOSFETの性能向上は、これまで素子サイズの微細化によって実現されてきた。しかし近年では、微細化が限界に到達しつつあり、微細化以外のトランジスタの性能向上技術(テクノロジーブースタ)が注目を集めている。数あるテクノロジーブースタの中でも、トランジスタの性能に直結する電流量を大きく増加させる技術として、チャネルひずみ技術と面方位技術が有力である。チャネルひずみ技術は、トランジスタのチャネル部に格子ひずみを導入してシリコンのバンド構造を変化させることによって、低電界移動度(電流量を決める物性値)を増加させるものであり、既に実用化されている。一方、面方位技術は、トランジスタを作製する基板の面方位を従来のシリコン(100)面からシリコン(110)面に変更することで、p型トランジスタ中のキャリアである正孔の移動度を増加させる技術である(1)。

高性能LSIを実現するには、この二つの技術を組み合わせたひずみ (110) 面トランジスタを導入することが望ましいと考えられるが、現状、ひずみ (110) 面トランジスタの性能については十分な理解がなされていない。具体的には、ゲート長の

長いトランジスタでの低電界移動度評価は行われているものの、実際のLSIで用いられるゲート長の短い短チャネルトランジスタの性能(電流)評価の報告例は少ない。短チャネルデバイスでは、チャネル中に高い横方向電界が生じるため、チャネルを流れるキャリアが大きなエネルギーを獲得し、高電界特有のキャリア輸送現象が発現する。ひずみ(110)面トランジスタでこの高電界輸送現象を正しく理解することは、高性能トランジスタ実現のために不可欠である。

そこで、試作した短チャネル (110) 面トランジスタに機械的な応力を印加して電流測定を行い、ひずみが短チャネルデバイスの高電界輸送に与える影響を詳細に調べた<sup>(2)</sup>。ひずみによる電流変調の物理的起源を明らかにするとともに、ひずみによる (110) 面 CMOSFET 回路の性能向上を予測した。

## 2 ひずみによる短チャネル (110) 面 MOSFETの 電流・速度変化の測定結果

ここでは、バルクシリコン基板上に作製したMOSFETを用いて実験を行った。ゲート材料はポリシリコン、ゲート絶縁膜は酸化膜換算膜厚1nmのSiON(酸窒化シリコン)とし、ゲート

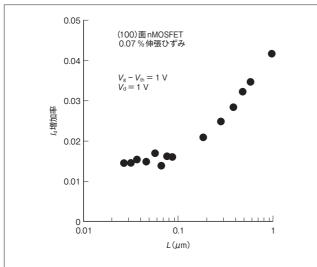

図1. (100) 面nMOSFETでの伸張ひずみによるドレイン電流増加率のゲート長依存性の測定結果 — ゲート長の縮小とともにドレイン電流増加率は低下する。

Dependence of gate length on drain current caused by tensile strain in (100) negative-channel MOSFET (nMOSFET)

幅は $1\mu$ mで、ゲート長Lは $10\mu$ mから25nmまで変化させた。MOSFETが作製されている基板を機械的に曲げて応力を印加し、応力によるドレイン電流の増加率を測定した。 (100) 面nMOSFETで0.07%のゲート長方向伸張ひずみを導入したときのドレイン電流増加率のゲート長依存性を**図1**に示す。ドレイン電圧 $V_d$ は1V、ゲート電圧 $V_g$ としきい値電圧 $V_{th}$ の差は1Vに固定している。

古くから知られているように、nMOSFETのドレイン電流は伸張ひずみによって増加するが、その電流増加率はゲート長とともに低下する。すなわち、ゲート長が短くなるほど、ひずみの効果が弱まってしまう。一般に、ドレイン電流を $I_d$ とすると、式(1)に示すように $I_d$ は電荷素量 $\mathbf{q}$ (定数)、キャリア密度 $N_{inv}$ キャリア速度vの積として表せる。

$$I_{\rm d} = \mathbf{q} \cdot N_{\rm inv} \cdot \mathbf{v} \tag{1}$$

ひずみによるキャリア密度の増加は小さいため、図1の電流 増加率はひずみによる速度の増加率にほぼ等しい。つまり、 ひずみによる速度増加率がゲート長とともに低下するというこ とであり、その原因を明らかにする必要がある。

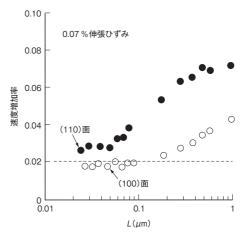

(100) 面nMOSFETと 同様 に, (100) 面pMOSFETと (110)面n及びpMOSFETでも, ひずみによる電流 (速度) 増加率を測定した。nMOSFETにゲート長方向伸張ひずみを導入した場合,及びpMOSFETにゲート長方向圧縮ひずみを導入した場合の速度増加率を図2に示す。

いずれのデバイスでも、ゲート長縮小とともに速度増加率が低下していく傾向が見られている。しかし、ゲート長が100 nm以下の領域に注目すると、(100)面nMOSFET及び(110)面pMOSFETの場合には速度増加率が飽和する傾向があり、

(a) nMOSFET にゲート長方向伸張ひずみを導入した場合

(b) pMOSFET にゲート長方向伸張ひずみを導入した場合

図2. (100) 面と (110) 面のn及びpMOSFETでの伸張と圧縮ひず みによる速度増加率のゲート長依存性の測定結果 — ゲート長  $100\,\mathrm{nm}$ 以下の領域では、4種類ともデバイスの速度増加率が収束する傾向がある。

Dependence of gate length on carrier velocity caused by tensile and compressive strain in (100)/(110) nMOSFET/positive-channel MOSFET (pMOSFET)

(110) 面nMOSFETの速度増加率は (100) 面nMOSFETの速度増加率に、(100) 面pMOSFETの速度増加率は (110) 面pMOSFETの速度増加率にそれぞれ接近していく。最終的に4種類のデバイスの速度飽和率はほぼ同程度の値 (0.02) に収束していく。

## 3 ひずみによる短チャネル (110) 面 MOSFETの 速度変調の起源

前章で得られたひずみによる速度増加率についてその決定 要因を考える。長チャネルMOSFETでは、おおまかにはドレイン電圧をゲート長で割り算した値に当たる横方向電界が低いため、キャリア速度は低電界移動度にほぼ比例する。このため、ひずみによる速度増加率はひずみによる移動度増加率

図3. 短チャネルMOSFETでのキャリア伝導の模式図 — 短チャネルでのキャリア輸送は、低電界移動度と飽和速度の両方によって決定される。 Schematic of carrier transport in short-channel MOSFETs

にほぼ等しい。既に報告されているように $^{(3),(4)}$ , ひずみによる移動度増加率は、(110) 面nMOSFETのほうが (100) 面nMOSFETよりも大きく、(100) 面pMOSFETのほうが (110) 面pMOSFETよりも大きい。図2のゲート長1 $\mu$ mにおける速度増加率の大小関係は、この移動度増加率の大小関係をそのまま反映したものになっている。

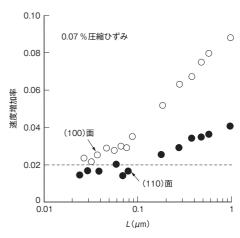

一方、短チャネルMOSFETでは、横方向電界が高くなるため、速度の変化を移動度の変化だけで説明することはできない。短チャネルMOSFETでのキャリア伝導の模式図を図3に示す。ソースからチャネルに注入されたキャリアは、ソース端付近のチャネルポテンシャルが熱エネルギー分だけ低下する領域(以下、kT層と呼ぶ)内で散乱を受け、一部のキャリアはソースへ戻される。kT層内での散乱の強さは低電界移動度によって決まる。すなわち、移動度が高いほど散乱が少ない。

kT層を通過したキャリアはkT層を越えた高エネルギー領域で更なる散乱を受ける。この散乱によってキャリア速度が頭打ちする現象を"速度飽和"と呼ぶ。このkT層を越えた領域での散乱は、高電界輸送を特徴づける物性値である、キャリアの飽和速度によって決まる。すなわち、飽和速度が高いほど散乱が少ない。

短チャネルMOSFETでは、ひずみによって移動度が増加してもこの速度飽和の影響によりそれが速度の増加に反映されにくくなるため、ひずみによる速度増加率が低下してしまう。ただ、単に速度飽和現象を仮定しただけでは、(100)面と(110)面n及びpMOSFETでの速度増加率低下はすべて同じように生じるはずであり、短チャネルですべてのデバイスの速度増加率が収束する図2の傾向は説明できない。

今回, 短チャネルMOSFETでのひずみによる速度増加率に, ひずみによる飽和速度の変化も影響していることを初めて明らかにした。 ひずみによる飽和速度の変化は, デバイスシミュレーションの結果を実測の電流データに合わせ込む手法 (インバースモデリング) を用いて, 抽出した。 今回のシミュ

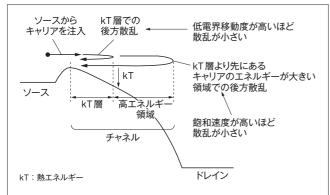

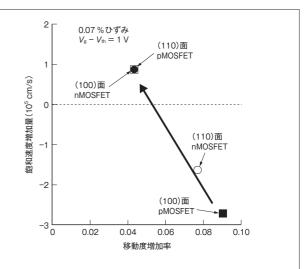

図4. (100) 面と (110) 面のn及びpMOSFETでのひずみによる移動 度増加率と飽和速度増加量の関係 — ひずみによる低電界移動度増加率 が低いほど、ひずみによる飽和速度増加量が大きい。

Relationship between mobility enhancement ratio and saturation velocity change caused by strain in (100)/(110) n/pMOSFET

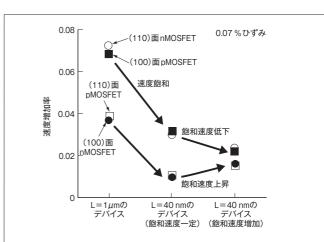

図5. (100) 面と (110) 面のn及びpMOSFETでのひずみによる速度 増加率のまとめ — 短チャネルでは、ひずみによる移動度増加率の差を飽 和速度の変化が相殺し、すべてのデバイスの速度増加率が収束する。

Summary of velocity enhancement ratio caused by strain in (100)/(110) n/pMOSFET

レーションでは、ドリフト拡散モデルを用いており、モデル中の飽和速度の値をパラメータとして合わせ込みを行った。 (100) 面と (110) 面n及びpMOSFETについて飽和速度の増加量を抽出した結果を図4に示す。 図4の縦軸はひずみによる飽和速度の増加量、横軸はひずみによる低電界移動度の増加率である。 ひずみによる低電界移動度増加率が低いデバイス ((100) 面nMOSFET, (110) 面pMOSFET) ではひずみによって飽和速度が増加する一方、移動度増加率が高いデバイスではひずみによって逆に飽和速度が低下している。

ひずみによる速度増加率の決定要因を図5にまとめる。ゲート $長1\mu m$ (長チャネル)のデバイスでは、速度増加率は移動

度増加率だけによって決まるが、ゲート長40 nm (短チャネル) のデバイスでは速度増加率は速度飽和の影響によって低下する。かりに飽和速度がひずみによって変化しないとすると、移動度増加率の低いデバイス((100) 面nMOSFET, (110) 面pMOSFET) の速度増加率は非常に低い値になってしまうが、実際にはこれらのデバイスでは飽和速度が増加するので、移動度増加率の低さが飽和速度増加によって補われ、すべてのデバイスでの速度増加率は収束していく。

### 4 ひずみ (110) 面 CMOSFET の性能予測

これまでは、基板曲げ実験の結果をもとに0.07%程度の小さなひずみを導入した際の(110)面MOSFETの電流変化を検討したが、実際の先端LSIでは1%程度の大きなひずみをプロセス技術によって導入している。そこでここでは、前章で抽出したひずみによる飽和速度の増加量をもとに、1%のひずみを導入したときの(110)面CMOSFETの性能をデバイスシミュレーションで予測した。

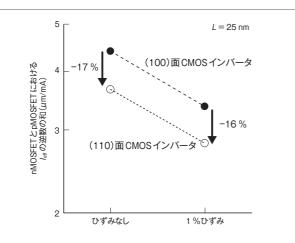

CMOSインバータ回路の遅延時間の指標とされる量である、nMOSFETとpMOSFETにおける実効ドレイン電流  $I_{eff}$ の遊数の和について、ひずみなしと1%ひずみの状態で計算した結果を比較して**図6**に示す。ゲート長は25 nm、実効的なゲート酸化膜厚は1.3 nmを仮定している。(100) 面、(110) 面のどちらの場合もひずみによって遅延時間が減少する。すなわち、回路の動作速度が向上する。しかし、ひずみ(110)面CMOSインバータの遅延時間はひずみ(100)面CMOSインバータに比べて16%小さく、ひずみのない状態での(110)面CMOSFETの優位性は、1%という大きなひずみを導入した状態でも維持

図6. (100) 面及び (110) 面 CMOS インバータ遅延時間のひずみ依存性の計算結果 — インバータの遅延時間はnMOSFETとpMOSFETにおける実効ドレイン電流の逆数の和に比例する。ひずみなし状態での (110) 面 CMOSFETの (100) 面 CMOSFETに対する優位性は、1%ひずみ状態でも維持される。

Calculated strain dependence of (100) and (110) CMOS inverter delay time

されることがわかる。これは前章で述べたように、短チャネルでのひずみによる速度増加率、すなわちドレイン電流増加率が、(100)面と(110)面のn及びpMOSFET すべてでほぼ同程度だからである。

#### 5 あとがき

ひずみによる短チャネル (110) 面トランジスタの電流変調は、 ひずみによる低電界移動度の変化と飽和速度すなわち高電界 輸送の変化の両方によって決定されることを明らかにした。 (110) 面CMOSFETの (100) 面CMOSFETに対する性能の 優位性は大きなひずみのもとでも保たれるため、ひずみ (110) 面CMOSFET技術は次世代以降の高性能・低消費電力LSI の実現に向けて非常に有望であると考えられる。

この研究の一部は、独立行政法人新エネルギー・産業技術総合開発機構(NEDO)から受託したプロジェクト「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」で実施したものである。

#### 文 献

- (1) 齋藤真澄, ほか、p型MOSFETの高速化技術。東芝レビュー。63, 9, 2008, p.54 - 57.

- (2) Saitoh, M., et al. "Understanding of Strain Effects on High-Field Carrier Velocity in (100) and (110) CMOSFETs under Quasi-Ballistic Transport". Tech. Dig. IEDM. Washington D.C., 2009-12, IEEE. p.469 - 472.

- (3) Uchida, K., et al. "Carrier Transport in (110) nMOSFETs: Subband Structures, Non-Parabolicity, Mobility Characteristics, and Uniaxial Stress Engineering". Tech. Dig. IEDM. San Francisco, 2006-12, IEEE. p.711-713.

- (4) Saitoh, M., et al. "Physical Understanding of Fundamental Properties of Si (110) pMOSFETs - Inversion-Layer Capacitance, Mobility Universality, and Uniaxial Stress Effects -". Tech. Dig. IEDM. Washington D.C., 2007-12, IEEE. p.1019 - 1022.

#### 齋藤 真澄 SAITOH Masumi, Ph.D.

研究開発センター LSI 基盤技術ラボラトリー研究主務,工博。 ナノ電子デバイス中のキャリア輸送に関する研究・開発に従事。 IEEE,応用物理学会会員。

Advanced LSI Technology Lab.

**沼田 敏典 NUMATA Toshinori, Ph.D.** 研究開発センター LSI 基盤技術ラボラトリー研究主務, 工博。 ナノスケール MOSFET に関する研究・開発に従事。 IEEE, 応用物理学会会員。

Advanced LSI Technology Lab.