# ディスクリート半導体の進化を支える パッケージング技術

Packaging Technologies Supporting Progress of Discrete Semiconductors

# 大谷 忠夫

OTANI Tadao

東芝は、ディスクリート半導体事業として、汎用ロジック、小信号デバイス、パワーデバイス、及びオプトデバイスの四つの製品分野を手がけており、これらの製品は世界市場でも高く評価され、シェアNo.1<sup>(注1)</sup>を堅持している。しかし、市場での競争は激化し、このシェアを維持かつ拡大していくには、常に市場のニーズに基づいた製品化が必要である。

当社は、市場ニーズに応えるための組立て生産技術の開発に取り組んでいる。例えば、小信号デバイスでは小型・薄型化に加え低抵抗化への要求が、パワーデバイスでは大電流・高放熱化への要求が増大しており、それに応じたパッケージング技術を開発してきた。また、これらの製品を生産するための組立て製造設備も同時に開発しており、当社の各製造拠点で稼働している。

Toshiba has been developing discrete semiconductor products in four categories: standard logic devices, small signal devices, power devices, and optoelectronic devices. These devices are highly regarded in the global market, and we are continuing our efforts to supply products corresponding with the market in order to maintain and expand our worldwide top sales in this highly competitive environment.

In response to the needs of the market, we have been focusing on improving assembly and production technologies. For example, we have developed packaging technologies to achieve miniaturization, reduction of thickness, and low resistance for small signal devices, and to achieve a large current and high heat radiation for power devices. We have also developed the manufacturing and assembly equipment operating in our manufacturing bases to produce these products.

### 1 まえがき

車載製品や携帯情報端末,パソコン(PC),デジタル家電など,応用製品の進化に伴い,ディスクリート半導体への市場のニーズも多様化している。東芝はこれらのニーズに対応した新しいパッケージの開発に取り組んでいる。例えば小信号デバイスの分野では,携帯情報端末の進化とともに小型・薄型化へのニーズが増し,それに対応する小型パッケージング技術が重要になっている。またパワーデバイスでは,大電流や高放熱への要求から低抵抗接合技術を,オプトデバイスでは,高輝度化要求に対応した材料技術を中心に開発を進めている。更に,これらのキー技術を適用した製品を生産するための製造設備も同時に開発しており,当社の各製造拠点でこれらの設備が稼働している。

一方,半導体市場での激しい競争のなか,製品のコスト競争力強化は必須である。製品コストを低減するためには,設備の生産性向上に必要な技術も重要な開発要素となる。

ここでは、ディスクリート半導体に要求される諸特性を実現 するためのパッケージング技術及び装置技術について述べる。

# 2 小信号デバイスのパッケージング技術

携帯電話やデジタルカメラなどの携帯情報端末の進化に伴っ

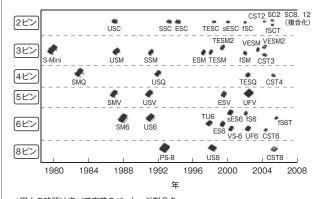

\*図中の略語はすべて東芝のパッケージ製品名

図1. 小信号バッケージの進化のようす — 携帯情報端末の進化に合わせて、パッケージも小型・薄型化へと進化してきた。

Road map of packages for small signal devices

て、小信号デバイスの小型・薄型化の要求が高まり、当社はそれに合わせた開発を進めてきた。近年新たに、低消費電力に対応した製品要求が増加しており、パワーデバイスで培ってきた低抵抗接続技術を展開した製品を開発して市場投入している。

### 2.1 東芝の小信号パッケージ

当社の小信号パッケージの進化のようすを図1に示す。携

(注1) 2009年ガートナー社調べ。

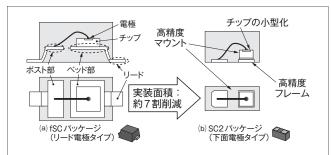

図2. fSCとSC2のパッケージ構造比較 — SC2は、チップをマウントするベッド部及びポスト部の裏面をそのまま電極とするリードレス構造で、fSCに比べ小型化となっている。

Comparison of structures of fSC and SC2 packages

帯電話やデジタルカメラなど製品の小型化に伴い、ガルウィングタイプのパッケージからフラットリードタイプへ、更に下面電極タイプへと、小型・薄型パッケージの開発を推進してきた。例えば、2ピンリードタイプの製品として1.0×0.6 mmサイズのパッケージfSCを製品化し、多くの携帯電話メーカーやモジュールメーカーに採用されているが、更に小型化を狙った0.6×0.3 mmタイプのパッケージSC2も同様に採用実績を積んでいる。

#### 2.2 SC2の特長

SC2は、これまでのリード電極タイプのパッケージとは異なり、部品下面に外部電極を設けている。fSCとSC2の構造比較を図2に示す。fSCは、チップを搭載するベッド部と、チップ上面の電極からの配線(ワイヤボンディング)が接続されるポスト部があり、それぞれから外部電極となるリードが延びている構造である。一方SC2は、チップをマウントするベッド部の裏面、及びポスト部の裏面をそのまま電極とするリードレス構造であり、実装面積の削減に大きく貢献している。

この構造とするために、チップの小型化や高精度フレームの 採用などのデザイン上の工夫と、従来以上の組立て精度が必要となる。このため、新たに高精度に搭載できるマウンタ (チップ搭載装置)を開発して量産を実現している。この装置 は従来に比べ、生産性を落とさずに、搭載精度を30%向上させることができる。

#### 2.3 新規パッケージの概要(1)

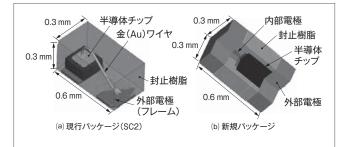

近年では、小型を維持したままで更に実装性の良いパッケージへの要求も強いことから、新たにチップ抵抗やチップコンデンサなどの受動部品と同じ形状のダイオード開発にも着手している。このパッケージは、外部電極を5面電極構造とすることで、実装時にはんだフィレットを形成できることから、実装強度が向上するとともに、実装後の外観検査が容易になるなどの利点がある。SC2と新規開発パッケージとの構造比較を図3に示す。

SC2の組立てプロセスは、従来から用いられているダイマウントやワイヤボンディング、樹脂モールドなど、個片化された

図3. SC2と新構造のパッケージ比較 — 新構造のパッケージは、外部電極を5面電極構造とすることで、SC2に比べて実装性が向上している。

Comparison of structures of SC2 and new package

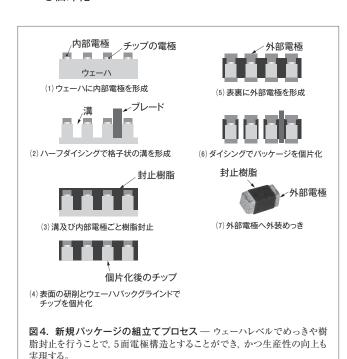

個々の半導体チップに対する組立て方式を採用している。これに対して新規パッケージでは、ウェーハレベルで銅(Cu)めっきや樹脂封止を行い、一括形成するWLP(Wafer Level Process)を適用し、生産性の向上を可能にしている。その組立てプロセスを図4に示し、以下に概要を述べる。

- (1) 素子を形成したウェーハに、Cuめっきで内部電極 (半 導体チップから外部電極への配線部)を形成

- (2) ハーフダイシング<sup>(注2)</sup>によりウェーハ上に格子状の溝を 形成

- (3) 格子状の溝及び内部電極を封止樹脂で封止

- (4) グラインダによる研削で内部電極の頭出しをするととも に、ウェーハバックグラインドでウェーハを薄化してチップ を個片化

(注2), (注3) ダイシングは, シリコン上のウェーハを切断することで, ハーフ ダイシングは, ウェーハの深さ方向の途中まで切込みを入れること。

Processes for assembly of new package

- (5) ウェーハの表裏に、Cuめっきにより外部電極を形成

- (6) ダイシング(注3)によりパッケージを個片化

- (7) 個々のパッケージ外部電極へ外装めっき

このように、Cuめっき工法を適用することで、従来の組立て プロセスにおけるダイマウントやワイヤボンディングなどチップ ごとに組み立てる工程を排除できる。ウェーハを一括で処理 することによる生産性向上も期待でき、量産化に向けた開発 を行っている。

一方、小信号デバイスに対してもパッケージの低抵抗化への 要求が増加していることから、当社はパワーデバイスで培った 低抵抗接続技術を展開し、2010年に製品への適用を開始す る予定である。このパッケージは配線材料としてアルミニウム (AI) リボンを採用することで、従来のワイヤボンディング構造 パッケージに比べてパッケージ内の配線抵抗を十数mΩ低減 することが可能であり、携帯情報端末などに採用される予定 である。ここで用いられるAlリボンはパワーデバイスに用い られているものに比べ、より微小なサイズが必要となること、 またより高い搭載精度が要求されることから、新たにボンディ ング装置を開発し、量産化を図る。

## 3 パワーデバイスのパッケージング技術

パワーデバイスの進化の歴史と将来のようすを図5に示す。 挿入タイプの自立型パッケージから、小型の表面実装タイプ、 あるいはモジュールタイプまで幅広いパッケージング技術が要 求される。最近では自動車の電子化に伴い、大電流に対応し た製品の要求が増加しており. 低抵抗接続技術が不可欠に なっている。一方で、パワーマネジメント機能を持つマルチ チップモジュール (MCM) のような複合パッケージ. 及び携帯

120 A 高放熱構造 45 A 小型化 75 A 大電流 低抵抗接続 タイプ TO-220SM(W) TO-220SM TFP MCM 小・中電流 タイプ SOP-8 SOP-8 SOP-Ad QFN56 OFN40 小型化 TSSOP-Ad TSON-8/Ad CSPタイプへ STP STP2 TSSOP-8 リチウムイオン ベアチップ 電池用途 構造へ チップLGA 2010 2012 2000 2004 2006 2008

CSP: チップサイズパッケージ

図5. パワーデバイスの進化の歴史と将来のようす — 大電流や高放熱へ の要求に応えるため、低抵抗接合技術を中心に進化してきた。

Road map of packages for power devices

電話やノートPCなどに搭載される小型バッテリーの保護回路 として用いられるチップBGA (Ball Grid Array) やチップ LGA (Land Grid Array) への要求も高まっており、これらの パッケージラインアップも拡充していく。

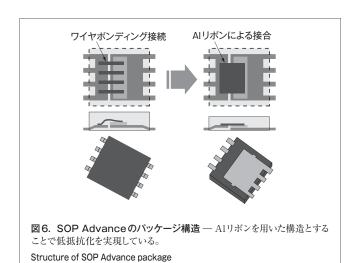

当社は、低抵抗接続技術としてAIリボンやCuの薄板を配 線材料とする接続技術を開発し、様々なパッケージに適用して いる。この接続技術を適用している代表的なパッケージとし てSOP Advanceがあり、従来のワイヤボンディング構造の製 品であるSOP-8に比べ、パッケージ抵抗(チップ抵抗を除く) を約1/3に低減している。

SOP Advanceの内部構造を図6に示す。リボン状のAl板 をチップ電極とリードフレームに接合することでパッケージの 低抵抗化を実現している。また、同じ構造で実装面積をSOP Advanceの約1/3にするという。更なる小型化を実現した TSON Advanceも既に製品化しており、今後の伸張が期待さ れる。

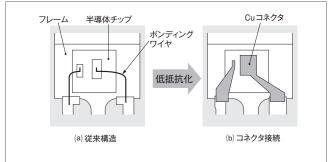

また、コネクタ接続を適用して低抵抗化を実現した例とし て、TO-220SISのパッケージ構造を**図7**に示す。同一ユニッ ト内でチップとコネクタをマウントする設備を開発し、高生産 性も実現している。

図7. TO-220SISのパッケージ構造 — コネクタ接続を適用することで、 低抵抗化を実現している。

Structure of TO-220SIS package

図8. マルチチップマウンタ — 複数個のチップを搭載できる装置で、生産性の向上を実現している。

Multi-chip mounter

更に、複数チップを1アクションで搭載できるマルチチップマウンタの開発も行い、当社のFLAT製品群に適用している。このマルチチップマウンタの外観を図8に示す。ウェーハからチップをピックアップし、リードフレーム上に搭載する装置で、生産性の向上を実現している。

マウントヘッドの小型・軽量化,及びウェーハ上のチップの一括認識アルゴリズムやリードフレーム送り機構などの開発により,従来1チップずつ搭載していたものを複数個同時に搭載でき,業界最速レベルの0.16 s/チップ(プロセス時間を含む)を実現した。また,チップの損傷を低減するために,瞬時に荷重を切り替えることができる独自の荷重制御機構も組み込んでおり,当社の各製造拠点で稼働している。

## 4 オプトデバイスのパッケージング技術

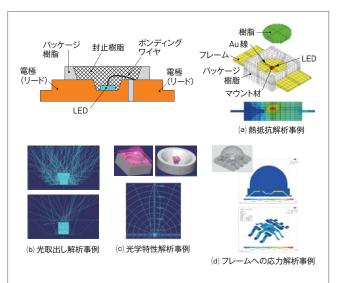

オプトデバイスでは、今後伸張が期待される可視光デバイスについて、高放熱樹脂や低応力透明樹脂などの樹脂材料と、光の取出し効率の向上を目的とした組立て技術を中心に開発している。可視光デバイスの構造とシミュレーション例を図9に示す。光の取出し効率向上のため、パッケージ樹脂の構造や封止樹脂の特性などが光学特性、熱伝導特性、及び応力に与える影響をシミュレーションして、パッケージ設計の適正化を図っている。

# 5 環境配慮型技術

当社は従来から、環境対応技術として外装リードの鉛フリー化対応を進めてきた。今後、環境配慮型の半導体へのニーズがますます高まると予測され、また、欧州を中心としたセットメーカーから臭素 (Br) 及びアンチモン (Sb) を含有しない製品を求める声も強くなっており、これらの物質を意図的に

図9. 可視光デバイスの構造とシミュレーション例 — 光の取出し効率向上のため、光学特性や光取出し解析を実施しパッケージ設計の適正化を行っている。

Optical device and examples of simulation results

添加しない製品の開発を進めてきた。また、Br、Sbに代わる 難燃剤を含むモールド樹脂の採用を進めており、2009年8月 現在で、約62%まで対応を終えている。

一方,組立て技術面では、材料,組立てプロセス,及び工程管理の3項目について取り組んでいる。Br、Sbを含まない新たな難燃剤を含む樹脂の開発と、モールド工程でのプロセス条件の適正化が必要となり、各拠点での対応を進めている。

#### 6 あとがき

ここでは、当社におけるディスクリート半導体のパッケージング技術及び組立て装置への取組みについて、小信号デバイスとパワーデバイスを中心に述べた。

車載機器や小型情報端末など、応用製品の新たな進化に伴い、そこで用いられる部品も進化し続ける必要がある。当社は、今後も市場のニーズに基づき、アプリケーションの差異化に貢献できるパッケージ開発を推進していく。

#### 文 献

(1) 東條 啓, ほか. "ウェハレベルプロセスによる新規小型パッケージの開発". エレクトロニクス実装学会秋季大会 第19回マイクロエレクトロニクスシンポジウム論文集. 福岡, 2009-09, エレクトロニクス実装学会. 2009, p.97 - 100.

大谷 忠夫 OTANI Tadao

セミコンダクター社 姫路半導体工場 組立生産技術部長。 ディスクリート半導体の組立生産技術の開発に従事。溶接学 会会員。

Himeji Operations-Semiconductor