集

# 電源回路向け 高耐圧パワー MOSFET π MOS- VI及び DTMOS- IIシリーズ

πMOS-VII and DTMOS-II Series High-Voltage Power MOSFETs for Power Supply Circuits

# 齋藤 涉

SAITO Wataru

高耐圧パワー MOSFET(金属酸化物半導体型電界効果トランジスタ)は、家電やパソコンなど様々な電化製品の電源回路に用いられている。省エネ化のために、パワー MOSFETのオン抵抗の低減が主に求められてきたが、最近、定格電圧(耐圧系)の選択肢の拡大や内蔵ダイオードの高速化なども要求されてきた。

東芝は、このような要求に応えるために、 $\pi$  MOS- $\Psi$ IとDTMOS- $\Psi$ Iシリーズを開発した。 $\pi$  MOS- $\Psi$ IシリーズではMOS ゲートセルを微細化し、DTMOS- $\Psi$ Iシリーズではドリフト層にスーパージャンクション構造を採用してオン抵抗を低減した。定格電圧として新規の650 V系をラインアップし、また $\pi$  MOS- $\Psi$ Iシリーズではダイオードの逆回復時間を半減させた製品も開発した。

The characteristics of high-voltage power metal-oxide-semiconductor field-effect transistors (MOSFETs) for power supply circuits in electrical appliances such as home electronics and PCs need to be continuously improved due to the requirements for strengthening of new voltage-class lineups and speeding up of body diodes in addition to reduction of on-resistance.

To meet these requirements, Toshiba has developed two new high-voltage power MOSFETs: the  $\pi$ MOS-VII series with a fine cell-pitch, and the DTMOS-II series with a super junction (SJ) structure in the drift layer. The new voltage class of 650 V has been added to the voltage-class lineup of these series. In addition, we have newly developed a high-speed body diode whose recovery time is reduced to half that of the previous type.

#### 1 まえがき

地球温暖化やエネルギー問題によって、電化製品での省エネ化の要求は増え続けており、電気エネルギーを有効に活用するエコ製品がこれまで以上に必要とされてきている。このため、電化製品内の電源回路の効率を向上させることが不可欠になり、コンセントに近い電源回路の一次側で使われている高耐圧パワー MOSFET の性能のいっそうの向上が求められている。

耐圧が500 V系や600 V系のパワー MOSFETでは、これまで主な要求はオン抵抗の低減であったが、最近、耐圧の選択肢の拡大や内蔵ダイオードの高速化なども要求されてきた。

東芝は、このような要求に応えるために、π MOS-Ψと DTMOS-Ⅱシリーズを開発した。ここでは、これらの高耐圧 パワー MOSFET の概要と特長について述べる。

## 高耐圧パワー MOSFETの構造と オン抵抗の低減

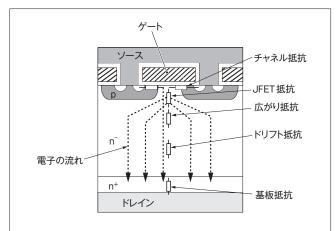

高耐圧パワー MOSFET は、通常、プレーナ型 MOS ゲートを持つ縦型素子である( $\mathbf{Z}$ 1)。ゲート電圧を印加することで MOS 界面に反転チャネルが形成され、電子がソース電極からチャネル、 $\mathbf{p}$  ( $\mathbf{p}$ 型半導体) ベース間のJFET (Junction FET)

図1. 高耐圧パワー MOSFETの断面構造 — パワー MOSFET がオン状態での電流経路に発生する各部の抵抗の総和がオン抵抗になる。

Cross-sectional structure of high-voltage power MOSFET

領域を通ってドリフト層全体に広がり、ドレイン電極に流れ込む。これが素子のオン状態における電流経路であり、オン抵抗とは、この電流経路で発生する各部の抵抗の総和である。

高耐圧パワー MOSFETでは、pベース下の広がり抵抗とドリフト抵抗がオン抵抗の80%以上を占めている。これらの抵抗はドリフト層の不純物濃度に依存し、ドリフト層濃度はオフ状態の耐圧を決める重要な設計パラメータの一つでもある。耐圧を上げるために、ドリフト層を低濃度なn(n型半導体)層

で形成することで空乏層を伸ばし、電圧を保持する。そのため、高耐圧な素子ほどドリフト層濃度が低くなって、ドリフト抵抗が増加し、オン抵抗は高くなる。これがオン抵抗ー耐圧トレードオフ(二律背反)と呼ばれ、理論上のドリフト層の濃度と厚さを最適化した最小オン抵抗がシリコン(Si)限界と呼ばれる。

縦型パワー MOSFET はpベースやMOSゲートの凹凸により電界集中が発生するため、理想状態よりも耐圧が低下してしまう。このため、必要な耐圧を得るためにドリフト濃度を下げるので、ドリフト抵抗や広がり抵抗が増加してしまう。

$\pi$  MOS- $\Psi$ シリーズでは、pベース端での電界集中を抑制し、高耐圧が得られやすくすることでドリフト抵抗を低減するために、MOSゲートの平面パターンを従来製品の $\pi$  MOS- $\Psi$ シリーズのメッシュパターンからストライプパターンに変更し、更に、広がり抵抗を低減するために $\Phi$ で一ス幅を短縮した。これらの変更で $\pi$  MOS- $\Psi$ シリーズよりもオン抵抗を12%低減できた。

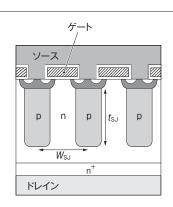

また、DTMOSシリーズでは、ドリフト層にスーパージャンクション (SJ) 構造と呼ばれる周期的なp/n構造を形成することで、従来の縦型パワー MOSFETでは得られなかったSi限界を下回る超低オン抵抗を実現できる( $\mathbf{Z}$ 2)。

従来の素子では、オフ状態においてpベース底部から低濃度 n層 (ドリフト層) 中を縦方向に空乏層が伸びていたのに対して、SJ構造は縦方向に伸びるp/n接合から横方向へ空乏層が伸びる。SJ構造の周期  $W_{SJ}$ が狭いほど空乏化しやすく、電流経路であるn層の濃度を上げても高耐圧が得られる。これにより、Si 限界を下回る超低オン抵抗を実現できる。

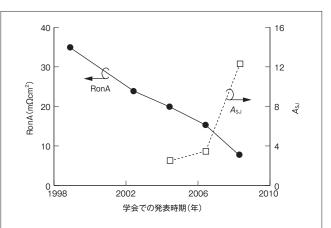

SJ-MOSFETは、1998年に発表されて以来、各社活発に開発が行われており、SJ構造の横方向微細化によりアスペクト比 $A_{SJ}$  (=厚さ $t_{SJ}$  /周期 $W_{SJ}$ )を大きくすることで単位面積当たりのオン抵抗 (RonA) の低減が進んでいる (図3)  $^{(1)-(5)}$ 。当

図2. SJ-MOSFET断面構造 — SJ構造の $W_{SJ}$ が狭いほど空乏化しやすく、電流経路のn層の濃度を上げても高耐圧が得られ、Si限界以下の非常に小さいオン抵抗を実現できる。

Cross-sectional structure of SJ-MOSFET

図3. 学会発表における  $600 \, \text{V}$ 系 SJ-MOSFET  $\sigma$  Ron A 推移 - SJ 構造の横方向の微細化で $A_{\text{SJ}}$ を大きくし、Ron A の低減を進めてきた。 Reductions in on-resistance(RonA) of  $600 \, \text{V-class}$  SJ-MOSFETs reported at technical meetings

社でも、SJ構造を採用したDTMOSを2007年に製品化し、第2世代のDTMOS-IIシリーズでは、 $\pi$  MOS-VIシリーズの 1/4のオン抵抗を実現している。

## 3 定格電圧のラインアップ拡充

パワーMOSFETの定格電圧(耐圧系)の選び方は、パワーMOSFETに印加されるオフ時の電圧だけで選ぶのではなく、スイッチング時の電圧サージを考慮し、余裕を持たせた耐圧系を選択する。しかし、2章で述べたように高耐圧な素子ほどオン抵抗は大きくなってしまい、オン状態での損失(導通損失)が増えて効率を悪化させるので、耐圧に余裕を持たせ過ぎることは得策ではない。

従来製品では、500 V系の上は600 V系と定格電圧の選択肢が少なく、用途に最適な定格電圧の素子のラインアップが不十分であった。そこで、 $\pi$  MOS-Wシリーズでは、回路設計者が必要に応じた定格電圧の素子を選択できるように、450 V系から650 V系まで50 Vごと (一部は25Vごと)に定格電圧ラインアップをそろえ、かつ、定格電流の品種数も増やした(**表1**)。特に、650 V系は、600 V系の製品に少し不満がある設計者を考慮した新しいラインアップである。

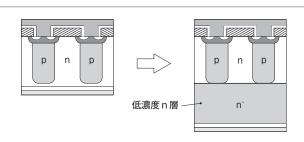

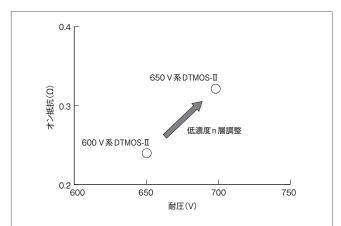

DTMOS-IIシリーズでも同様な要求に応えるため、650 V系を開発した。SJ構造を高耐圧化しようとすると、複雑な構造であるため大幅な設計変更を要する。しかし、当社ではSJ構造の下に低濃度 n層を設ける SemiSJ 構造を採用することで、少ない設計変更により高耐圧ラインアップの展開を実現した。

通常、SJ-MOSFETを高耐圧化させるには、SJ構造の2次元的なスケーリング(サイズの変更)を行う。具体的にはSJ構造を厚くするだけでなく、横方向周期を広くして低濃度化する。このようにSJ構造の高耐圧化には大幅な設計変更を伴う。こ

#### 表 1. π MOS- WIシリーズのラインアップ

Lineup of  $\pi$ MOS-VII series

| 定格電圧 (V) | 定格電流(オン抵抗)                    | 定格品種数 |

|----------|-------------------------------|-------|

| 450      | 3.5 A (1.75 Ω) -19 A (0.25 Ω) | 13    |

| 500      | 3 A (3 Ω) -20 A (0.27 Ω)      | 19    |

| 525      | 3 A (1.7 Ω) –12 A (0.58 Ω)    | 7     |

| 550      | 2.5 A (3.5 Ω) -19 A (0.33 Ω)  | 19    |

| 600      | 2 A (4.3 Ω) -15 A (0.37 Ω)    | 17    |

| 650      | 2 A (3.3 Ω) –12 A (0.5 Ω)     | 12    |

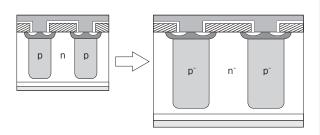

(a) 低濃度 n層の追加及び調整による高耐圧化(SemiSJ構造)

(b) 二次元的なサイズの変更による高耐圧化(SJ構造)

図4. SemiSJ構造とSJ構造の高耐圧設計の違い — SemiSJ構造では 低濃度n層の調整により高耐圧化できるが、SJ構造では大幅な設計変更が 必要となる。

Differences in high-voltage design of SemiSJ and SJ structures

図5. SemiSJ構造での高耐圧化 — 低濃度 n層の調整によって、オン抵 抗値を抑制しながら, 600 V 系 DTMOS- II (型番 TK15A60U) の高耐圧タ イプになる650 V 系 DTMOS-Ⅱ (型番 TK13A65U) を開発した。

Trade-off between on-resistance and breakdown voltage for enhancement of breakdown voltage using SemiSJ structures

れに対して、SemiSJ構造を採用することで、SJ構造下の低濃 度n層を調整するだけで高耐圧化できる(図4)<sup>(6)</sup>。

SemiSI構造で、低濃度n層を調整したときのオン抵抗と耐 圧の関係を図5に示す。単純な設計変更にもかかわらず、SI 構造の厚さやピッチを変更した場合と同等のオン抵抗が実現 できている。

# 内蔵ダイオードの高速化

エアコンや液晶テレビでは、モータやバックライトへの電力 を調整する電源回路としてインバータ回路が用いられ、スイッ チング素子に並列接続された還流ダイオードが必要である。 通常、還流ダイオードに逆回復 (リカバリ) 動作が高速な pin (注1) ダイオードを用いて、パワー MOSFET の内蔵ダイオードを動 作させないように逆直列にダイオードを接続する。しかし、パ ワー MOSFETの内蔵ダイオードを高速化し、還流ダイオード として用いれば、外付けpinダイオード二つが不要となって回 路の部品点数を削減できる。

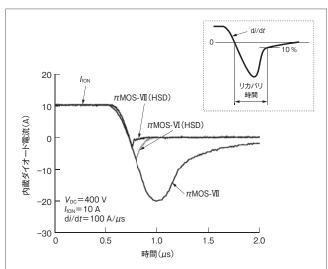

ダイオードのリカバリ時間は, 順方向に電圧が印加された オン状態で、ドリフト層内に蓄積されたキャリアを逆方向に 電圧を印加してオフ状態となるように排出する時間である。 π MOS-Wシリーズでは、キャリア排出を高速化するようにド リフト層の濃度分布を最適化し、更に、再結合によるキャリア 消滅を促進するようにライフタイムも最適化した。

V<sub>DC</sub> : 直流電源電圧

V<sub>ICN</sub> : ダイオード順方向電流 di/dt:ダイオードの単位時間当たりの電流変化量

図6. 高速内蔵ダイオードのリカバリ時間 ― ドリフト層濃度分布とライ フタイムの最適化によって、開発した π MOS-WI (HSD) シリーズ (型番 TK10A60D5) での高速ダイオードのリカバリ時間は, π MOS-VI (HSD) シリーズ (型番 2SK4015) の半分以下に短縮できた。

Recovery current waveform of high-speed body diode in  $\pi$  MOS-VII series

(注1) PN接合の間に真正半導体層 (I層) を持つ構造のダイオード。

開発した $\pi$  MOS- $\Psi$ シリーズの高速ダイオード (HSD) のリカバリ時間は約50 ns と $\pi$  MOS- $\Psi$  (HSD) の半分以下に短縮できている (図6)。これにより、低いリカバリ損失を実現できるだけでなく、 $\pi$  MOS- $\Psi$  (HSD)シリーズなどでは対応できなかった高いスイッチング周波数での回路にも使用できる。

#### 5 あとがき

省エネ電化製品の電源回路の効率を改善できる高耐圧パワー MOSFET  $\pi$  MOS-WEDTMOS-IIシリーズを開発した。従来製品に比べてオン抵抗を低減するだけでなく、新しい定格電圧650 V系をラインアップし、電源回路設計者の様々な要求に応えている。更に、内蔵ダイオードのリカバリ時間も従来製品に比べて半分以下に短縮できた。

当社は今後も、電化製品の省エネ化によりいっそう貢献できる魅力ある高耐圧パワー MOSFET を開発していく。

### 文 献

- Deboy, G., et al. "A new generation of high voltage MOSFETs breaks the limit line of silicon". Technical Digest in International Electron Device Meeting 1998. San Francisco, USA, 1998-12, IEEE. 1998, p.683 - 685.

- (2) Onishi, Y., et al. "24mΩcm² 680V Silicon Superjunction MOSFET". Proc. of International Symposium on Power Semiconductor Devices & IC's 2002. Santa Fe, USA, 2002-06, IEEE. 2002, p.241 - 244.

- (3) Saito, W., et al. "A 20m Ωcm² 600 V-class Superjunction MOSFET". Proc. of International Symposium on Power Semiconductor Devices & IC's 2004. Kitakyushu, Japan, 2004-05, IEEJ. 2004, p.459 - 462.

- (4) Saito, W., et al. "A 15.5mΩcm²-680 V-class Superjunction MOSFET Reduced On-Resistance by Lateral Pitch Narrowing". Proc. of International Symposium on Power Semiconductor Devices & IC's 2006. Naples, Italy, 2006-06, IEEE. 2006, p.293 - 296.

- (5) Sakakibara, J., et al. "600V-class Super Junction MOSFET with High Aspect Ratio P/N Columns Structure". Proc. of International Symposium on Power Semiconductor Devices & IC's 2008. Orland, USA, 2008-05, IEEE. 2008, p.299 - 302.

- (6) Saito, W., et al. High Breakdown Voltage (>1000V) Semi-Superjunction MOSFETs Using 600-V Class Superjunction MOSFET Process. IEEE Trans. Electron Devices. 52, 10, 2005, p.2317 - 2322.

齋藤 涉 SAITO Wataru, D.Eng.

セミコンダクター社 ディスクリート半導体事業部 先端ディスク リート素子開発部参事, 工博。次世代パワーデバイスの開発に 従事。IEEE, 応用物理学会, 電子情報通信学会会員。 Discrete Semiconductor Div.