Low-Voltage Power MOSFETs Achieving High Performance and Low Cost

横田 誠 川口 雄介

■ YOKOTA Makoto

■ KAWAGUCHI Yusuke

パワー MOSFET (金属酸化膜半導体型電界効果トランジスタ) は、大電力を扱うパワー半導体分野において中心的な存在であり、その性能は、機器のエネルギー効率や消費電力などへ直接影響し、省エネ及び二酸化炭素(CO2)削減など環境に配慮するうえでも重要なデバイスである。特にモバイル機器に使用される低耐圧パワー MOSFET に対しては、バッテリーでの長時間駆動を実現させるための低損失化に加え、機器の小型・薄型・軽量化に伴うパッケージサイズの縮小や、電力を供給する CPUの多機能・高性能化に伴う大電力対応、更には機器の価格下落に伴う低価格化に向けた要求が強まっている。

東芝は、トレンチ構造型低耐圧パワー MOSFETにおける二律背反の特性改善と低価格化を両立させ、多様化するこれらの要求に応えるとともに、省電力化を通じて環境に与える影響を低減している。

Power metal-oxide-semiconductor field-effect transistors (MOSFETs), which are key devices in the power semiconductor field, are playing an important role in enhancing energy conservation and reducing carbon dioxide (CO<sub>2</sub>) emissions because these devices directly affect the energy efficiency and power consumption of equipment. In particular, low-voltage power MOSFETs mounted on mobile equipment are increasingly required to have low power loss for longer battery life; a compact package to achieve smaller, low-profile, and lighter weight equipment; higher power supply required by advanced central processing units (CPUs); and lower cost.

To meet these requirements, Toshiba has developed a new trench technology improving the trade-off between high performance and low cost, and realized more ecologically friendly devices through power conservation.

# 1 まえがき

ノートPC (パソコン)では、CPUやメモリに電力を供給する同期整流方式DC/DCコンバータ (直流電源変換器)や、各電源ラインのスイッチに低耐圧パワー MOSFETが多数 (一般的な機種で約25個)搭載されており、電源の電力変換効率の向上や小型・薄型化など機器のパフォーマンスに直結する重要な役割を担っている。また、搭載される素子数が多いため、機器のコストダウンに向けたパワー MOSFETの低価格化が近年ますます重要になってきている。パワー MOSFETの使用例として東芝 dynabook<sub>TM</sub> SS RX2のメイン基板を**図1**に示す。

パワー MOSFETでもっとも重要視される特性はオン状態の導通抵抗(以下、オン抵抗と呼ぶ)であるが、同一プロセスのパワー MOSFETで比較した場合、チップサイズが大きいほど製品価格は高いため、低価格化を考慮する場合、やみくもに低オン抵抗製品を選択することは不適切である。また、パワー MOSFETの高周波動作のためには、ゲート容量の低減が重要であるが、オン抵抗が低いほどゲート容量は大きくなり、このトレードオフの改善が低損失と低価格を実現するパワー MOSFETの開発の重要なポイントとなる。ここでは、主に技術的な課題の改善について概要を述べる。

**図 1. dynabook**<sub>TM</sub> **SS RX2 メイン基板** — ノートPCにはパワー MOSFET が多数搭載されている。

Main printed circuit board of dynabook  $_{\text{TM}}$  SS RX2

# 2 パワー MOSFETの電力損失

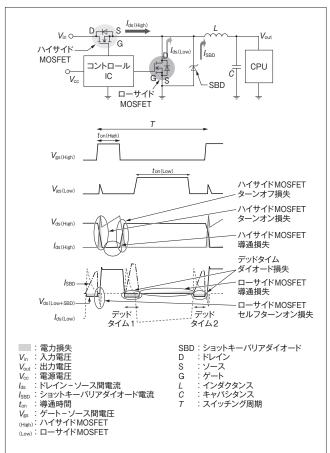

電源ラインのスイッチに使用されるパワー MOSFETにおける電力損失では、素子のオン抵抗に起因する導通損失が大部分を占めるが、高速スイッチング動作を伴う用途では、電力損失は多岐にわたる。例として、同期整流方式降圧型DC/DCコンバータにおける動作の概要と電力損失の内容を図2に示す。

図2. 同期整流方式DC/DCコンバータの動作と電力損失 — パワーMOSFET の高速スイッチング用途においては、導通損失だけでなくスイッチング損失などの電力損失が存在する。

Power losses of synchronous DC/DC converter

導通期間の短いハイサイド MOSFET ではスイッチング損失 (ターンオン損失及びターンオフ損失) が、導通期間の長いローサイド MOSFET では導通損失が、それぞれ支配的であることがわかる。

また、これらの主な電力損失のほか、ローサイド MOSFET では、デッドタイム期間中の内蔵ダイオード導通損失及びセルフターンオン損失も無視できない要素である。

# 3 電力損失の改善

オン抵抗と高速スイッチング特性のトレードオフの改善について述べる。

## 3.1 オン抵抗の低減

パワー MOSFETのオン抵抗の低減は、動作損失を下げるためのもっとも重要な開発課題である。おおむね100 V以下の低耐圧タイプでは、トレンチゲート構造が積極的に採用されて半導体チップ表面近傍部の抵抗が大幅に削減され、更に微細加工技術のデザイン世代ごとに低オン抵抗化が進み、この5~6年で単位面積当たりのオン抵抗が50 %以下に低減され

ている。

また、単位面積当たりのオン抵抗の低減は、より小さなチップサイズで同一オン抵抗値を実現できるため、チップサイズの縮小化による低価格化の効果も大きい。

### 3.2 ゲート容量の低減

パワーMOSFETをターンオン/オフさせるためには、ゲート 容量成分を充放電させる必要があり、高速スイッチング動作、及びドライブ電力の削減には、その容量成分の低減が重要である。

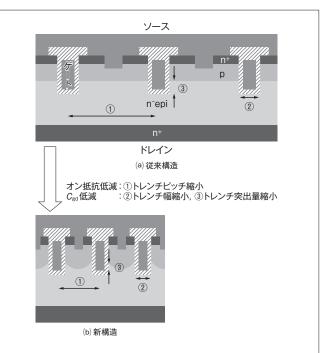

1章で述べたように、オン抵抗とゲート容量の間にはトレードオフの関係がある。低オン抵抗化を実現するためにトレンチゲートピッチの縮小など微細加工を行うと、ゲート容量の増加につながり、この結果スイッチング特性が悪化する。このため、トレンチ幅の縮小やトレンチ突出し量の縮小によってトレンチ構造を最適化することで、ゲート容量の増加を軽減している。パワー MOSFETの従来構造と新構造の比較を図3に示す。

特に前述の同期整流方式DC/DCコンバータに使用されるパワー MOSFETでは、低オン抵抗特性だけでなく高速スイッチング特性も強く要求されるため、このトレードオフの改善が不可欠である。

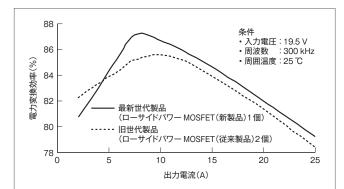

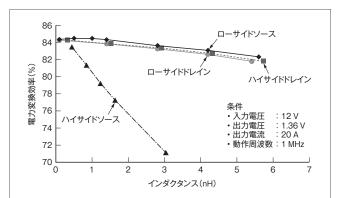

パワー MOSFET の特性改善の結果、DC/DCコンバータの電力変換効率の向上が実現される。例として、電力変換効率の比較データを図4に示す。旧世代の製品に対して、最新世代の製品ではローサイドパワー MOSFET の数を削減しつ

図3. パワー MOSFETの従来構造と新構造の比較 — 新構造はオン抵抗とゲート容量の両方を低減する。

Comparison of trench gate structure of conventional and newly developed power MOSFETs

特

図4. DC/DCコンバータの電力変換効率の比較 — 最新世代パワー MOSFET は二律背反の素子数削減と電力変換効率向上を両立している。

Comparison of power conversion efficiency of conventional and newly developed synchronous DC/DC converters

つ電力変換効率が約1%(25A出力時)向上しており、二律背 反の特性改善とコストダウンを両立している。

# 4 安全性の向上

## 4.1 セルフターンオン (Shoot-Through) 現象の抑止

パワー MOSFET の高速スイッチング動作では、ドレイン電 流とドレイン-ソース間電圧は大きく変化するので、電流変化 率 di/dtと電圧変化率 dv/dt はいずれも高い値となる。これが ドレイン-ゲート間容量 $C_{gd}$ に帰還され、ゲート電圧が上昇し、 パワー MOSFET が誤ってターンオンする可能性がある。こ れはセルフターンオン若しくはShoot-Throughと呼ばれる誤動 作で、電力変換効率を悪化させるだけでなく、場合によっては 発煙や発火など深刻な問題を引き起こす現象である。

この現象を防止するために、パワー MOSFET ではゲート電 位を上昇させる変位電流の抑止を目的とした Cod の低減、及び ゲート容量を放電するための内部ゲート抵抗の低減がそれぞ れ重要であり、最適なチップデザインでこれを実現している。

# 4.2 アバランシェ破壊耐量の向上

パワー MOSFET を高速スイッチングさせるとき,回路自体 のインダクタンス及び寄生インダクタンスにより、ドレイン-ソー ス間電圧の最大定格値を超える逆電圧が発生する。このと き、内部構造的に存在する寄生バイポーラトランジスタが動作 し、一部のセルに電流が集中してパワー MOSFET が破壊す る場合がある。これがアバランシェ破壊である。

近年のパワー MOSFET ではアバランシェ破壊に対する耐 量が最大定格値として保証されている。アバランシェ破壊耐 量の向上には、 寄生バイポーラトランジスタを動作させずに、 MOSFETセルに均等にアバランシェ電流を流すことが重要で あり、アバランシェ電流がチャネル近傍を流れないようセル構 造を最適化することで、アバランシェ破壊耐量の向上を実現し ている。

# 5 パッケージの改善

電子機器の高機能・多機能化が進み、それに使用されるパ ワー MOSFETも大電力への対応が求められる。その一方 で、電子機器の小型・薄型化に伴い、高密度実装への対応や 低背化への要求が高まり、大電力を扱うパワー MOSFETに とっての放熱条件はますます厳しくなっている。この課題を解 決するため、小型の表面実装パッケージの裏面に放熱フィンを 設置し、実装基板面から放熱させることによって許容損失を 増加させたパッケージ(図5)が主流になりつつあり、当社もこ の方式を採用している。

パワーMOSFETには温度によって変化する特性があり、こ のような高放熱パッケージでチャネル温度を低く抑えること は、長期信頼性の維持だけでなく、素子特性を適正なレベル にコントロールするという意味でも非常に有効である。

また低オン抵抗化の進行とともに、パッケージ外部端子と チップ間の接続方法も見直され、従来の細い金属線(ボンディ ングワイヤ) に代わり、金属板 (ストラップ) 又はリボンによる 接続が一般に使用されている。この接続方法により、小型面 実装パッケージの場合、 $1\sim 2$  m  $\Omega$ 程度のオン抵抗が低減でき

図5. 東芝 "SOP Advance" パッケージ — 放熱効果が高く, 許容損失 が高いパッケージである。

Toshiba SOP Advance package

図6. ハイサイドパワー MOSFETのソースインダクタンスの電力変換効 率への影響 - 同期整流方式DC/DCコンバータの電力変換効率に関する シミュレーション結果から、ソースインダクタンスの低減が電力変換効率の 向上には重要であることがわかる。

Effect of source inductance of high-side MOSFET on power conversion efficiency

る。更に、ソースインダクタンスも低減されるため、高周波動作時の電圧降下が抑制されて、電力損失も改善される。同期整流方式DC/DCコンバータにおける寄生インダクタンスの電力変換効率への影響を図6に示す。

# 6 高付加価値機能の追加

## 6.1 外付けショットキーバリアダイオードの問題点

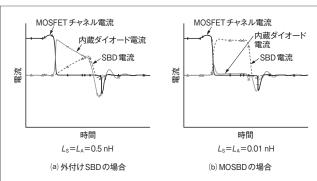

同期整流方式のDC/DCコンバータでは、ハイサイドとロー サイドのパワー MOSFET が同時にオンすることによって発生 する貫通を防止するためにデッドタイム期間が設けられており. この期間中、転流電流はローサイドMOSFETの内蔵ダイオー ドを流れる。内蔵ダイオードでの導通損失を低減するため、 ローサイドMOSFETと並列に順電圧の低いショットキーバリ アダイオード (SBD) を外付けする場合がある。ただし、実際 には外付けSBDのアノード電極とローサイドMOSFETのソー ス電極の間の回路配線上には寄生インダクタンスが存在する ため、転流電流はSBDに流入するのを阻害される。このため 順電圧特性の悪いMOSFET内部の内蔵ダイオードに転流電 流が残留することが、シミュレーションによる検証で確認され ている (図7(a))。この場合、発生する順電圧降下はSBDより 内蔵ダイオードのほうが大きいため、デッドタイム期間中の導通 損失の悪化につながる。また、内蔵ダイオードはリカバリ特性 の面でもSBDに比べて劣るため、リカバリ損失の増大にもつ ながる。

DC/DCコンバータの高周波化に伴い、デッドタイム期間中のパワー MOSFETの内蔵ダイオード若しくは外付けSBDの導通損失及びリカバリ損失の影響が大きくなってきており、重要な改善課題の一つである。この損失を低減するためには、前述の回路配線上の寄生インダクタンスの低減が必要である

L<sub>S</sub>: ソース寄生インダクタンス L<sub>A</sub>: アノード寄生インダクタンス

図7. SBD内蔵パワー MOSFET (MOSBD) の効果 (回路シュミレーション 波形) — SBD内蔵パワー MOSFETは、DC/DCコンバータ用途において デッドタイム損失及びリカバリ損失を改善し、かつ高周波ノイズの低減に効果が大きいことがわかる。

Effect of built-in Schottky barrier diode (SBD) of power MOSFET

が、ディスクリート製品による回路構成では物理的な制約も大きく、効果が限定的である。

#### 6.2 SBD内蔵パワー MOSFET (MOSBD)

これらの課題を改善するため、配線の寄生インダクタンスの影響を受けにくいMOSBDが開発されている。この製品は、パワー MOSFETセルの一部がSBD領域に割り当てられ、パワー MOSFETとSBDがモノリシック構造となっている複合製品であり、パワー MOSFETとSBDの間の寄生インダクタンスは無視できるほど小さい。この製品をローサイド用スイッチとして使用することにより、デッドタイム損失が軽減され、特に軽負荷時の効率改善に効果が大きい(図7(b))。

また、このMOSBDはDC/DCコンバータで発生する高周波ノイズの削減にも効果が大きい。これは、パワー MOSFET内蔵ダイオードに比べて高速なリカバリ特性を持つSBDを内蔵しているため、パワー MOSFETのスイッチング時のスパイク・リンギング電流が抑制されて電流変化率  $\mathrm{d}i/\mathrm{d}t$  が減少し、寄生インダクタンス L によって発生するスパイク・リンギング電圧  $L \times \mathrm{d}i/\mathrm{d}t$  が減少するからである。

## 7 環境負荷への対応

有害物質を排除するため、外部端子に使用されるはんだの 無鉛化と、パッケージ材料の見直しによるハロゲン系有害物 質の削除を実現している。

また、製造プロセスでの生産効率を向上させ、製品生産段階で排出される $CO_2$ を大幅に低減している。

## 8 あとがき

ここでは、当社の低耐圧パワー MOSFETの開発について 例を交えて述べた。今後更にパワー MOSFETの高周波動作 が進む見込みであり、ノイズ低減などを実現する高付加価値 製品の開発に取り組んでいく。

### 横田 誠 YOKOTA Makoto

セミコンダクター社 ディスクリート半導体事業部 パワー半導体 応用技術部主務。低耐圧パワー MOSFETの商品企画及び 開発に従事。

Discrete Semiconductor Div.

### 川口 雄介 KAWAGUCHI Yusuke

セミコンダクター社 ディスクリート半導体事業部 先端ディスクリート素子開発部参事。低耐圧パワー MOSFETの開発に従事。電気学会会員。

Discrete Semiconductor Div.