一般論文 FEATURE ARTICLES

# p型MOSFETの高速化技術

High-Speed Technology of p-Type MOSFET

## 齋藤 真澄 小林 茂樹

■ SAITOH Masumi

■ KOBAYASHI Shigeki

これまで、LSIを構成するMOSFET (金属酸化物半導体型 電界効果トランジスタ) の高速化は、主にゲート長の縮小により 実現されてきた。しかし近年では、ゲート長縮小の副作用である短チャネル効果を抑制するために、基板に極めて高い濃度の 不純物を注入する必要があり、その結果、ゲート長の縮小で性能がむしろ低下する問題が生じている。

今回、p型MOSFETを作製するとき、シリコン (Si) 基板の面方位を従来のSi (100) 面からSi (110) 面に変更し、高い基板不純物濃度におけるトランジスタのキャリア移動度を大幅に向上できた。更に、チャネル部に圧縮ひずみを導入することにより、次世代以降のLSIで有望な高性能トランジスタが実現できる。

The gate length of metal-oxide-semiconductor field-effect transistors (MOSFETs) in large-scale integrations (LSIs) has been continuously shrinking to achieve improvements in the operation speed of LSIs. In recent years, however, the performance of MOSFETs has been somewhat degraded by these reductions in gate length, because the substrate impurity concentration becomes extremely high to suppress the adverse effects of the shrinkage in MOSFET size.

Toshiba has newly found that carrier mobility, which determines the performance of MOSFETs, is greatly improved even under high substrate impurity concentration by fabricating a p-type MOSFET (pMOSFET) on a silicon Si(110) substrate instead of the conventional Si(100) substrate. By further introducing strain into the channel of the MOSFET, high-performance MOSFETs can be fabricated that offer promise as future technology nodes.

#### 1 まえがき

これまで、LSIの基本構成素子であるMOSFET (金属酸化物半導体型電界効果トランジスタ)の性能向上は、主にゲート長の縮小によって実現されてきた。しかし近年では、ゲート長が30 nm程度にまで縮小された結果、ゲート長縮小の副作用である短チャネル効果 (しきい値電圧低下)を抑制するために、基板に極めて高い濃度の不純物を注入する必要が生じている。従来のトランジスタでは、基板中の不純物濃度が増加すると、電流を運ぶキャリア (電子あるいは正孔)の移動度が低下するため、ゲート長縮小による性能向上に限界が生じるという問題が起きている。LSIは、電子をキャリアとするn型トランジスタと正孔をキャリアとするp型トランジスタから構成されているが、正孔の移動度はもともと低いため、p型トランジスタでこの問題は特に深刻になっている。ゲート長縮小による性能向上の限界を打ち破るためには、基板不純物濃度が高い状況でのキャリア移動度を向上させる必要がある。

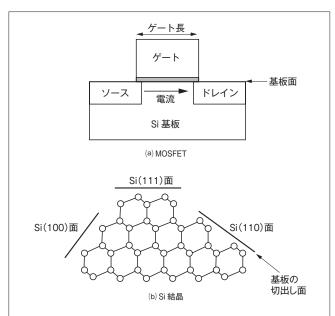

今回, 東芝は、トランジスタを作製する基板の面方位を従来のSi (100) 面からSi (110) 面に変更することで、高い基板不純物濃度におけるキャリア移動度を大幅に向上できた $^{(1)}$ 。 MOSFETとSi結晶面方位の模式図を**図1**に示す。これまでにもSi (110) 面p型 MOSFETにおける高い性能を報告した例 $^{(2)}$  はあったが、高い基板不純物濃度におけるキャリア移動度特

図1. MOSFETとSi結晶面方位の模式図 — シリコン結晶からの基板切出し面を従来のSi (100) 面からSi (110) 面に変更することで、キャリア移動度を大幅に向上できた。

Schematics of MOSFET and Si crystal structure

性を明らかにしたのは今回が初めてである。

このSi(110) 面 p 型 MOSFET の高移動度特性と、ひずみ 導入による更なる特性向上策の詳細について、以下に述べる。

#### 2 Si (110) 面p型MOSFETの高移動度特性

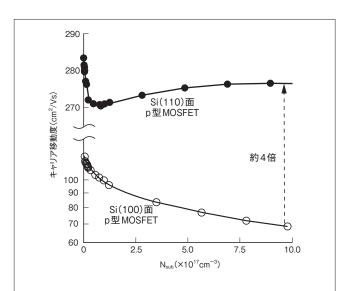

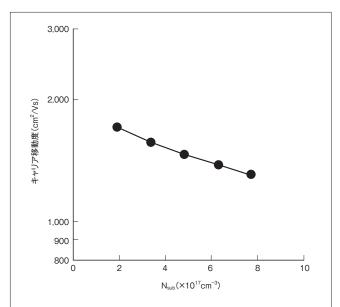

Si (100) 面基板とSi (110) 面基板上に基板不純物濃度  $N_{sub}$  条件を変えた p型 MOSFET を作製し、MOSFET のキャリア移動度を測定した。室温でのキャリア移動度の $N_{sub}$  依存性を図2に示す。従来のSi (100) 面 p型 MOSFET では  $N_{sub}$  の増加とともにキャリア移動度が急激に低下するが、Si (110) 面 p型 MOSFET では、 $N_{sub}$  が  $10^{17}$  cm<sup>-3</sup> 台で、 $N_{sub}$  の増加とともにキャリア移動度がむしろ増加している。この現象は当社が世界で初めて発見した  $({}^{(\pm 1)}$  ものである。

Si (110) 面p型 MOSFET は  $10^{17}$  cm $^{-3}$ 台の  $N_{\text{sub}}$ で移動度が増加する結果,短チャネルデバイス動作で必須となる  $1 \times 10^{18}$  cm $^{-3}$  という高い  $N_{\text{sub}}$  において,従来の Si (100) 面p型 MOSFET の約4倍という極めて高い移動度を示す。移動度が4倍になるということは,短チャネルデバイスの性能(電流)として約2倍の大幅な向上をもたらし,結果としてトランジスタの動作速度が約2倍になることを意味している。このように,Si (110) 面p型 MOSFET はゲート長縮小による性能向上の限界を打破することができるため,微細化が進む32 nm技術世代以降のLSIにおいてたいへん有望である。

次に、Si (110) 面p型 MOSFET におけるキャリア移動度増加の物理的起源について述べる。MOSFET におけるキャリア移動を考えるうえで、キャリアのエネルギー状態を正しく理解することが必要である。一般にMOSFET 中のキャリアは、基板表面付近に閉じ込められており、閉じ込められたキャリア

図2. 室温でのキャリア移動度の $N_{\text{sub}}$ 依存性 — Si~(100) 面 p 型 MOSFET ではキャリア移動度が  $N_{\text{sub}}$  の増加とともに単調に減少するが、Si~(110) 面 p 型 MOSFET ではキャリア移動度の増加が見られる。

Substrate impurity concentration dependence of mobility in Si(100) and Si (110) pMOSFETs

(注1) 2007年12月時点, 当社調べ。

はいくつかの離散的なエネルギー準位 (サブバンド) に存在している。

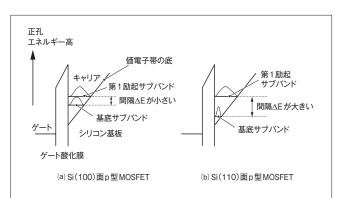

p型 MOSFETの価電子帯におけるサブバンド構造の模式 図を図3に示す。p型 MOSFETのキャリアは正孔であるが、この正孔は主に基底サブバンドと第一励起サブバンドに存在している。図3では上に向かうほど正孔のエネルギーが高いが、基底サブバンドと第一励起サブバンドのエネルギー間隔 $\Delta$ Eが大きいほど、正孔はエネルギーの低い基底サブバンドに存在することになる。

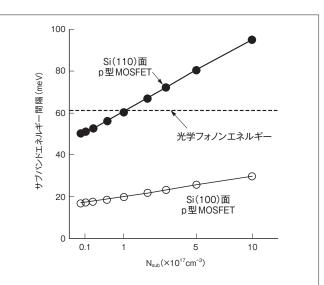

Si (100) 面p型 MOSFETとSi (110) 面p型 MOSFETにおける $\Delta$ Eの $N_{sub}$ 依存性を**図4**に示す。一般にサブバンドエネルギーのレベルは、キャリアの基板に垂直な方向 (閉じ込め方向) の有効質量mzに強く依存する。Si (110) 面p型 MOS-

図3. p型MOSFETの価電子帯におけるサブバンド構造の模式図 — Si (110) 面 p型 MOSFET では、Si (100) 面 p型 MOSFET に比べて基底サブバンドと第 1 励起サブバンドのエネルギー間隔が大きい。

Schematics of subband structures in valence bands in Si(100) and Si(110) pMOSFETs  $\,$

図4. p型MOSFETにおけるサブバンド間隔の $N_{\text{sub}}$ 依存性 — Si (110) 面 p型 MOSFET では、 $N_{\text{sub}}$ の増加とともにサブバンドエネルギー間隔が急激に増大する。

Substrate impurity concentration dependence of subband energy splitting in Si(100) and Si(110) pMOSFETs

p型MOSFETの高速化技術 55

FETでは、Si~(100) 面 p型 MOSFET に比べて基底サブバンドと第1励起サブバンドにおけるmzの違いが大きいため $^{(3)}$ 、サブバンドエネルギーレベルの差、すなわち $\Delta E$ が大きい。したがって、Si~(110) 面 p型 MOSFET では基底サブバンドを占有する正孔の割合が高い。

しかも、Si (110) 面p型 MOSFETでは $\Delta$ Eが $N_{sub}$ とともに急激に増加していく。図4中には、Siの光学フォノンエネルギー 61 meVの線を示しているが、Si (110) 面p型 MOSFETでは、 $N_{sub}$ が $1\times10^{17}$  cm $^{-3}$ 以上の領域で、 $\Delta$ Eが光学フォノンエネルギーを上回る。このことは、Si (110) 面p型 MOSFETでは $N_{sub}$ が $1\times10^{17}$  cm $^{-3}$ 以上の領域で、光学フォノンを介したサブバンド間のキャリア散乱(基底サブバンドから第1励起サブバンドへのキャリアの励起)が抑制されることを示唆する。キャリア散乱の抑制はキャリア移動度の増加に直結するため、図2で見られた、 $10^{17}$  cm $^{-3}$ 台の $N_{sub}$ でキャリア移動度が増加する現象の起源は、 $\Delta$ Eの増大によるサブバンド間散乱の抑制であると考えられる。

Si (110) 面p型MOSFETにおけるキャリア移動度の決定要因を更に明確にするため、低温でのキャリア移動度特性を測定した。熱力学温度30 KにおけるSi (110) 面p型MOSFETの移動度の $N_{sub}$  依存性を**図5**に示す。30 Kではキャリア移動度は $N_{sub}$  の増加とともに単調に減少し、室温のような $N_{sub}$  に対する増加は見られない。フォノン散乱が支配的でない低温においてキャリア移動度の増加が見られないことから、室温での移動度増加の起源は上述のとおり、サブバンド間のフォノン散乱の抑制であると考えられる。

図5. 熱力学温度30 KでのSi (110) 面p型MOSFETにおけるキャリア移動度の $N_{sub}$ 依存性 — キャリア移動度は $N_{sub}$ の増加とともに単調に減少し、室温でのような増加傾向は見られない。

Substrate impurity concentration dependence of mobility in Si(110) pMOSFET at 30 K  $\,$

#### 3 ひずみ導入による更なる性能向上

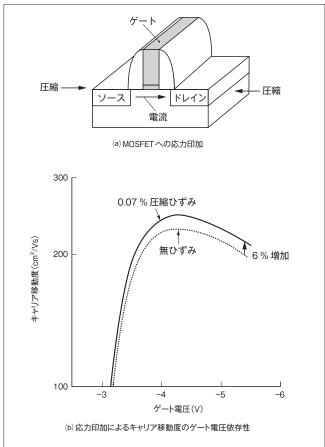

近年では、MOSFETのチャネル部に格子ひずみを導入して性能を向上させる技術が盛んに用いられるようになっている。当社は、もともと移動度の高いSi (110)面p型MOSFETにひずみを導入することによるいっそうの性能向上を検討した。実際の先端LSIでは、ゲート上に窒化膜、あるいはソース及びドレイン領域にSiゲルマニウムを形成するなど、作製プロセス上の工夫でひずみを導入する。今回は、作製プロセストの工夫でひずみを導入する。今回は、作製プロセスの変化による特性への影響を排除し、ひずみによる純粋な特性変調だけを抽出するため、素子完成後に、MOSFETが形成されている基板を機械的に曲げてチャネル部にひずみを導入する手法を採用した。

MOSFETへの応力印加の模式図と応力印加による移動度特性の変化を図6に示す。Si (110) 面p型MOSFETのゲート長の方向に圧縮性の一軸応力を印加しており、チャネル部に誘起されているひずみ量は0.07%である。0.07%の圧縮ひずみの導入により、キャリア移動度は約6%増加する。作製プロセスの工夫によって導入できるひずみ量を1%と仮定した場

図6. Si (110)面p型MOSFETでの応力印加によるキャリア移動度特性の変化 — ゲート長方向に圧縮の応力を印加することにより、Si (110)面p型MOSFETのキャリア移動度は増加する。

Mobility characteristics with and without stress in Si(110) pMOSFET

合,キャリア移動度は80%増加することが予想される。80%のキャリア移動度の増加により、トランジスタの動作速度は、ひずみを導入しない場合に比べて約40%向上すると考えられる。

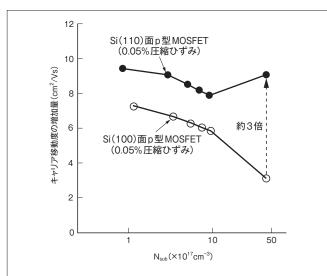

キャリア移動度と同様、ひずみによるキャリア移動度の増加量についても $N_{sub}$ 依存性を測定した。Si~(100) 面p型 MOSFETとSi~(110) 面p型 MOSFETにおける、0.05%の圧縮ひずみによるキャリア移動度増加量の $N_{sub}$ 依存性を**図7**に示す。Si~(110) 面p型 MOSFETでのひずみによるキャリア移動度の増加量は、 $\overline{n}$   $\overline{n}$

図7. 圧縮ひずみによるキャリア移動度増加量の $N_{sub}$ 依存性 — Si~(110)面p型MOSFETのひずみによるキャリア移動度増加量は、高 $N_{sub}$ 領域においてSi~(100)面p型MOSFETの約3倍に達する。

Substrate impurity concentration dependence of amount of mobility enhancement by strain in Si(100) and Si(110) pMOSFETs

#### 4 あとがき

p型 MOSFETを作製するSi 基板の面方位を従来のSi (100) 面からSi (110) 面に変え、更に、チャネルひずみを導入することで、短チャネル動作で必須となる高 $N_{\rm sub}$  領域でのトランジスタ性能を大幅に向上できることを実証した。基板の材料を変えず、基板の切出し面の方向を変えるだけで性能を向上できるこの技術は、 $32\,\rm nm$ 技術世代以降のLSIにおいてたいへん有望である。

### 文 献

- (1) Saitoh, M., et al. "Physical Understanding of Fundamental Properties of Si (110) pMOSFETs - Inversion-Layer Capacitance, Mobility Universality, and Uniaxial Stress Effects -". Tech. Dig. IEDM 2007. Washington, 2007-12, IEEE. New Jersey, 2007, p.1019—1022.

- (2) B. (F.) Yang., et al. "Stress dependence and poly-pitch scaling characteristics of (110) PMOS drive current". Dig. Symp. VLSI Tech. 2007. Kyoto, 2007-06, IEEE. 2007, p.126—127.

- (3) M. V. Fischetti, et al. Six-band kp calculation of the hole mobility in silicon inversion layers: Dependence on surface orientation, strain, and silicon thickness. J. Appl. Phys. 94, 2, 2003, p.1079-1095.

#### 齋藤 真澄 SAITOH Masumi,Ph.D.

研究開発センター LSI基盤技術ラボラトリー研究主務、工博。 ナノ電子デバイス中のキャリア輸送に関する研究に従事。 IEEE・応用物理学会会員。

Advanced LSI Technology Lab.

## 小林 茂樹 KOBAYASHI Shigeki 研究開発センター LSI基盤技術ラボラトリー。

MOSFET中のキャリア輸送に関する研究に従事。応用物理 学会会員。

Advanced LSI Technology Lab.

p型MOSFETの高速化技術 57