# 部品の設計及び製造工程を適正化するシミュレーション技術

Simulation Technology for Optimizing Component Design and Manufacturing Processes

## 中川 泰忠

#### ■ NAKAGAWA Yasutada

樹脂成形、プレス加工、除去加工、接着、及び結晶成長など多岐にわたる部品製造の分野では、品質の確保や製造時間の短縮が求められ、また、部品設計では、部品の機能や性能の向上に加えて製造性を考慮した設計が求められている。

東芝は、シミュレーションと最適化手法を用いて、製造条件や部品設計の適正化に取り組んでいる。半導体ウェーハに対しては、平たん度向上のために両面研磨工程を、また、半導体チップでは、熱硬化性樹脂接着における加熱温度履歴を適正化した。 更に、携帯情報機器に使用されるプリント回路基板 (PCB) では、リフロー工程で発生する反りを低減するために構造設計を適正化した。

Maintenance of quality and shortening of processing times are required in various component manufacturing processes such as resin molding, press processing, removal processing, adhesion, crystal growth, and so on.

To meet these requirements, Toshiba has introduced a simulation technology for optimizing component design and manufacturing processes.

In the manufacturing process, for example, the optimization of double-sided polishing conditions to enhance the flatness of silicon (Si) wafers, and of the heating temperature profile of adhesive for connecting Si chips to printed circuit boards (PCBs) in flip-chip surface mounting technology, were realized using the newly developed simulation technology. In the design of components, not only functions and performance but also manufacturability must be taken into consideration. As an example of the application of our simulation technology, the design of PCBs was optimized in order to minimize PCB deformation in the reflow process by making use of the difference in thermal expansion between copper and PCB resin.

#### 1 まえがき

半導体やプリント回路基板 (PCB) などの部品製造分野では、品質の確保や製造時間の短縮が、また、部品設計では、部品の機能や性能の向上に加えて、製造性を考慮した設計が求められている。

これらの要求に対し東芝は、製造工程における様々な現象

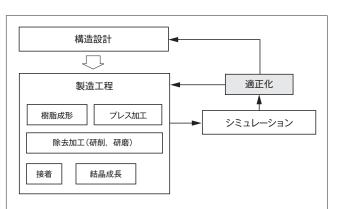

図1. 部品設計及び製造工程を適正化するためのシミュレーション技術 ― 製造性を考慮した部品設計や多岐にわたる製造工程を,シミュレーションと最適化手法を用いて適正化する。

Simulation technology for optimizing component design and manufacturing processes

をシミュレーションし、最適化手法を適用して製造条件を適正化している(**図1**)。ここでは、現象に応じてシミュレーションモデルを構築し、製造工程における除去加工や接着を適正化した事例と、PCBの設計を適正化した事例について述べる。

## 2 部品製造工程の適正化

## 2.1 除去加工

半導体回路の線幅微細化に伴い、シリコン(Si)ウェーハ(以下,ウェーハと略記)の平たん度に対する要求も厳しくなっている。当社は、ウェーハの高平たん化のために、研磨工程における加工条件を適正化してウェーハの研磨量を均一化した(1)。

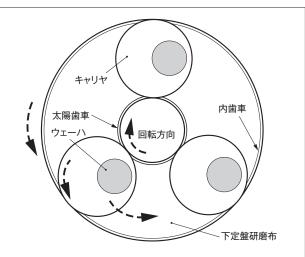

対象とした両面研磨装置の概要を**図2**に示す。両面研磨では、ウェーハを運動させるために、遊星歯車列が用いられる。この遊星歯車はキャリヤと呼ばれ、ウェーハを保持する円形の穴が設けられている。この穴の中で、ウェーハは上下の研磨布から作用する力により自転する。この歯車列を挟み込んで、研磨布をはった上定盤と下定盤を押しつけて回転させることで、ウェーハの表面と裏面を同時に研磨する。太陽歯車、内歯車、上定盤研磨布、及び下定盤研磨布の角速度は、それぞれ独立に設定できる。

この工程に対して、まず、ウェーハ中心の移動軌跡をキャリ

特

図2. 両面研磨装置の概要—下定盤はこの図の後側 (ウェーハの下)にあり、上定盤と上定盤研磨布はこの図の手前側 (ウェーハの上)にある。キャリアに保持されたウェーハを、研磨布をはった上定盤と下定盤で挟み込んで、表面と裏面を同時に研磨できる。

Outline of double-sided polishing and coordinating system

ヤ、上定盤研磨布、及び下定盤研磨布の運動から計算する。 ウェーハには上下の研磨布から作用する力により連れ回りと呼ばれる自転が発生するので、上定盤の研磨布から作用する モーメントと下定盤の研磨布から作用するモーメントとがつり 合うウェーハの自転速度を各位置で決定する。そして、ウェーハと研磨布との相対速度を時間積分して、研磨量と比例関係 にある摩擦距離を計算する。

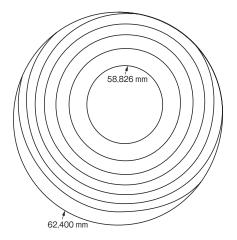

太陽歯車,内歯車,上定盤研磨布,及び下定盤研磨布の回転角速度をそれぞれ $10\,\mathrm{rpm}$ ,  $-10\,\mathrm{rpm}$ ,  $10\,\mathrm{rpm}$ ,  $-10\,\mathrm{rpm}$  とした場合の,1分間の摩擦距離をシミュレーションした結果を図3に示す。摩擦距離は最小で $58,826\,\mathrm{mm}$ ,外周側で大きくなり最大で $62,400\,\mathrm{mm}$ と,ウェーハ面内では $3,574\,\mathrm{mm}$ の摩擦距離の差異が発生しており,ウェーハ外周側の方がより多く研磨される。実験では、摩擦距離が $75,000\,\mathrm{mm}$ のときに研磨量は $0.075\,\mu\mathrm{m}$ なので、総加工時間 $150\,\mathrm{分}$ では研磨量の差異は $0.54\,\mu\mathrm{m}$ となる。この $0.54\,\mu\mathrm{m}$ が平たん度に対応する。

上記のシミュレーションモデルを用いて加工条件の適正化を実施した。前記の各回転角速度を設計変数とし、摩擦距離のウェーハ面内での差異を評価関数とする。研磨量は特定の範囲に収める必要があるので、最適化計算でも摩擦距離に上限値と下限値を設定する。また、装置を駆動するモータの出力や歯車の強度といった機構的な制限を反映して、各回転角速度の絶対値にも上限を設定する。これらの設計変数の探索には、評価関数の2階微分の計算が不要のため計算時間が少なくて済む準ニュートン法を用いた。摩擦距離の上限値と下限値、各回転角速度の絶対値に関する上限値は、ペナルティ関数を用いることで準ニュートン法による最適化の中で考慮した。

等高線間隔: 400 mm

図3. 摩擦距離のウェーハ面内分布 — シミュレーションの結果ではウェーハ面内に 3,574 mmの摩擦距離の差異が発生しており、外周側のほうがより 多く研磨される。

Distribution of friction distance in Si wafer

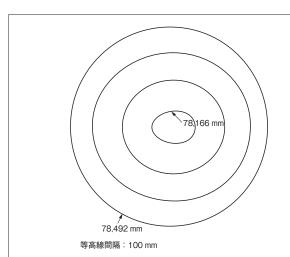

図4. 最適化した加工条件における摩擦距離のウェーハ面内分布 — 加工条件の最適化で、摩擦距離のウェーハ面内での差異が327 mmに低減され、ウェーハの平たん度を向上できる。

Distribution of friction distance in Si wafer by simulation for optimizing processing conditions

制約条件として、各回転速度の絶対値の上限には50 rpm を、摩擦距離には上限値80,000 mmと下限値70,000 mmを設定して最適化計算を実施した。この制約条件を満足しながら最適解の探索が実施され、各回転角速度はそれぞれ3.62 rpm、15.75 rpm、0.17 rpm、-0.54 rpmとなった。最適化された加工条件における、摩擦距離のウェーハ面内分布を図4に示す。摩擦距離は最小で78,166 mm、外周側で大きくなり最大で78,492 mmとなる。摩擦距離が外周側で大きくなるという傾向は図3と同様であるが、最適化した加工条件が各回転角速度に用いられることで、摩擦距離のウェーハ面内

での差異が  $327 \, \text{mm}$ に低減された。この節で設定した摩擦距離と研磨レートとの関係、総加工時間を考慮すると平たん度は  $0.05 \, \mu \, \text{m}$ となり、大幅に向上している。

#### 2.2 接着

半導体チップのPCBへの接続方法の一つとして、Siチップ 裏面に配置した接続用金属 (バンプ) を用いるフリップチップ 方式がある。フリップチップ実装では、チップとPCB間を樹 脂で封止して接着する方法が実用化されている。この方法で は応力が接着部全体に分散されるので、バンプへの応力集中 が防止できるという特長がある。当社は、樹脂封止フリップ チップ実装を対象として、樹脂を加熱する温度履歴を最適化 した<sup>(2)</sup>。

樹脂封止フリップチップ実装の概要を図5に示す。PCBとチップを接着する樹脂としては、接着・耐熱性に優れたエポキシ樹脂が用いられる。エポキシ樹脂は、PCB上にペーストやフィルムの状態で置かれる。エポキシ樹脂上にチップを配置し上方からチップを加熱することで、チップとPCBの間にあるエポキシ樹脂を硬化させる。このとき、チップ上から加圧することでエポキシ樹脂内部の気泡を外に押し出す。加熱と加圧に用いる部材には金属やセラミックスが用いられ、任意の温度履歴を与えることができる。

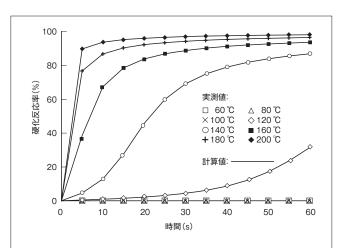

エポキシ樹脂は、加熱すると反応が進んで硬化する熱硬化性樹脂である。熱硬化性樹脂の粘度は一般に、加熱温度の上昇とともに低下するが、加熱されて硬化反応が進行すると、温度が上昇しても粘度は上昇するようになる。このような工程に対して、反応速度や粘度変化を時間と温度の関数として定式化した。これらの式において、アレニウスの式で記述される速度定数や活性化エネルギーに依存するパラメータは、実測値を再現するように推定した。硬化反応率の変化に関する実測値と計算値を八つの温度条件において比較した結果を図6に示すが、定式化した反応速度は実測値をよく再現していること

ボンディング ツール / Si チップ バンプ PCB

図5. 樹脂封止フリップチップ実装の概要 — エポキシ樹脂上にチップを配置し、上方からチップを加熱・加圧しながらPCBに接着する。

Flip-chip surface mounting technology using epoxy resin

がわかる。

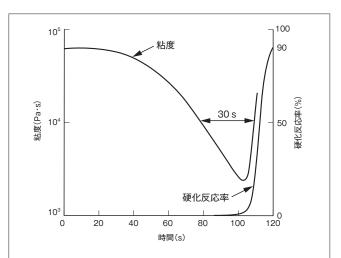

エポキシ樹脂にはPCBから発生したガスなどにより気泡が含まれる場合があるので、チップとPCBの間からエポキシ樹脂とともに気泡を外部へ排出させる必要がある。したがって、気泡の残留を防止するためには、加熱開始から一定の時間は、エポキシ樹脂が流動できるように粘度を一定の値以下に抑えておく必要がある。一方、加熱完了時にはエポキシ樹脂の接着性を確保するために、硬化反応率を一定の値まで到達させる必要がある。まず、これらの二つの要件を評価関数として設定し、次に温度履歴を多項式で表し、この温度履歴に対する硬化反応率と粘度の変化が評価関数を最小化するように温度履歴のパラメータを最適化した。ここでは、加熱と加圧の開始から粘度が10<sup>4</sup> Pa·sを下回る期間を30 sとし、加熱と加圧が終了する120 s後における硬化反応率は0.9と設定した。

図6. 硬化反応率の解析値と実測値との比較 — それぞれの温度条件において, 硬化反応率の計算値は実測値をよく再現している。

Comparison of experimental and calculated curing rate data

図7. 最適化した硬化反応率と粘度の履歴 — 温度履歴を最適化することで、粘度と硬化反応率に求められる要件を達成している。

Optimized curing rate and viscosity profiles

最適化した温度履歴における硬化反応率,及び粘度の変化を**図7**に示す。接着工程の前半部分では,温度上昇を抑えて硬化反応を抑制することで,粘度が10<sup>4</sup> Pa·sを下回る期間を30 s確保している。そして後半では,温度を上昇させて硬化反応を進め、目標とする硬化反応率を達成している。

#### 3 PCB設計の適正化

携帯情報機器に用いられるPCBは、銅はくによる回路パターンをもつ銅はく層と樹脂を基材とする絶縁層を、交互に積層した構造である。銅はく層で回路がない部分には、絶縁層と同様の樹脂が存在する。

加熱してPCBに部品をはんだ付けするリフロー工程では、 銅と樹脂との線膨張係数の相違からPCBに反りが発生する 場合がある。PCBに発生した反りが大きくなると、部品とはん だが密着せず接続不良が発生する。

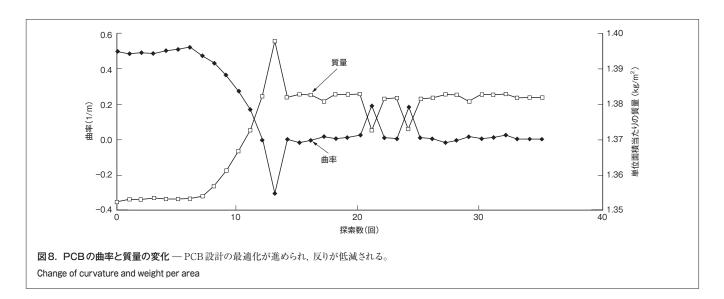

従来、PCBに発生する反りを防止するために、銅はく層の銅パターンの変更が経験的に行われている。これは、回路の電気的機能に影響しない範囲で銅はく層に銅パターンを追加する方法で、銅はく層の見かけの線膨張係数と弾性係数を変更することによりPCB全体の反りを低減する。この方法を用いて、PCBの銅はく層の最適設計を実施した(3)。

まず、リフロー時のPCBの反りをシミュレーションするために、銅はく層の機械的物性を複合材料の微視力学に立脚してモデル化した。そして、銅はく層と絶縁層の積層構造を複合材料の積層理論を用いてモデル化し、温度変化に対するPCBの曲率を解析できるようにした。このシミュレーションモデルに対して最適化手法を適用し、リフローにおける反りを最小化するように各銅はく層における銅はくの面積比を適正化した。最適化計算では、各銅はく層において銅が占める面積比を設計変数とし、また、製品仕様から決められるPCB質量の

上限値と, 電気回路としての機能から決められる銅はくの面 積比の上限値と下限値を, 最適化計算の中で制約条件として 考慮した。

携帯情報機器用のPCBに適用した事例を次に示す。このPCBは6層の銅はく層と5層の絶縁層を交互に積層した構成で、銅はく層の厚さは0.018 mm、絶縁層の厚さは0.1 mmである。PCBの重量の上限値は1.4 kg/m²、銅はくの面積比の上限値は0.9とし、銅はくの面積比の下限値は、電気設計から決定した銅パターンがPCBに占める面積比で設定した。

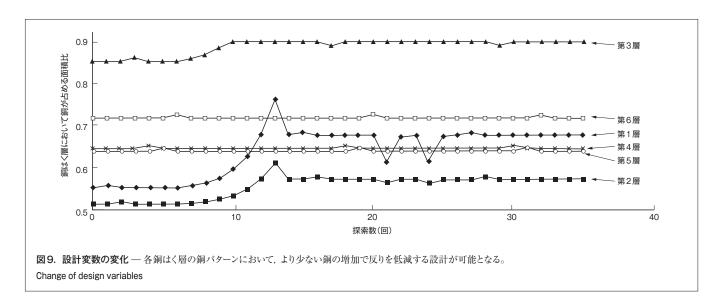

最適解の探索過程におけるPCBの曲率と質量の変化を図8に、設計変数の変化を図9に示す。初期設計では、銅はくの第1層よりも第6層で、第2層よりも第5層でそれぞれ銅が占める面積比が高い。線膨脹係数は樹脂よりも銅のほうが高いため、第6層側の膨脹量が相対的に大きくなる。このために、第1層側が凹となる反りとなっている。各銅はく層における銅パターンの面積比に関する探索が実施された結果、曲率は低減し、PCB単位面積当たりの質量も初期設計から増加はしたが、上限値の1.4 kg/m²には達していない。

初期設計では、銅はくの第1層側が凹となる変形なので、PCBの厚さ方向の中央面を指す中立線を挟んで第1、第2、第3層の銅パターンの面積比が増加するか、第4、第5、第6層の銅パターンの面積比が減少することで変形が低減する。ただし、電気回路を成立させるために銅はく層全面を銅とすることはできないので、面積比には上限の制約条件が設定されている。第3層では、この上限の制約条件が有効となった銅はくの面積比となっている。また、PCB表面の銅はく層のほうが内部の層よりも面積比の増加量が大きい。中立線から遠い銅はく層における線膨脹係数の変化のほうが、近い銅はく層における線膨脹係数の変化のほうが、近い銅はく層における線膨脹係数の変化のほうが、近い銅はく層における線膨脹係数の変化のほうが、近い銅はく層における線膨脹係数の変化よりも、温度変化時のPCBの曲げモーメントに与える影響が大きいので、より少ない銅の増加で反りを低減する設計が実現されていることがわかる。

## 4 あとがき

製造工程における除去加工や接着,及びPCBの設計に,シミュレーションと最適化手法を適用した事例について述べた。製造性を考慮した設計は様々な部品で求められており,その適正化を実現するためには、多様な製造工程と部品構造を再現するシミュレーション技術が必要となる。

これに応えるため当社は、機械系シミュレーション技術に加 えて、様々な物理量や相状態を扱うことが可能なマルチフィ ジックスシミュレーションの開発を進めている。

## 文 献

(1) 中川泰忠. 両面研磨における摩擦距離のウェーハ面内分布均一化のための加工条件最適化. 精密工学会誌. 72, 5, 2006, p.641 - 646.

- (2) 中川泰忠. 樹脂封止フリップチップ実装における加熱温度履歴の最適化. 日本機械学会論文集. 72, 713C, 2006, p.1-6.

- (3) 中川泰忠、プリント回路基板のリフロー工程における反り低減のための最適設計. 日本機械学会論文集. 72, 719C, 2006, p.2021 2026.

中川 泰忠 NAKAGAWA Yasutada 生産技術センター 部品技術研究センター研究主幹。 部品設計, 部品製造に関するシミュレーション業務に従事。 日本機械学会, 精密工学会会員。 Machinery Component Technology Research Center