一般論文 FEATURE ARTICLES

# メディア処理向け 動的再構成可能 LSI

Dynamically Reconfigurable LSI for Media Application

吉川 宜史 山田 裕 浅野 滋博

■ YOSHIKAWA Takashi

■ YAMADA Yutaka

■ ASANO Shigehiro

LSIの微細化や機能の複雑化に伴い,その開発コストは年々増大しており,特に,画像や音声を処理するメディア処理向け LSIにおいては,デジタル機器の多様化やメディア処理の急速な進化に合わせて,開発頻度が増している。そのため,開発回数の 削減や開発期間の短縮によりコストを低減できる,プログラマブルなLSIへの期待が高まっているが,従来の製品は面積や消費 電力が大きく,高性能・小面積・低消費電力が要求されるデジタル機器への適用は困難だった。

東芝は、このような市場ニーズに応えるため、メディア処理向けの高性能プログラマブルLSIの開発を進め、処理に合わせてLSIの構成を動的に変更する動的再構成技術を、メディア処理に特化して応用することで、小面積化と低消費電力化を実現した。このLSIを用いることで、様々なメディア処理向けLSIの開発をメディア処理用ソフトウェアの開発に置き換えることが可能となり、LSI開発コストの低減が期待できる。

The cost of developing large-scale integrations (LSIs) has been rising year by year with their increasing miniaturization and complexity of functions. At the same time, the frequency of LSI development has been increasing for media applications such as audio and video processing due to the diversification of digital devices and rapid progress of media processing. The realization of programmable LSIs is expected to reduce the cost by reducing the frequency of development or shortening the development period. However, the conventional products have had critical issues such as large area and high power dissipation.

With this as a background, Toshiba has developed a high-performance programmable LSI specifically for media processing that achieves a small area and low power dissipation by utilizing dynamic reconfiguration technology for the programmability of media applications. The use of this dynamically reconfigurable LSI makes it possible to implement software development for media processing instead of new LSI development, thereby reducing LSI development costs.

#### 1 まえがき

動画像や音声の符号化・復号化処理,画像認識などのメディア処理は,デジタルのテレビやカメラなど,デジタル機器の基本機能を実現する重要な処理である。

近年、デジタル機器の高精細化や多様化が急速に進むにつれ、メディア処理向けLSIの開発頻度が増大しており、このLSIの開発コスト低減が重要な課題となっている。

そこで東芝は、単一のLSI上で様々なメディア処理を実現することで開発頻度を低減させるため、メディア処理に合わせて構成を動的に変更できるLSI (動的再構成可能LSI) を開発した。ここでは、その概要、特長などについて述べる。

#### 2 東芝の動的再構成可能 LSIの概要

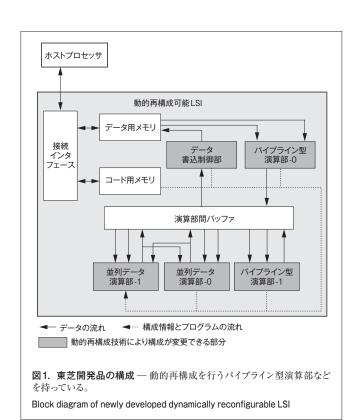

当社が開発した動的再構成可能LSI(以下,当社開発品と言う)の構成を**図1**に示す。ホストとなるプロセッサから転送されるデータに対して、同様にプロセッサから転送されるプログラムコードと構成情報により規定される一連の演算を行う、プログラマブルなメディア処理向けLSIである。

プログラムコードに従って次々と構成情報を選択して,演算を行う演算器や,演算器間を接続する経路の構成を高速に変更する動的再構成技術により,様々なメディア処理を実現する。

当社開発品は、メディア処理の特徴に合うよう演算器の配置や演算器間の接続を工夫した、パイプライン型演算部などの演算部、演算部間のデータ転送を実現する演算部間バッファ、プロセッサとLSIの接続インタフェース、プロセッサから転送されるデータや構成情報などを格納するメモリ、及び演算結果をメモリに書き込むデータ書込制御部から構成される。

プロセッサが、必要なデータ、プログラムコード、及び構成情報をLSIに転送した後、LSIに処理の開始を通知することでメディア処理が開始される。

初めにパイプライン型演算部-0がデータメモリからデータを 読み出し、プログラムコードに従って構成を変更しながら演算 を行って、結果を演算部間バッファに書き込む。ほかの演算部 は、自身にあてられた演算部間バッファ上のデータに対して演 算を行い、その結果を演算部間バッファに書き込む。このよう にして規定の数だけ演算を行なった後、演算結果はデータ書 込制御部に転送され、データメモリに書き込まれる。以上が 一つのデータ処理における流れである。

このようなデータ処理を次々と行うことで、一つのメディア処理が実現される。それぞれのデータ処理は逐次実行されるのではなく、一つのデータ処理の結果がデータメモリに書き込まれる前に、後続のデータ処理は随時開始されていく。このようにして、LSI上で複数のデータ処理を並列に実行することで、高い演算性能が得られる。

# 3 東芝の動的再構成可能LSIの特長

ここでは、当社開発品の二つの特長について述べる。

## 3.1 小面積と低消費電力

動的再構成可能LSIは、プログラムコードや構成情報を格納するメモリが必要なことや、様々なメディア処理を実現できるように演算器の数や演算器間の経路数を多くしていることから、特定のメディア処理だけを実現する専用LSIと比べて面積や消費電力が増大する。この増大の程度を小さくするために、メディア処理への適性を大きく損なわずに冗長な演算器や経路などの演算資源を削減した。

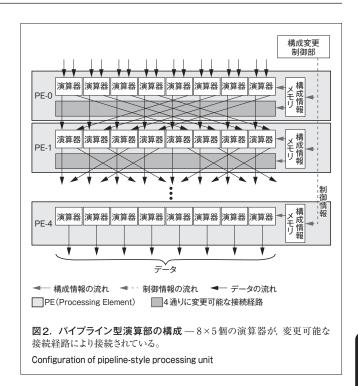

例えば、パイプライン型演算部(図2)には8列×5行の40個の演算器があるが、それぞれの演算器は隣接する行にある4個の演算器だけと一方向に接続可能であり、同じ行にある演算器間を接続してデータの受け渡しをさせるようなことはできない。同じ行や列にある任意の演算器間で双方向にデータの受け渡しができる従来の動的再構成可能LSIと比べると、接続の数は大幅に削減されている。

しかしながら、メディア処理では、データに対して流れ作業

(パイプライン)式に順に演算が行われるため、上の演算器から一つ下の演算器への接続が十分にあれば、ほかの接続を削減してもメディア処理への適性が大きく損なわれることはない。

一方で当社開発品が持つ接続の中には、次段の四つ隣の演算器への接続のように、従来品にはないものもある。このような接続を用いると、メディア処理の基本となる行列演算を従来よりも少ない演算器で実現できるようになり、性能を落とすことなく、LSIに必要な演算器の数を削減することもできた。

#### 3.2 メディア処理に適した構成変更方式

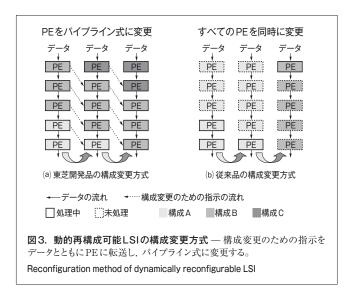

単一のLSI上で様々なメディア処理を実現するためには、いろいろなデータ処理に柔軟に適応できるよう、LSIの構成変更を高速に行う必要がある。当社開発品では、従来品とは異なる独自の構成変更方式を採ることで、従来よりも高速な構成変更を実現している(図3)。

従来品では、構成変更制御装置からの指示に従って、演算器の構成や演算器間の接続経路などを同時に変更する。変更そのものにかかる時間は極めて短いが、演算中の演算器が一つでも存在する間はそれらを変更できないため、すべての演算が完了するのを待って行う必要がある。そのため、高速での変更はできない。

一方、当社開発品では、構成変更制御装置からの指示は データとともに演算器や接続経路に伝わり、それらが到着した 演算器や接続経路だけが、その指示に従ってデータ処理に必 要な構成に変化する。このような構成変更方式を取ることで、 演算中の演算器が存在する間でも、構成変更制御装置はデー タとともに次々と指示を送ることができる。そのため、それぞ れの演算器や接続経路の構成を高速で変更できる。

# 4 コード開発環境

様々なメディア処理を1個のLSIで行えるようになれば、開発の対象をメディアごとの専用LSIから、プログラムコードや構成情報といった当社開発品用のソフトウェアへ置き換えることができる。あるメディア処理を行うためのソフトウェアの開発コストが、そのメディア処理専用のLSIを開発するコストより小さくできれば、全体の開発コストを低減できることになる。このような理由で、ソフトウェアの開発を容易にするコード開発環境は重要であり、LSIの開発と並行して、その構築も進めている。

コード開発環境の構築においては、当社開発品用のソフトウェアは、より多くのソフトウェアエンジニアが携われるよう、標準的な開発手法であるC言語記述による開発を目指している。

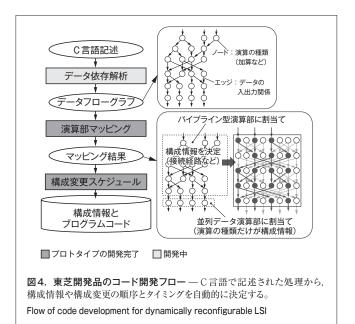

当社開発品のソフトウェアをC言語から自動生成するためのコード開発フローは、**図4**のようになる。

まず、C言語による可読性が高いメディア処理の記述を解析し、その処理で行われる演算と演算間のデータ受け渡しの関係を求め(データ依存解析)、それを機械的に処理しやすいようにグラフで表現する。

次に、当社開発品が持つ演算部の特性を考慮してグラフを 複数の部分グラフに切り分け、それぞれをどれかの演算部に 割り当てた後(演算部マッピング)、その部分グラフを演算する ための構成情報を出力する。

最後に、データ依存解析により得られた演算間のデータ受け渡し関係を考慮して、演算実行のためにそれぞれの演算部で行われる構成変更の順序とタイミングを決定し(構成変更スケジュール)、それをプログラムコードとして出力する。このようにして、当社開発品のソフトウェアである構成情報とプログラムコードが、C言語によるメディア処理の記述から自動生成される。

現在は、開発フローにおける演算部マッピング以降のフローまでのプロトタイプが完成しており、データ依存解析部分の開発を進めている。データ依存解析は、プロセッサ用のコンパイラでも行われている処理であり、既存の技術を効果的に利用することで開発を加速することができる。

#### 5 性能評価

ITU (国際電気通信連合)のH.264規格で符号化された動画像の復号処理性能について、当社と他社のプログラマブルLSIを比較した。動画像の復号処理には、様々なメディア処理アプリケーションで使用される基本的なデータ処理が多く含まれているため、メディア処理性能の評価に適している。比較対象のLSIは、ARM社のプロセッサであるCortex-A8と、IMEC (Interuniversity Microelectronics Center)の動的再構成可能LSIであるADRESとした。これらのLSIを用いてH.264規格で符号化された動画像を復号した際の処理性能は公開されている(1)-(3)。当社開発品のデータは、シミュレーションによる結果である。

90 nm 半導体プロセスにおけるそれぞれのLSIの面積と、H.264規格で符号化された動画像を復号した際の消費電力及び性能を比較した結果を**表1**に示す。Cortex-A8については、参考文献(2)の面積と文献(1)の消費電力は65 nm半導体プロセスでの値なので、面積を2倍、消費電力を1.4倍した。ADRESについては、130 nm半導体プロセスでの値なので、面積を0.5倍、消費電力を0.7倍した後、動作周波数300 MHzで比較するため、性能と消費電力をそれぞれ3倍した。

性能だけ比較すると、Cortex-A8は当社開発品と同等であるが、面積と消費電力の効率は当社開発品よりも低い。その

表1. プログラマブルLSIの復号処理性能, 面積, 及び消費電力の比較 Comparison of image decoding performance, area, and power consumption of programmable LSIs

| 項目                | 性能      |           |       |  |  |

|-------------------|---------|-----------|-------|--|--|

|                   | 東芝開発品   | Cortex-A8 | ADRES |  |  |

| 復号処理性能 (×104画素/s) | 1,843.2 | 1,711.5   | 760.3 |  |  |

| 面 積 (mm²)         | 4.5     | 8         | 7.5   |  |  |

| 消費電力 (mW)         | 143     | 420       | 97    |  |  |

ことを端的に示すために、 $1 \text{ mm}^2$ 当たりの性能(面積当たりの性能)と1 mW当たりの性能(消費電力当たりの性能)を比較した (**表2**)。

表2. 面積当たり及び消費電力当たりの復号処理性能の比較 Comparison of performance per power consumption and unit area of programmable LSIs

| 項目                       |                            | 性 能                                      |           |       |       |

|--------------------------|----------------------------|------------------------------------------|-----------|-------|-------|

|                          |                            | 東芝開発品                                    | Cortex-A8 | ADRES |       |

| 復号処理 面積当たり<br>性能 消費電力当たり | 面積当たり                      | (×10 <sup>4</sup> 画素/s/mm <sup>2</sup> ) | 409.6     | 213.9 | 101.4 |

|                          | (×10 <sup>4</sup> 画素/s/mW) | 12.9                                     | 4.1       | 7.8   |       |

一般にプロセッサは、少ない演算器を高い動作周波数で高速に使いまわすことで性能を向上させているため、面積効率は従来品より良いが、消費電力は大きくなる傾向にある。逆に、従来品は、多数の演算器や演算器間の様々な接続経路を利用して大量の演算を並列実行しているので、低い動作周波数でも高い性能が得られ、消費電力効率はプロセッサより良いが、面積は大きくなる傾向にある。

当社開発品では、メディア処理においては冗長な演算器や接続経路を削除するとともに、独自の構成変更方式により少ない演算資源で高性能を実現しているため、面積と消費電力は従来のプログラマブルなLSIよりずっと小さくなるという結果になった。

### 6 あとがき

メディア処理に特化した動的再構成技術の応用により,面積効率が従来の動的再構成可能LSIの約4倍,消費電力効率

がプロセッサの約3倍となるなど、小面積で低消費電力のLSI を実現できることがわかった。

今後は、LSIの試作などにより評価精度を向上させるとともに、C言語ベースのコード開発フローを完成させる。また、メディア処理以外の分野への動的再構成技術の応用についても検討していきたい。

# 文 献

- (1) ARM Limited. "Architecture and Implementation of the ARM Cortex-A8 Microproessor".<a href="http://www.arm.com/pdfs/Tiger">http://www.arm.com/pdfs/Tiger</a> Whitepaper Final.pdf>, (参照 2008-03-21).

- (2) ARM Limited. "ARM Cotex-A8".<a href="http://www.arm.com/products/CPUs/ARM\_Cortex-A8.html">http://www.arm.com/products/CPUs/ARM\_Cortex-A8.html</a>, (答照 2008-03-21).

- (3) Veredas, F., et al. "Custom Implementation of the coarse grained reconfigurable ADRES architecture for multimedia purposes". International Conference on Field-Programmable Technology. Singapore, 2005-12, IEEE. p.106-111.

吉川 宜史 YOSHIKAWA Takashi

研究開発センター コンピュータ・ネットワークラボラトリー研究主務。システム LSI の研究・開発に従事。 Computer & Network Systems Lab.

山田 裕 YAMADA Yutaka

研究開発センター コンピュータ・ネットワークラボラトリー。 システムLSIの研究・開発に従事。電子情報通信学会会員。 Computer & Network Systems Lab.

浅野 滋博 ASANO Shigehiro

研究開発センター コンピュータ・ネットワークラボラトリー研 究主幹。システムLSIの研究・開発に従事。IEEE会員。 Computer & Network Systems Lab.