一般論文 FEATURE ARTICLES

# Ku帯 50W級 GaN HEMT

Ku-Band 50 W-Class GaN HEMT

# 高木 一考 松下 景一 小野寺 賢

■ TAKAGI Kazutaka

■ MATSUSHITA Keiichi

ONODERA Ker

衛星通信基地局などで用いられるマイクロ波固体化増幅器向けの高周波・高出力素子として、Ku帯 (12~15 GHz帯) において出力50 W (注1)を超える、窒化ガリウム (GaN) HEMT (High Electron Mobility Transistor:高電子移動度トランジスタ) の開発に成功した。

これは、既開発のX帯  $(8\sim12~\text{GHz}$ 帯)  $50~\text{W}^{(\pm2)}$ 級 GaN HEMT (() を基に、高周波で良好な特性を引き出すために、新たに開発した貫通電極 (ビアホール) 形成技術を適用し接地性を改善することで、14.5 GHz において最高 65~W の出力を達成したものである。これによって、Ku帯においても増幅器の固体化がいっそう進むと期待できる。

Toshiba has developed a gallium nitride high-electron-mobility transistor (GaN HEMT) with an output power exceeding 50 W for the Ku-band (12-15 GHz) frequency range used in base stations for satellite microwave communications, radar systems, and other applications. We adopted a via-hole technology newly developed for semiconductor dies at Ku-band frequencies, based on the technology developed for X-band (8-12 GHz) GaN HEMTs. The new device achieved a peak output power of 65 W at 14.5 GHz. Solid-state amplifiers incorporating this HEMT are expected to replace electron tubes for Ku-band applications.

# 1 まえがき

近年、情報量の増大に伴い、Ku帯を使う衛星通信への期待が高まっている。その基地局のマイクロ波固体化増幅器などに用いられる増幅素子は、C帯(4~8 GHz帯)の増幅素子に比べて出力が低く、いっそうの高出力化が求められている。しかし、空洞共振が生じる周波数をその素子が使用される周波数帯域よりも高く保つために、増幅素子のパッケージサイズ、特に幅には上限があり、内蔵するチップの幅もおのずと制限される。チップ幅が限られていることに加えて、放熱性を確保するために電極間隔にも下限がある。相反する高周波特性と放熱特性を両立させるため、ガリウムヒ素(GaAs)では、素子出力は30 Wが限界となっている(2)。

一方, 固体化増幅器の内部では増幅素子を並列接続して, 大きな出力を得るが, その電力合成は周波数が高くなるほど 難しい。実用的な合成効率をもって電力合成できる増幅素子 の数も4合成が一般的で, 100 Wが固体化増幅器の上限と なっていた。

GaNは、GaAsやシリコン (Si) に比べて、より高い絶縁破壊電界を持つことから、より高出力な素子が実現できる可能性のある材料である。既にL帯  $(1\sim 2\,GHz$ 帯) では絶縁破壊電界の高さを生かし、その動作電圧を上げ、 $200\,W$ を超える増幅素子が数多く発表されている。GaNはGaAsやSiに比べ

(注1) Ku帯の中の14 GHz帯 (14~14.5 GHz帯) における出力

(注2) X帯の中の9 GHz帯 (8.5~9.5 GHz帯) における出力

て、高い絶縁破壊電界に加え、より大きな電子飽和ドリフト速度を持つことから、高周波素子に適した材料でもある。このような材料特性を生かすことにより、小さなチップから大きな出力を引き出すことができ、Ku帯においても、GaNはGaAsを大きく上回る出力を達成することが期待できる。

ここでは、高周波で高出力の一例として、Ku帯 50 W級 GaN HEMTの概要、技術課題と解決方法、及び特性例について述べる。

#### 2 Ku帯 50W級 GaN HEMTの概要

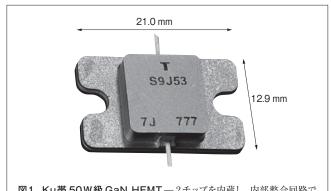

Ku帯 50W級 GaN HEMTの外観を**図1**に示す。21.0×12.9 mmのパッケージにGaN HEMTチップが二つ実装され

図1. Ku帯 50W級 GaN HEMT — 2チップを内蔵し、内部整合回路で入出力端子ともに50  $\Omega$ に整合されている。

Newly developed GaN HEMT

ている。内部整合回路で二つのチップを電力合成し、入力・ 出力端子を $50\,\Omega$ に整合している。

## 3 技術課題と解決方法

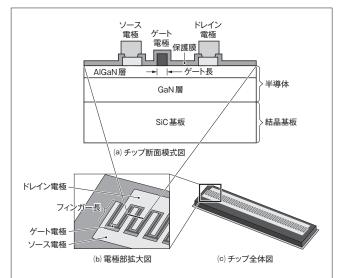

Ku帯でのチップ開発の技術課題は利得の確保である。GaN HEMTチップの模式図を図2に示す。図2(b)に示すように、GaN HEMTチップにはゲート電極、ソース電極、及びドレイン電極が櫛(くし)状に並んでいる。フィンガーを長くするほど、一つのチップから出せる出力を大きくできるが、フィンガーが長くなるにつれて、フィンガー上の位相の違いが無視できなくなり利得は低下する。

ゲート電極はゲート容量を持ち、ゲート長の増加に伴ってそ の容量が大きくなるほど、利得は低下する。

ソース電極はパッケージの接地面に接続されるが、そのソース電極と接地面の間にインダクタンスが生じる。そのインダクタンスが大きくなるほど、利得は低下する。

周波数が高くなるにつれて、位相差、ゲート容量、及び接地 インダクタンスの影響を強く受けるようになり、利得は低くな る。そこで、利得の低下が最小限に抑えられるようフィンガー 長、ゲート長、及び接地インダクタンスの最小化を検討した。

図2. GaN HEMTチップの模式図 — 利得の低下が最小限に抑えられるようフィンガー長、ゲート長、及び接地インダクタンスの最小化を検討した。 Schematic of GaN HEMT

#### 3.1 位相差の影響

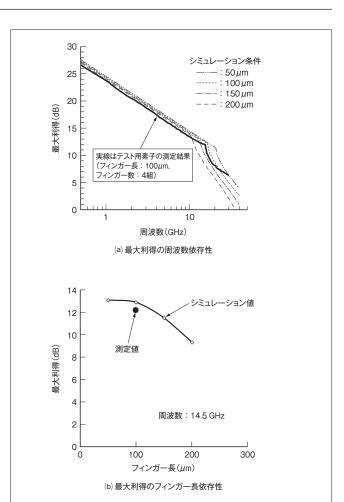

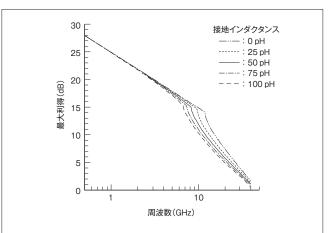

最大利得の周波数及びフィンガー長依存性を図3に示す。

図3(a)の実線は、フィンガー長100 $\mu$ m、フィンガー4組のテスト用素子をウェーハ状態で、高周波プローブを用いて測定したときの最大利得の周波数依存性である。この測定データを元にフィンガー長100 $\mu$ mの素子モデルを作成し、更に、

図3. 最大利得の周波数及びフィンガー長依存性 — MSGは、周波数に対して3 dB/オクターブで低下し、フィンガー長の影響をほとんど受けない。MAGは、周波数に対して6 dB/オクターブで低下する。フィンガー長を $100 \mu$ mよりも長くすると、14.5 GHzにおける利得はMSGからMAGに変わり、利得の低下が顕著になる。

Finger-length dependence of maximum gain

フィンガー長  $100 \mu m$ の素子モデルをスケーリングして、フィンガー長が 50, 150, そして  $200 \mu m$ の素子モデルを作成した。これらのモデルを用いてシミュレーションした最大利得の周波数依存性を、図 3(a)に併せて示した。

この結果から、低い周波数では、最大利得は最大安定利得(MSG: Maximum Stable Gain)で表され、MSGは周波数に対して3dB/オクターブで低下する。MSGは、フィンガー長の影響をほとんど受けないことがわかる。高い周波数では、最大利得は最大有能利得(MAG: Maximum Available Gain)で表され、MAGは周波数に対してほぼ6dB/オクターブで低下する。MAGはMSGに比べてフィンガー長の影響を強く受ける。

$14.5~{\rm GHz}$ における最大利得のフィンガー長依存性を図3(b)に示す。フィンガーを $100~\mu{\rm m}$ よりも長くすると $14.5~{\rm GHz}$ における利得は ${\rm MSG}$ から ${\rm MAG}$ に変わり、利得の低下が顕著になることがわかる。この結果から、今回、チップのフィンガー長

Ku帯 50W級 GaN HEMT 41

は $100 \mu m$ とした。

# 3.2 ゲート容量の影響

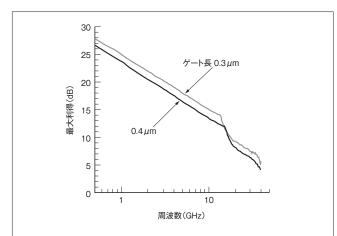

ゲート容量が小さいほど、最大利得は高くなる。ゲート容量を小さくするためには、ゲート電極を微細化することが有効である。ゲート長が $0.4\mu$ mと $0.3\mu$ mのテスト用素子を作製し、その最大利得を測定した(**図4**)。ゲート長を $0.4\mu$ mから $0.3\mu$ mにしたことで、利得は約 $1\,d$ B上がった。現行のGaN素子製作プロセスでは、安定に形成できるゲート長の最小値が $0.3\mu$ mであることも考慮し、ゲート長は $0.3\mu$ mとした。

**図4. 最大利得のゲート長依存性** — 測定したテスト用素子のゲート長は、 $0.4 \mu m \ge 0.3 \mu m$ である。ゲート長を25 % 御細化したことで、利得が約 1 dB 上がった。

Gate-length dependence of maximum gain

#### 3.3 接地インダクタンスの影響

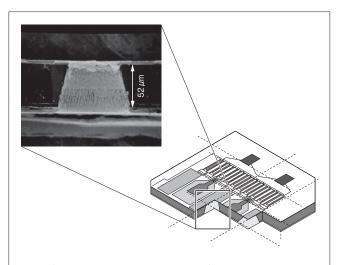

先に製品化した X 帯 GaN HEMTでは、金線でソース電極とパッケージの接地面をつないでいる。金線の長さは200 μm にもなるため、この方法では100 pH 程度の接地インダクタンスを生じる。図5は、最大利得の接地インダクタンス依存性をシミュレーションした結果である。長さ100 μmのフィンガー10組で構成される評価用素子モデルに対し、その接地との間にインダクタンスを0 pHから100 pHまで加えたときの最大利得を計算した。この結果から、MSGは接地インダクタンスの影響を受けないが、MAGは接地インダクタンスが大きいほど低くなることがわかる。接地インダクタンスを小さくするために、炭化ケイ素(SiC)基板は50 μmまで薄くしてチップにビアホールを設け、金線の代わりにこのビアホールでソース電極とパッケージの接地面をつないだ。GaAsでは、このビアホールによる接地が一般的に用いられているが、化学的に安定性の高い

図5. 最大利得の接地インダクタンス依存性 — 長さ100  $\mu$ mのフィンガー10組に対し、接地インダクタンスを0 pHから100 pHまで変えて最大利得を計算した。MSG は接地インダクタンスの影響を受けないが、MAG は接地インダクタンスが大きいほど低くなる。

Grounding-inductance dependence of maximum gain

SiC基板(注3) にビアホールを形成するためには、独自プロセスの開発が必要であった。そこで、RIE (Reactive Ion Etching) 条件を最適化し、断面がテーパ状のビアホールを形成することに成功した。これにより裏面電極が形成しやすくなり、ビアホール内電極の段切れが防止できる。

ビアホールによる接地を示す模式図と, ビアホールの断面 SEM (走査型電子顕微鏡) 写真を図6に示す。

図6. ビアホールによる接地を示す模式図とビアホールの断面SEM写真 - 深さ約50 μm, 断面がテーパ状のビアホールを形成することに成功した。 Cross-sectional view of via hole of GaN HEMT

#### 3.4 Ku帯 50W級 GaN HEMT チップの構成

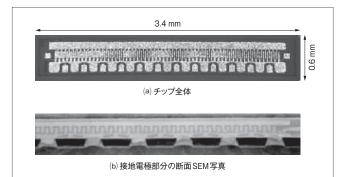

開発したGaN HEMTチップを**図7**に示す。チップサイズは $3.4 \times 0.6$  mmである。これまで検討してきた結果に基づき、フィンガー長  $100~\mu$ mの電極を120 組並べ、12 個のビアホールを設け、ゲート長は $0.3~\mu$ m、総ゲート幅は $12~\mu$ mとした。

<sup>(</sup>注3) GaN HEMTは、サファイア、SiC、及びSiなどといった結晶基板を下地として、その上にGaN層や窒化アルミニウムガリウム(AIGaN)層などをMOCVD法(Metal-Organic Chemical Vapor Deposition: 有機金属気相成長法)を使って、動作層として形成する。当社は、SiCを用いている。

図7. Ku帯 50 W級 GaN HEMTチップ — チップサイズは  $3.4 \times 0.6$  mm, 厚さは  $50~\mu$ m である。

Newly developed GaN HEMT chip

## 4 Ku帯 50W級 GaN HEMTの特性例

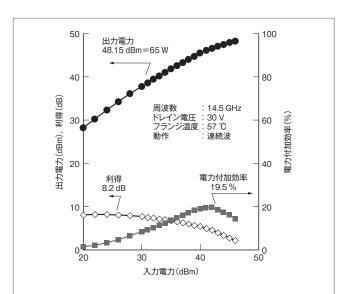

3章で述べたGaN HEMTチップ2個を内部整合回路とともにパッケージに実装した素子の入出力特性を図8に示す。ドレイン電圧30 V,測定周波数14.5 GHzで飽和出力48.15 dB (65 W)を得た。このときの線形利得は8.2 dB,電力付加効率は19.5 %であった。

**図8. パッケージ実装した素子の入出力特性** — 測定周波数14.5 GHzにおいて, 飽和出力65 Wを得た。

Input vs. output characteristics of newly developed GaN HEMT

#### 5 あとがき

今回,フィンガー長を最適化し、ゲート長を短縮するとともに、新たに開発したビアホール形成技術を適用してチップの接地性を改善することで、14 GHz帯において目標出力の50 Wを超える GaN HEMTの開発に成功した。今後、電力付加効率の向上を目指して更に改善を続ける。

#### 文 献

- (1) 高木一考,ほか、X帯 50 W 級 GaN電力 HEMT. 東芝レビュー、62,4,2007, p.42 - 45.

- (2) 高木一考, ほか. Ku帯 30W電力FET. 東芝レビュー. 60, 11, 2005, p.49-52.

- (3) 松下景一, ほか. C帯 150W級GaN電力HEMT. 東芝レビュー. 60, 12, 2005, p.32-35.

- (4) Matsushita, K., et al. "Ku-band AlGaN/GaN HEMT over 65W". ISCS2007. Kyoto, 2007-10, International Symposium on Compound Semiconductors. 2007, p.159.

高木 一考 TAKAGI Kazutaka

社会システム社 小向工場 マイクロ波技術部参事。 マイクロ波半導体のデバイス設計・開発に従事。 応用物理学会会員。

Komukai Operations

松下 景一 MATSUSHITA Keiichi

社会システム社 小向工場 マイクロ波技術部主務。 マイクロ波半導体及び半導体製造プロセスの設計・開発に 従事。応用物理学会会員。

Komukai Operations

#### 小野寺 賢 ONODERA Ken

社会システム社 小向工場 マイクロ波技術部主務。 マイクロ波半導体及び半導体製造プロセスの設計・開発に 従事。

Komukai Operations

Ku帯 50W級 GaN HEMT 43