# Cell 電源システム

**Power Supply System for Cell Broadband Engine**

武井 洋 武本 昭彦 山口 大介

■ TAKEI Hiroshi ■ TAKEMOTO Akihiko

5V入力 DC-DC (直流 – 直流) コンバータに対応したパルス幅変調 (PWM: Pulse Width Modulation) コントローラの TB6814FLG と, パワー素子を集積して 1 MHz 動作が可能なマルチチップモジュール (MCM: Multi Chip Module) の TB7003FL を開発した。両者を組み合わせることで, Cell Broadband Engine (CBE) に最適な, 高精度で高速応答が可能な小型・高効率電源システムを実現することができる。

■ YAMAGUCHI Daisuke

Toshiba has developed the TB6814FLG pulse width modulation (PWM) controller for 5 V input DC-DC converters and the TB7003FL multichip module (MCM) for installation in power devices operating at 1 MHz frequency. These technologies enable the optimal power supply system for Cell Broadband Engine to be constructed, securing high accuracy, rapid response, a compact structure, and high efficiency.

## 1 まえがき

近年のCPUは、数年前と比較し急速な処理能力向上を実現したが、同時に、消費電力の急激な上昇という問題を抱えている。 x86系 CPUを例にとると、当初は数 W 程度だった消費電力は年々増加し、最近では 100 W を超える製品も登場している。

高速処理を実現するためのクロックの高周波化は、消費電力の増大を招く。プロセスの微細化による動作電圧の低減は消費電力上昇を抑制するが、それ以上に高速処理が進む結果、CPUの消費電力は年々上昇している。消費電力の上昇はすなわち消費電流の上昇を意味し、動作電圧が低減することで更なる消費電流の増大を招く。

消費電力がまだ数Wであった時代は、CPUの放熱処理はファンを必要としていなかったが、その後の消費電力の急激な上昇によって、ファンを用いた放熱が必要とされるようになった。しかしながら、放熱処理を必要としなかった時代とは異なり、ファンの騒音が問題となり始め、放熱能力や静音性で有利な液冷システムを導入する例が増えていることからも、消費電力の上昇は深刻な問題となっている。

CPU処理を高速化するためのプロセス微細化による動作電圧の低減とクロック周波数の向上は、従来に比べ高精度で高速応答が可能な電源を必要とする。動作電圧の低減に伴い動作可能電圧範囲も狭まり、電源の出力電圧変動幅の抑制(高精度化)が重要となる。クロック周波数の向上は消費電流の変化率の向上を招き、その電流変化に追従可能な高速応答電源が必要となる。また、消費電力の増加により、小型・高効率な電源であることも重要な要素となっている。

このようなCPUやLSIの低電圧化,大電流化,及び高速化に伴い,電源の構成も従来の集中給電方式から分散給電方式へと変化している。

集中給電方式とは、CPUやLSIが必要とする電圧ごとに 電源を構成し、そこから同一電圧で動作する各素子へ電力 を供給する方式である。この構成は、電源から素子への 距離が長く、配線インピーダンスが大きくなる傾向にある。 配線インピーダンスの増加は電圧降下の増大を招き、素子へ 所定の電圧を供給できなくなるとともに、素子の動作による 電流変化に対する電流供給応答の悪化や、急激な電圧降下 を引き起こす。

CPUやLSIの低電圧化が進むと動作可能電圧範囲が狭くなり、配線による電圧降下の影響が無視できなくなる。更に、大電流化は電圧降下を増大させるとともに、電力損失の増大も招く。大電流化と高速化は負荷電流の急激な変化を引き起こし、集中給電方式では応答が困難となる。

前述の集中給電方式の欠点を改善するために,近年の CPUやLSI用の大電流電源は,負荷近傍に電源を分散配置 するPOL (Point Of Load)と呼ばれる分散給電方式が主流 となっている。

この方式では、負荷近傍に電源を分散配置することで配線インピーダンスの影響を低減し、精度の向上、負荷変動に対する電源の安定性の向上、及び高効率化を実現する。

また、大電流用途では、複数のDC-DCコンバータの位相をずらして並列配置するマルチフェーズ電源構成が一般的である。この構成は、等価的にスイッチング周波数<sup>(注1)</sup>を相数倍<sup>(注2)</sup>にすることで高速応答を実現するとともに、電流を分散することで熱の集中を抑えることが可能である。

CPUやLSIの進化に伴う消費電力の増加及び高速処理動作によって、従来の電源システム以上の精度、応答特性、効率を実現できる電源システムが求められている。

## 2 Cell電源システムの構成

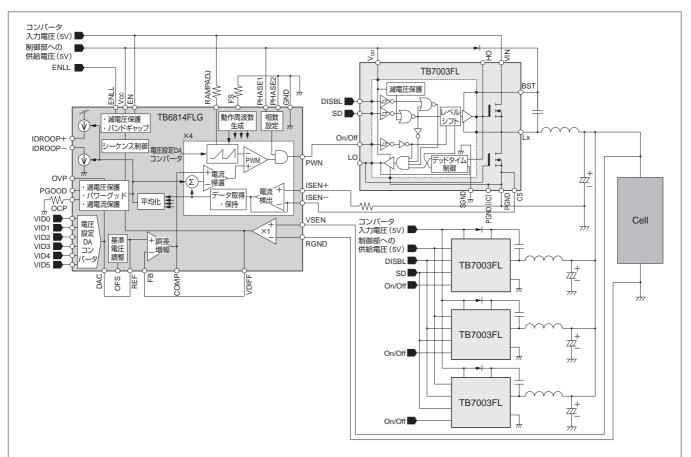

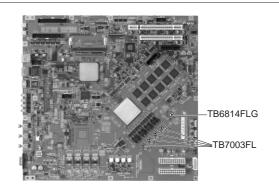

Cell 電源システムは、PWM コントローラの TB6814FLG (図1 (a)) 及び、MOSFET (金属酸化膜半導体型 電界効果トランジスタ) とそのドライバ IC を 1パッケージに集積した MCM の TB7003FL (図1 (b)) によって構成される。システムのブロック図を図2に示す。

TB6814FLGによって最大四つのTB7003FLを制御し、

- (注1) DC-DC コンバータを構成するスイッチング素子 (今回のシステム では MOSFET) がスイッチングを繰り返す周期のこと。電源を小型化するためにはスイッチング周波数を高めることが有効であり、負荷応答特性も向上する。

- (注2) マルチフェーズ電源は各相のスイッチングの位相をすらして動作させるため、見かけ上は相数倍の周波数で動作していることになる。例えば、1相当たりのスイッチング周波数が1 MHzで4相構成の場合は、4 MHzのスイッチング周波数に相当する。

**図1. TB6814FLGとTB7003FLの外観** – PWM コントローラのTB6814FLGとMCMのTB7003FLで電源システムを構成する。

External view of TB6814FLG PWM controller and TB7003FL multichip module

CBEの駆動に最適な電源を実現する。CBE用電源の重要な特性として、精度、高速応答、高効率が挙げられる。

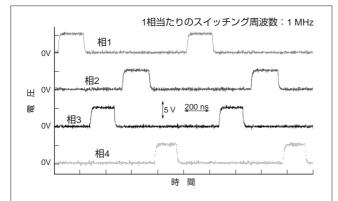

TB6814FLGは、高精度の基準電圧源、エラーアンプ、出力電圧検出機能、及び相ごとの電流検出機能によって、システムとしての高精度電圧出力を可能とする。また、1相当たりのスイッチング周波数が1MHzの4相構成マルチフェーズ電源とすることで、出力電圧の低リップル化と高速負荷応答を可能とする。4相動作時のPWM出力波形を図3に示す。

TB7003FLは、ドライバICとMOSFETを混載したMCM

**図2. Cell 電源システムのブロック図** - 1 個の TB6814FLG で4 個の TB7003FL を制御し、4 相構成のマルチフェーズ電源を構築する。 Block diagram of newly developed power supply system

特

図3. PWM 出力波形 – 各相の周期  $(1 \mu s)$  の 1/4 に相当する 250 ns ずつ位相をずらして PWM 信号を出力し、4相マルチフェーズ動作を実現する。 PWM output signal

である。ドライバICとMOSFET間の配線インピーダンスを 低減することによって、従来のディスクリート素子構成では実 現が困難であったスイッチング周波数1MHzの動作に対応 した。

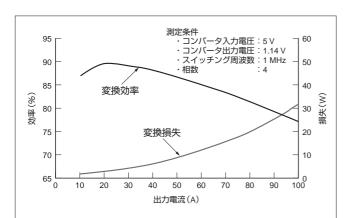

一般にスイッチング周波数の向上は、スイッチングロスの増加や制御電流の増加を招き、変換効率の低下につながる。しかしながら、TB6814FLGとTB7003FLは共に、従来の12V入力ではなく5V入力を基準に設計したこと、TB7003FLにおいては、ゲート電圧監視機能によるデッドタイムの最適化と低オン抵抗を実現したため、1MHzのスイッチング周波数における高効率動作を実現した。

#### 3 TB6814FLGの特長

TB6814FLGは4相PWMコントローラである。

従来のCPU用DC-DCコンバータは、12 Vの入力をCPUへの供給電圧 (コア電圧)まで降圧していたため、PWMコントローラは 12 V 専用が主流であった。今回開発したTB6814FLGは、コンバータ入力電圧に応じてPWMゲインを調整する機能 $^{(tz3)}$ を備えており、幅広い電圧に対応することを可能にした。Cell電源システムでは、コンバータ入力電圧を5 V とし変換損失の低減を図っている。

スイッチング周波数は外付け抵抗によって設定を行い、 $300\,\mathrm{kHz} \sim 3\,\mathrm{MHz}$ の範囲で動作可能である。また、PWM 出力は、相数設定端子 (PHASE1、PHASE2) の接続によって 2、3、4 相の切替えが可能である。

出力電圧の可変範囲は、プロセスの微細化に伴ったコア電圧の低下を見据え、0.6~1.3625 Vと従来のPWM コントローラより約0.2 V低下させている。この出力電圧の設定は

(注3) コンバータ入力電圧に応じて PWM 出力の分解能を最適化し, 高精 度制御を実現する。 6ビットの VID (電圧設定) コードを外部入力することで行い,動作中にコア電圧を変更することが可能である。

出力電圧の検出はゲイン1倍のアンプにより行うため、コア GND (グランド)とIC-GND が異なっていても、コア電圧を的確に検出する。

出力電流は相ごとに検出が可能であり、これによって相ごとの電流バランス制御、相ごとの過電流保護を実現する。また、相ごとの電流を加算することで、電源全体の電流が検出でき、電源全体の過電流保護も実現できる。電流検出は相ごとに搭載した電流検出アンプで行い、そのコモンモード電圧(注4)は1.5 Vまで対応しているため、各種の電流検出方式を採用することが可能である。電源全体の負荷電流に比例した電流を出力する端子を設け、その端子に接続した抵抗の電圧降下を利用し、負荷電流に応じて出力電圧を調整することでDroop(注5)制御を実現する。

また、コアを安全に動作させるため、前述の相ごと又は全相の過電流保護に加え、過電圧保護、過熱保護、TB6814FLGの制御電圧及びコンバータ入力電圧それぞれに減電圧保護、ソフトスタート、ソフトオフ、及びパワーグッドの機能を搭載している。

### 4 TB7003FLの特長

TB7003FLは、ハイサイドMOSFET、ローサイドMOSFET 及びMOSFET 駆動用ドライバICを、8 mm角の小型QFN (Quad Flat Nonlead) パッケージに集積したMCMである。PWMコントローラ、インダクタ、及び入出力コンデンサと組み合わせることで、同期整流型降圧DC-DCコンバータを構成する。

従来のディスクリート MOSFET 構成では、MOSFET とドライバIC 間の配線インピーダンスが障害となり、高い周波数による動作は困難であった。この TB7003FL は、ドライバIC と MOSFET を同一パッケージに集積することで、配線インピーダンスを低減し、1 MHz 動作を実現した。

1 MHzの動作周波数による高効率化のために,次のような施策を盛り込んでいる。

- (1) ドライバIC内部回路の高速動作を可能にする新規開発プロセスの採用

- (2) ドライバICに内蔵したゲート電圧監視回路によるデッド タイム<sup>(注6)</sup>の最適化

- (注4) 電流検出アンプの各端子(ISEN+, ISEN-)に入力される電圧差。 電流検出部の両端の電圧降下をアンプに入力することで電流値を 導き出す。入力電圧を1.5 Vまで対応可能とすることで、電流検出 箇所の自由度が増す。

- (注5) 負荷電流の増加に従い動作電圧が低下するように、ICの動作定格 電圧を設定すること。負荷の急変に伴う電圧変動の影響を吸収しや すくする。

Cell 電源システム 23

- (3) 低ゲート容量と低オン抵抗特性を持ち、DC-DCコンバータに最適な最新世代のパワーMOSFET搭載

- (4) パッケージ内配線の最適化による寄生インピーダンス の低減

- (5) パッケージ裏面の金属パッドによる放熱性の向上

素子1個当たりの出力電流は最大で30 Aであり、TB6814FLGによる4相構成とすることで、高精度で高速応答が可能な小型、高効率の120 A出力電源が実現可能である。電源システムの効率特性を**図4**に示す。

TB7003FLは、入力電圧 $5\sim12$  V程度のDC-DCコンバータを想定しているが、20 Vまでのより高い入力電圧に対応した製品の開発も進めている。

図4. 電源システムの変換効率 - このシステムにより、高効率な電源が 実現できる。

Conversion efficiency of newly developed power supply system

#### 5 あとがき

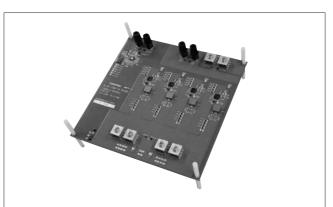

ここで述べたように、PWM コントローラの TB6814FLGと MCMの TB7003FL により、CBE に最適な、小型、高効率、高精度で、高速応答特性を備える電源システムを構築することができた。この電源システムは、Cell リファレンスセットに搭載されている。Cell リファレンスセットの基板を図5に示す。また、電源システム単独の評価ボードとして、4相のDC-DCコンバータセット(図6)を用意し、ユーザーの評価用に提供している。

今後は、アプリケーションに応じた多様な入力電圧に対応するためのラインアップを充実させていく。また、前記性能の更なる向上を実現する次世代製品の開発を進めるため、PWMコントローラの制御性能向上(内部回路の精度改善、

(注6) 降圧型同期整流回路は、コントロール側スイッチ(ハイサイドスイッチ)と同期側スイッチ(ローサイドスイッチ)を交互にスイッチングさせ、両者のオン時間の比率(デューティ)を調整することで設定電圧を出力する。オンしているスイッチング素子を切り替える際に両者ともオフしている期間をデッドタイムと称する。

図5. Cell リファレンスセットの基板 - CBE 評価用のリファレンスセットの電源部は、この Cell 電源システムで構成されている。

Cell reference set board

図 6. 電源システムの評価ボード – TB6814FLGと TB7003FLを搭載した4相の DC-DC コンバータセットを作製し、ユーザーの評価用に提供している。

Evaluation board for newly developed power supply system

内部動作周波数向上), MCM内蔵素子の世代更新(高速動作ドライバIC, 低損失 MOSFET), 及びMCM内部構造の改善(低配線インピーダンス, 高放熱)などを検討していく。

#### 武井 洋 TAKEI Hiroshi

セミコンダクター社 ディスクリート半導体事業部 パワー 半導体応用技術部主務。パワー半導体の商品企画・開発に 従事。電気学会会員。

Discrete Semiconductor Div.

### 武本 昭彦 TAKEMOTO Akihiko

セミコンダクター社 システム LSI 第二事業部 アナログパワーシステム LSI 技術部主務。電源 IC の商品企画・開発に従事。

System LSI Div. II

# 山口 大介 YAMAGUCHI Daisuke

東芝情報システム(株)第一LSIソリューション事業部 第二 LSI設計センター。電源ICの商品企画・開発に従事。

Toshiba Information Systems (Japan) Corp.