# Thin & Light PC の基板小型化技術

Printed Wiring Board Technologies for Thin and Light PCs

古賀 裕一 八甫谷 明彦 山本 展大

■ KOGA Yuichi

■ HAPPOYA Akihiko

■ YAMAMOTO Nobuhiro

Thin & Light PC では、薄く軽くという仕様を実現するため基板面積の小型化が必須である。数年前の同一カテゴリの製品と比較しても、チップセットの大型化や放熱機構追加など新規要素が追加されており、基板内の実装スペースは小型化の一途をたどっている。

東芝は、このようなニーズに対応した低損失スタックビアプリント配線板、狭小部品、及びBGA (Ball Grid Array) 重ね実装を実現した高密度部品実装技術を開発し、今回発表した dynabook SS SX/190 と libretto U100 に採用した。その基板面積は従来機種の 70 %未満となっている。

In the field of thin and light PCs, minimization of the printed wiring board (PWB) area is indispensable. Even when products are compared with those in the same category from several years ago, new elements such as enlarged chip sets and the addition of a cooling mechanism are now being incorporated in PWBs while reduction of the mounting space is progressing.

Toshiba has developed a high-density parts mounting technology that realizes a low loss stack via PWB and narrow part, as well as a ball grid array (BGA) table reverse side mounting technology. These technologies have been adopted in the dynabook SS SX/190 and libretto U100 notebook PCs. The PWB area in these models is less than 70 % that in conventional models.

## 1 まえがき

Thin & Light PC "dynabook SS SX/190"と"libretto U100" には,高密度実装技術が生かされた小型基板が搭載されている。これは,配線幅を縮小し配線密度向上を達成した低損失スタックビアプリント配線板技術と,部品配置間隔の縮小及びBGA (Ball Grid Array) 重ね実装を実現した高密度部品実装技術から構成される。

ここでは、これらの技術について述べる。

## 2 ノートPC基板に求められる仕様について

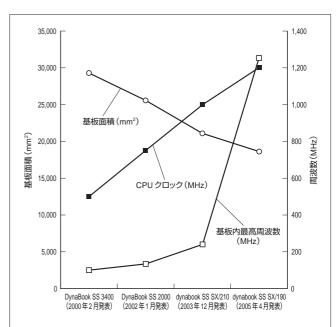

Thin & Light PCでは小型の筐体(きょうたい)に収めるために、その基板は小型化の一途をたどっている。図1は、Thin & Light PCのB5サイズにおける基板仕様の、2000年から2005年に至るまでの変遷である。2000年2月に発表したDynaBook SS3400シリーズと2005年4月に発表したdynabook SS SX/190を比較すると、dynabook SS SX/190は30%の面積を削減している。面積削減により空いたスペースは、放熱機構の実装やバッテリー容量の増加などに活用できるため、より魅力ある製品仕様が可能となる。

今回,開発した低損失スタックビアプリント配線板は,配線幅及び配線間隔を従来比で20%削減し,層間接続用ビアサイズも20%縮小した。これらの新規技術採用により配線

図1. B5 サイズノートPC の基板仕様変遷 — 基板面積は減少し、基板内周波数は増加の一途をたどっている。

Changes in specifications of PWBs for B5-size notebook PCs

密度を向上させることに成功し、前述のとおり30%の基板 面積削減を達成した。

また,絶縁層材料を見直すことで高周波帯域における伝送損失を改善し,配線微細化による伝送特性の悪化を抑え

ることにも成功した。結果としてPCI-Expressチップセットの採用による基板内伝送スピード2.5 Gビット/s を実現している。

# 3 dynabook SS SX/190とlibretto U100の 基板実装仕様

表1は、dynabook SS SX/190及びlibretto U100の基板 仕様についてまとめたものである。配線やビアの微細化により配線密度だけでなく部品密度も向上し、従来の部品間隔が0.25 mmであるのに対し、0.20 mmまでの狭間隔化を達成した。libretto U100については、製品をA5用紙サイズに収めるためにBGA 重ね実装を実現し、従来使用していた1.0×0.5 mm (1005) サイズのチップ部品に加え  $0.6 \times 0.3$  mm (0603) サイズのチップ部品も採用し、小型化に貢献した。

#### 表 1. dynabook SS SX/190 と libretto U100 の基板仕様の比較 PWB comparison of dynabook SS SX/190 and libretto U100

| 項目          | dynabook SS SX/190                       | libretto U100             |

|-------------|------------------------------------------|---------------------------|

| プリント配線板     | 低損失スタックビア                                |                           |

| 配線層数(層)     | 10                                       |                           |

| 配線幅/間隔(µm)  | 75/100                                   |                           |

| 基板サイズ (mm)  | 180 × 84                                 | 160 × 100                 |

| 製品サイズ (mm)  | 286 × 229                                | 210 × 165                 |

| チップセット      | Intel <sup>®(注1)</sup><br>915GMS Express | Intel <sup>®</sup> 855GME |

| 最小チップ       | 1005                                     | 0603                      |

| 部品間隔 (mm)   | 0.2                                      | 0.2                       |

| 部品総ピン数      | 8,310                                    | 6,017                     |

| 最高周波数 (MHz) | 1,250                                    | 240                       |

| その他         | PCI-Express 採用                           | BGA重ね実装採用                 |

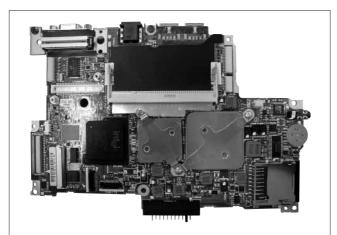

**図 2**. **dynabook SS SX/190のメイン基板** — PCI-Express 採用の チップセットが横一列に並んだ高密度実装である。

Main board of dynabook SS SX/190

(注1) Intelは、米国又はその他の国における米国 Intel Corporation 又は 子会社の登録商標又は商標。

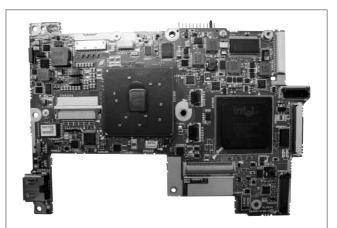

図3. libretto U100のメイン基板 — 製品サイズを A5用紙並みに抑えるため、メイン基板は dynabook SS SX/190の70%まで削減されている。 Main board of libretto U100

dynabook SS SX/190のメイン基板を**図2**に, libretto U100のメイン基板を**図3**に示す。

## 4 低損失スタックビアプリント配線板

dynabook SS SX/190, libretto U100に採用したプリント 配線板は、高速伝送に対応した低損失材料を採用しており、 高密度配線が可能なスタックビア構造を業界で初めて採用 している。また、環境対応技術も積極的に採り入れている。

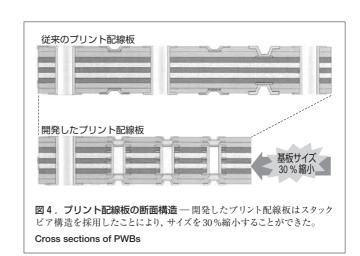

#### 4.1 高密度技術

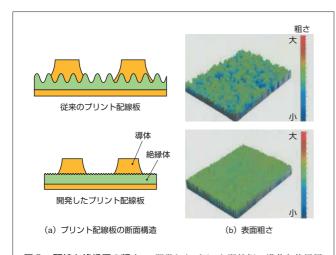

従来の Thin & Light PCには、**図4**上に示す1~3層 スキップビア構造ビルドアッププリント配線板を採用していた。dynabook SS SX/190, libretto U100では、図4下に示すような、よりいっそうの高密度設計が可能な、スタックビア構造ビルドアッププリント配線板を採用した。この構造は、レーザで加工した穴に銅メッキを充填(じゅうてん)することにより、ビア上にビアを重ねることができ、配線の自由度が非常に高い特長を持っている。

#### 4.2 高速対応技術

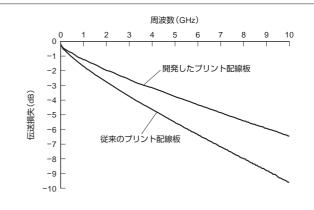

信号の周波数が高速化し、GHz帯になると信号伝送の損失が無視できなくなり、伝送損失をいかに少なくするかということが高速伝送の重要なポイントとなる。伝送損失には抵抗損失や誘電損失などがある。細い配線ほど断面積が小さくなり、抵抗値が高くなるので、高密度化した設計ほど抵抗損失が大きくなる傾向がある。また、使用する周波数が高くなるほど誘電損失が支配的である。誘電損失を小さくするには、プリント配線板材料の誘電率と誘電正接を低くすることが必要となる。今回採用した材料は、従来採用していた材料よりも低誘電率と低誘電正接になっている。

プリント配線板の導体は銅箔(はく)であり、絶縁層との密着性を確保するために密着面が荒れた形状になっている(図5上)。信号の周波数が高くなるほど、導体の表面に電流が集中する表皮効果が大きくなり、この荒れた形状が伝送損失を大きくしている。今回採用したプリント配線板の銅箔と絶縁層の粗さは、従来のものに比べ非常に小さいロープロファイル銅箔を使っており、伝送損失を小さく抑えることができる(図5下)。

また、銅箔と絶縁層の粗さを小さくすると、配線を形成するときに行うエッチングが容易にでき、パターン幅の仕上がり精度が向上する。パターン幅の精度が向上すれば、特性・差動インピーダンスの精度も良くなり、安定した高速伝送が可能となる。低誘電率、低誘電正接、及びロープロファイル銅箔を用いることにより、図6に示すように伝送特性が従来品より向上しており、高速伝送において低損失という特長を持っている。

#### 4.3 環境対応技術

東芝は、1998年11月に世界で初めて、焼却時にダイオキシンや臭化水素の発生を抑えたハロゲンフリー多層プリント配線

図5. 配線と絶縁層の粗さ ― 開発したプリント配線板の導体と絶縁層の密着面粗さは、従来のプリント配線板に比べ非常に小さく、伝送損失を小さく抑えることができる。

Profile between conductor and dielectric layer

図 6. 高速伝送特性 — 低誘電率, 低誘電正接, 及びロープロファイル 銅箔を用いることにより高速伝送特性が向上している。

High-speed transmission characteristics

板の量産化に成功し、ノートPC DynaBook Satellite2510に採用した。dynabook SS SX/190とlibretto U100のプリント配線板にもハロゲンフリー材を採用している。また、環境にとって有害な鉛を用いない、すずー銀ー銅系の鉛フリーはんだを2001年2月から採用をしている。2005年1月からは、RoHS (Restriction on Hazardous Substances) 指令で指定されている鉛、水銀、カドミウム、六価クロム、特定臭素系難燃剤 (PBB (PolyBrominated Biphenyls), PBDE (PolyBrominated Diphenyl Ethers))の、6種類の有害物質を含まない基板を採用したノートPCを出荷している。

## 5 高密度部品実装技術

libretto U100では,以下の技術を開発採用することにより, dynabook SS SX/190と比べて30%の基板面積縮小を達成 した。

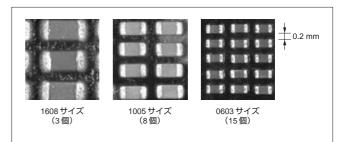

- (1) 0603 サイズのチップ部品(図7)

- (2) BGA 重ね実装

#### 5.1 0603 サイズのチップ部品

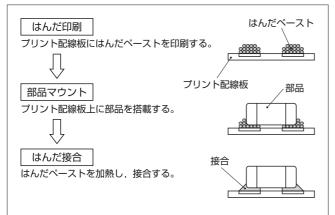

一般に電子機器へ内蔵される基板は、図8に示すように表面実装工程で製造される。0603サイズのチップ部品にお

**図7. 同一面積に実装できる部品数の比較** — 基板面積 (2.6 × 2.8 mm) に実装できる部品の数を比較している。0603 チップ実装可能数は 1608 チップの 5 倍以上である。

Comparison of number of parts mountable on same area

図8.表面実装工程 — はんだ印刷, 部品マウント, 及びはんだ接合により, プリント配線板に部品をはんだ付けして基板を製造する。

Surface mounting process

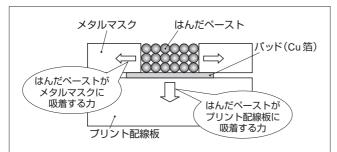

図9. はんだペーストの印刷メカニズム — はんだペーストは金属粒と 粘性のある活性剤の混合物であり、それ自体の粘度が高いためメタル マスクやプリント配線板に対して吸着力が働く。

Solder paste printing mechanism

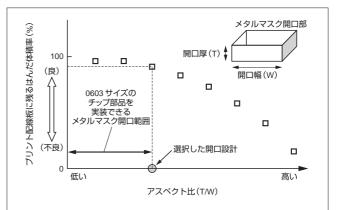

いて特に重要となるのは、はんだ印刷の工程である。はんだ印刷には、メタルマスクとプリント配線板を離す際に、**図9**に示すようにメタルマスクやプリント配線板に対して吸着力が働く。はんだ印刷の安定のためには、メタルマスクの開口厚と開口幅の比であるアスペクト比を調整しなければならない。アスペクト比が高くなると、はんだペーストがメタルマスクに吸着する力が大きくなるため、基板上にはんだペーストが残らない。そのためlibretto U100では、**図10**に示すように、アスペクト比と印刷の関係について基礎評価を重ね、最適な開口設計を採用している。

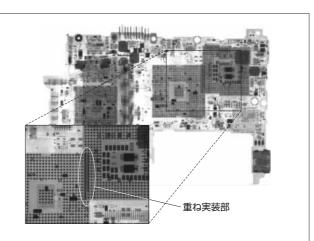

### 5.2 BGA 重ね実装

BGA 重ね比率は,基板の電気特性や生産性を考慮して決定する必要がある。libretto U100は,評価結果からBGA 重ね比率を約15%とした(**図11**)。

# 6 あとがき

Thin & Light PCに採用している高密度・高速基板技術について説明した。PC設計は、性能向上による基板内伝送路の高速化が見込まれる。また、差異化技術の実装による

図10. アスペクト比とはんだ印刷量の関係 — 高密度基板では、すべての表面実装部品について、製造性とはんだ量の観点から最適なメタルマスクの開口設計を行う。

Relationship between aspect ratio and solder print

図11. BGA 重ね配置の X 線写真 — libretto U100 に採用されている BGA 重ね実装を示している。

Radiograph of BGA piling arrangement

基板面積の減少も考えられる。

今後もこれら技術課題を克服し,魅力ある製品つくりに 貢献していきたい。

古賀 裕一 KOGA Yuichi

PC&ネットワーク社 PC開発センター PC設計第一部主務。 PCのハードウエア開発に従事。

PC Development Center

#### 八甫谷 明彦 HAPPOYA Akihiko

PC&ネットワーク社 PC開発センター 実装開発センター グループ長。PCのプリント配線板・実装開発に従事。エレクトロニクス実装学会会員。

PC Development Center

#### 山本 展大 YAMAMOTO Nobuhiro

PC&ネットワーク社 PC 開発センター 実装開発センター。 PCの実装開発に従事。

PC Development Center