# 高性能配線技術

**Advanced BEOL Technology**

依田 孝 蓮沼 正彦 宮島 秀史

YODA Takashi

■ HASUNUMA Masahiko

■ MIYAJIMA Hideshi

高性能配線技術の分野では、130 nm 世代より配線材料がアルミニウム (AI) から銅 (Cu) へと大きな変革を遂げた。引き続き、90 nm 世代より本格的に低誘電率膜 (Low-k 膜) が採用され始め、その後 Low-k 膜は世代ごとに変化していく。更なる誘電率低減のためには、膜密度を下げたポーラス膜 (多孔質の膜) が必要とされる。ポーラス膜は、膜自身の機械的強度が下がり、かつ異種膜界面での密着性も大幅に低下する。これらの膜を用いてプロセスを組み上げることは、非常に困難になっている。

東芝は、このようなニーズに応えるために、Cu配線とLow-k 膜を主体とする配線技術開発において、微細化プロセスにて常に最先端を走り、かつロバストなプロセス開発を手がけてきた。90 nm/65 nm/45 nm 世代配線プロセスの層間絶縁膜の積層構造、微細 RIE (Reactive Ion Etching) 加工技術、機械的強度向上化施策を中心に独自の技術を開発し高性能微細化配線を実現している。

In recent years, great progress has been achieved in back end of line (BEOL) process development since the advent of the 130 nm technology node. This progress includes changing the wiring material from Al to Cu, and the dielectric material from the traditional silicon dioxide  $(SiO_2)$  to low-dielectric-constant (low-k) materials. Moreover, a high-performance BEOL process requires a porous material. However, porous low-k material degrades the mechanical strength of the film and the interfacial adhesion of films.

To meet the above requirement, Toshiba has developed the leading-edge technology in the Cu/low-k BEOL process. This advanced BEOL process technology centers around the stacked dielectric structure, the reactive ion etching (RIE) process, and improvement of the mechanical strength of the film.

## 1 まえがき

130 nm世代の高速ロジックデバイス以降, LSIチップの多層配線工程には世代ごとに新材料が用いられるようになってきた。配線材料としては, 130 nm世代から前世代までの Al に代わり Cu が採用され始め, 更に層間絶縁膜として 90 nm世代から初めて比誘電率 (k) 3.0 以下の低誘電率膜 (Low-k膜) が用いられてきた。層間絶縁膜の低誘電率化はその後も進み, 65 nm世代以降には, 絶縁膜中に微細な空孔を持つk=2.5 以下の膜が必要となる。こうした材料の変革とあいまって, Cu 配線導入に伴い配線構造も, 従来のメタル RIE (Reactive Ion Etching) 加工からダマシン構造と呼ばれる溝埋込み配線構造へと変革してきた。

多層配線技術は、デバイス性能としてULSIチップの高速 化のボトルネックとなるだけでなく、製造工程においても、全 工程数に占める配線工程数の割合は年々増大しており、コス ト削減が最重要課題となる。更に、歩留まりのドラスティック な改善と高い信頼性で圧倒的な優位に立つことが急務とさ れている。

90 nm 世代以降の配線技術のいちばんの特徴は、新たな

Low-k膜の採用である。ここでは、新Low-k膜導入に伴い開発された東芝独自の層間絶縁膜の積層構造、微細RIE加工技術、機械的強度向上化施策を中心に配線モジュールプロセス技術について述べる。

#### 2 現状技術 (90 nm/65 nm 世代の配線技術)<sup>(1)-(5)</sup>

#### 2.1 層間絶縁膜構造

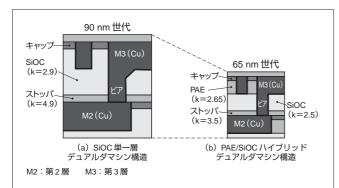

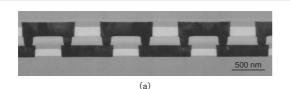

90 nm, 65 nm 世代の微細配線層の断面構造を**図1**に示す。 90 nm 世代では微細配線層のLow-k 膜として k = 2.9 の PE-CVD (Plasma Enhanced - Chemical Vapor Deposition) 炭素添加シリコン酸化膜(SiOC 膜)を単一層構造で採用した。 また, k = 4.9 の PE-CVD 窒素添加シリコンカーバイト(SiCN) 膜をLow-k 膜 RIE 時のエッチングストッパ膜として用い, Cuの熱及び電界拡散バリア,更に Cu 腐食防止としての機能 も持たせた。更に,Low-k 膜表層にはキャップ層として PE-CVD シリコン酸化膜 (SiO<sub>2</sub>膜) を形成し,CMP (Chemical Mechanical Polishing) やプラズマ処理時のLow-k ダメージ を回避している。

なお, 前記構造はコストの点からデュアルダマシンプロセス

図1.90 nm, 65 nm 世代における多層配線構造の概略 — 90 nm 世代では層間絶縁膜構造として単一層構造を,65 nm 世代では三種類の Low-k 膜を積層した構造を採用。

Schematic diagram of multilayered interconnection structure in 90 nm and 65 nm node generations

#### にて実現した。

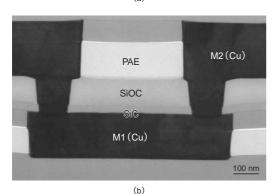

一方、 $65\,\mathrm{nm}$ 世代では、 $\mathrm{Low-k}$ 層を積層構造 (ハイブリッド構造) に変更し、配線間絶縁膜に  $\mathrm{SOD-PAE}$  (Spin On Dielectric-Poly Arylene Ether) ( $\mathrm{k}=2.65$ ) 膜及びビアホール (層間配線接続部) 層絶縁膜に PE-CVD SiOC ( $\mathrm{k}=2.5$ ) 膜を用いて RIE 加工時の選択比を持たせたことが特徴である。ハイブリッド構造を採用した理由は、RIE 形状の向上と安定性を上げられることである。こうして高精度の形状制御が可能となったことにより  $\mathrm{Cu}$  埋込み性が改善された。エッチングストッパ膜は前世代に比べ更に誘電率を低減させたPE-CVD SiCN ( $\mathrm{k}=3.5$ ) を用い、キャップ層も前世代同様に適用した。

#### 2.2 デュアルダマシン形成プロセス

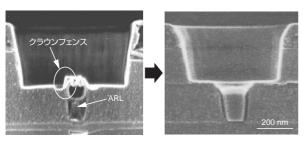

90 nm 世代ではデュアルダマシン形成方式として,合わせずれに強いビア先プロセスを開発した。従来の塗布による反射防止膜を用いて加工した場合,反射防止膜とレジストとの選択比がとれないことからトレンチ RIE の際にビアホール開孔部にクラウンフェンスと呼ばれる残渣(ざんさ)が発生

(a) 従来のレジストプロセスによる加工

(b) S-MAPによる加工

ARL: Anti-Reflective Layer

図2. 断面走査型電子顕微鏡 (SEM) による加工形状の比較 — 従来のレジストプロセスでの加工形状に比べ、S-MAP プロセスを採用することにより、スムーズなビア形状を得ることが可能となる。

Comparison of via shape after dry etching process

した(図2(a))。これに対し、3層の多層マスク構造(トップレジスト/SOG(Spin On Glass)/ボトムレジスト)を利用したS-MAP(Stacked MAsk Process)プロセスを用いることによりクラウンフェンスの形成を抑止し、良好な形状を得ることが可能となった(図2(b))。

また、RIE後のレジスト除去プロセスに関して、従来の $O_2$ (酸素)プラズマに代わり、 $H_2O(水)$ プラズマを用いることにより、レジスト除去時のダメージ層形成を抑制し、配線間リークや配線の断線などの信頼性問題の改善を図った。

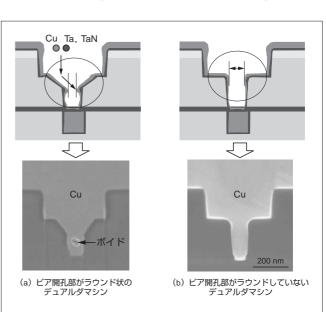

65 nm 世代ではハイブリッド構造の形成に際して、新たにトリプルハードマスクを用いた加工プロセスを開発した。レジストマスクによる加工方法では、マスクの除去工程で有機成分を持つLow-k 膜がダメージを受け、誘電率の増大や吸湿による配線信頼性の劣化を引き起こしてしまう。また、図3(a)に示すようにビアホールの肩部の形状がラウンド状に加工されるためバリアメタル(タンタル(Ta)、窒化タンタル(TaN))とCuシードのスパッタ成膜の際に、ひさし状にメタルが形成されCuメッキ工程において埋込み不良の原因となる。

ハイブリッド構造とトリプルハードマスク加工の導入により、図3(b)に示すようなスパッタ成膜に有利なRIE加工形状が安定して形成されることになり、ボイドのないCu埋込み配線を実現することが可能となった。

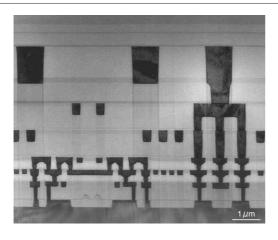

図4,図5は前述の技術に加えメタル成膜技術,更にCMPプロセス技術を用いて形成した90nm世代6層Cu配線及び65nm世代のハイブリッド構造による二層ビアチェイン配線部の断面を示したものである。ともにボイドフリーの良好な配線形状を示すが、ハイブリッド構造は配線形状,特にビア

図3. Cu 埋込み特性を比較した断面 SEM ― ビア加工形状はその後の Cu 埋込み特性に大きな影響を及ぼす。ビア開孔部のラウンドをなくすことにより、埋込み性は向上する。

Comparison of via shape for different Cu filling characteristics

図 4 . 90 nm 世代の 6 層 Cu 配線断面構造 — M2-M3 の層間絶縁膜に SiOC (k=2.9) を M4-M5 に FSG (Fluorinated Silicate Glass) (k=3.4) を 導入。

Cross-sectional structure of six levels of Cu/low-k interconnection in 90 nm node generation

図 5 . 65 nm 世代の二層配線の断面構造 — 無機系 Low-k 膜と有機系 Low-k 膜を積層したハイブリッド構造の  $0.1~\mu m$  ハーフピッチ二層配線である ((b) は拡大図) 。

Cross-sectional structure of two-level interconnection in  $65\ \mathrm{nm}$  node generation

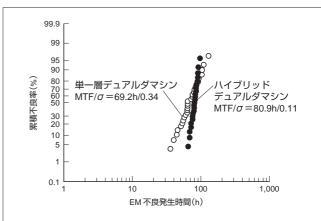

部の肩落ちが大幅に改善された結果、歩留まり及びEM (ElectroMigration)、SIV (Stress Induced Voiding)といった配線信頼性の向上も顕著に発現された。図 6 は一例として配線EM試験結果を示したものである。単一層構造の寿命ばらつきが $0.34\sigma$ に比べハイブリッド構造の寿命ばらつきが $0.11\sigma$ と極めて小さいことが特長であり、MTF (Mean Time to Failure)も前者の69.2 hに比べ後者は80.9 h と向上した。このばらつきの低減及びMTFの向上は、ハイブリッド構造

図 6. EM 不良発生度合いの多層配線構造依存性 — ハイブリッド構造 は単一層構造の EM 信頼性結果に比べ寿命のばらつきが小さくなること が大きな特長である。

Electromigration (EM) cumulative failure distribution of homogeneous-dual damascene (DD) and hybrid-DD Cu lines

ではビア形状のウェーハ面内均一性,ウェーハ間再現性が高くなることにより,短寿命となる不良ビア形状が減少することによる効果と考える。

### 3 将来技術 (45 nm 世代)<sup>6</sup>

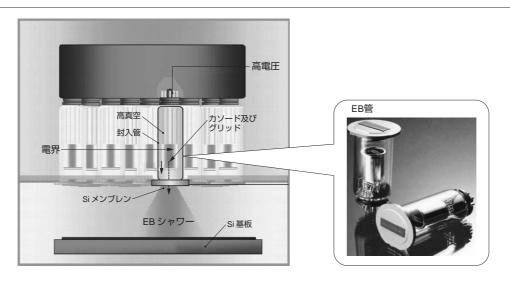

今後45 nm 世代以降では、デバイス動作速度の更なる高速化のため層間絶縁膜にはk = 2.2以下の膜が必要となる。この低誘電率化は、誘電分極率及び膜密度を下げることにより実現される。このように45 nm 世代以降はポーラス膜の適用が本格化されるため、機械的強度及び異種膜界面の密着強度が急激に劣化する。この問題を解決する手段の一つが、電子ビーム(EB)照射によるLow-k膜の改質(EB キュアプロセス)である。図7に装置の概念を示す。

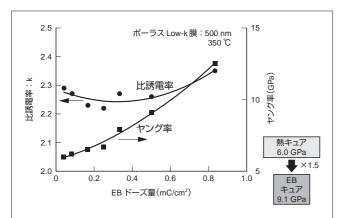

特に塗布膜系のLow-k 膜へEBキュアプロセスを適用する場合には、膜強度を向上させるだけでなく熱キュア温度及び時間を大幅に低減することが可能となり、低コストプロセスとしても注目されている。図8にEBドーズ量に対する比誘電率及びヤング率の変化を示す。熱キュアの場合 6.0 GPaのヤング率が約1.5倍の9.1 GPaに向上しているのがわかる。しかも比誘電率はほとんど上昇しないというメリットがある。密着性に関しても4点曲げ試験による界面密着強度測定の結果、熱キュアに比べ1.6倍の密着強度が得られた。また、このときのEBキュア時間は約3 min であり、従来の熱キュアでは350 ℃で60 min 必要なのに対し1/20 の時間短縮効果となる

以上のようにEBキュアプロセスは比誘電率の劣化を招かずに機械的強度の向上が図れ、更に短TAT (Turn Around Time) 化が可能な技術であり、45 nm世代以降の必須技術になると考える。

高性能配線技術 19

**図7**. **EBキュア装置の概略** — EB管を多数本併設してEBシャワーを均一化し, 照射窓にはSiメンブレンを採用している。 Schematic diagram of electron beam (EB) cure system

**図8. EB キュアによる Low-k 改質効果** — 0.5 mC/cm<sup>2</sup>の EB 照射により、比誘電率は上昇することなく、Low-k 膜のヤング率が熱キュアの 1.5 倍に向上している。

Dielectric constant and Young's modulus as function of total dose

## 4 要素技術開発 (7), (8)

EB キュアプロセスのように材料自体の高強度化を図るプロセス開発にとって,必要とされる強度の指標を定量的に得る技術,また,破壊を招く応力自体を構造の最適化により低減する技術が今後ますます必要とされる。

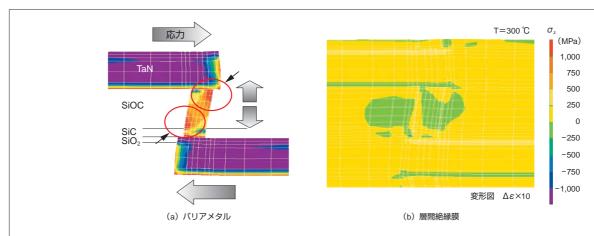

多層配線構造にはプロセス中の温度の上げ下げに伴う 熱応力, CMP時の剪断(せんだん)応力, 更にはプロービング, ボンディングなどをはじめとする検査, 後工程時に多種多様 な力が掛かる。これを回避するためのストレス設計技術が 重要である。

ストレス設計技術とは,第1段階は,多層配線構造の応力 状態を計算する"応力集中予測技術"と,材料や界面の壊れ る状態を実測する"破壊クライテリア測定技術"を融合させることにより、多層配線の破壊の危険性を定量的に予測することを目指す技術である。更に第2段階では、破壊の危険性を回避するために応力集中の低減又は破壊のクライテリアを上げるための施策を検討する必要がある。具体的には①最適な多層配線構造、②外部応力の低減化、③材料又はプロセス改善などを定量的に提案し、信頼性の高い多層配線を形成する技術である。なお、このような施策は開発初期に行うことにより、プロセスに対する過度なスペック要求の回避、開発の短TAT化を可能にすることができる。以下に多層配線に掛かる熱応力の実例を用いて簡単に示す。

図9は多層配線部に300℃の温度を加えたときのビアホール周辺の熱応力計算結果である。多層配線各部位の応力状態を調べると、多層配線中でもっとも大きな熱応力が掛かるのは、ビアホールのバリアメタルとなる。その中でもビア上部と下部(図9中の赤丸部)に集中する。この応力集中を引き起こす原因は、材料間の線膨張係数差と配線バリアメタルが持つ3GPaにも及ぶ圧縮の内部応力である。ビアホール部のバリアメタルは、低誘電率の層間絶縁膜とCuにより縦に引っ張られる力と配線のバリアメタルの圧縮応力により変形させられるために大きな応力が働く。ビアホール部バリアメタルに掛かる応力に及ぼす低誘電率の層間絶縁膜のヤング率と線膨張係数の影響を計算した結果、10GPaを切るような低ヤング率材料になるとヤング率よりも線膨張係数の影響が大きくなることから、材料の開発や選択においては線膨張係数の低い材料が望ましいことが判明した。

一方,破壊のクライテリアの測定は実際の二層配線構造を 用いた熱による加速実験で行った。その結果,現在の物理 蒸着で成膜した Ta/TaN のバリアメタルは450 ℃まで加熱し

図9. ビア部熱応力集中部位 — ヤング率が小さく、線膨張係数の大きいLow-k 膜を用いると、ビア部のバリアメタルに熱応力が集中する。 Result of thermal stress simulation in vicinity of via

ても破壊は生じない。なお、このときの応力値は計算の結果 2GPaに相当する。以上の結果から、ビアホール部の安全性 が現在のバリアメタル構造で確認されるとともに次世代の材 料開発の方向性も明らかとなった。しかし、バリアメタルは 熱応力による危険部位として今後も継続して着目しなくては ならない部位である。

## 5 あとがき

90 nm世代以降の配線技術に関して,新Low-k 膜導入に伴う層間絶縁膜の積層構造,微細 RIE 加工技術,機械的強度向上化施策を中心に述べてきた。微細化対応の高精度,高信頼性デュアルダマシン形成プロセスは,90 nm/65 nm世代で確立することができた。45 nm世代以降で威力を発揮する当社独自の差異化技術は,EBキュアプロセスによる材料高強度化技術,及びストレス設計技術である。これらの技術を駆使することにより,高性能微細化配線プロセス技術において,常に最先端を走り,かつロバストなプロセス実現が可能となってきている。

## 文 献

- Inohara, M., et al. High Performance Copper and Low-k Interconnect Technology Fully Compatible to 90 nm-node SOC application (CMOS4) International Electron Devices Meeting. Technical Digest. 2002, p.77 80.

- (2) Higashi, K., et al. A Manufacturable Copper/Low-k SiOC/SiCN Process Technology for 90 nm-node High Performance eDRAM. Proceeding of the IEEE 2002 International Interconnect Technology Conference. p.15 17.

- (3) Kajita, A., et al. Highly Reliable Cu/low-k Dual-Damascene Interconnect Technology with Hybrid( PAE/SiOC )Dielectrics for 65 nm-node High Performance eDRAM. Proceeding of the IEEE 2003 International Interconnect Technology Conference, p.9 11.

- (4) Kanamura, R., et al. Integration of Cu/low-k dual-damascene interconnects with a porous PAE/SiOC hybrid structure for 65 nm-node high performance eDRAM. 2003 Symposium of VLSI Technology. p.107 - 108.

- (5) 山田誠司,ほか.快走する東芝・ソニーのDRAM混載65 nm後は信頼性確認と歩留まり向上.日経マイクロデバイス.2003-07,p.79-90.

- (6) Fujita, K., et al. Notable Improvement in Porous Low-k film Properties using Electro-Beam Cure method. Proceeding of the IEEE 2003 International Interconnect Technology Conference. 2003, p. 106 - 108.

- (7) 蓮沼正彦 . Stress Engineering of Multi-Level Interconnection Module with Copper and Low-k Dielectric . 第64回半導体集積回路シンポジウム予稿集 . 2003 . p.58 - 61 .

- (8) 伊藤祥代,ほか、Cu/Low-k構造におけるパッドへの外部応力印加時の 応力集中、第9回LSI配線における原子輸送応力問題研究会予稿集、 2003-10,p.10-11.

#### 依田 孝 YODA Takashi

セミコンダクター社 プロセス技術推進センター 半導体プロセス開発第五部長。多層配線プロセスの技術開発に従事。 応用物理学会会員。

Process & Manufacturing Engineering Center

### 蓮沼 正彦 HASUNUMA Masahiko

セミコンダクター社 プロセス技術推進センター 半導体プロセス開発第五部主査。多層配線プロセスの技術開発に従事。 Process & Manufacturing Engineering Center

#### 宮島 秀史 MIYAJIMA Hideshi

セミコンダクター社 プロセス技術推進センター 半導体プロセス開発第五部主務。多層配線プロセスの技術開発に従事。 Process & Manufacturing Engineering Center

高性能配線技術 21