世界を手のひらに,明日をエンジョイする携帯電話

# 2. 省工ネ最前線

ますます多様な機能が搭載されながら進化していく 携帯電話では,使用時間を長く保つために省エネルギー(以下,省エネと略記)設計が重要です。今回は, 携帯電話の設計においてどのような省エネ努力がなさ れてきたのかを紹介します。

#### 携帯電話の省エネ技術

携帯電話は小型・軽量を保ちつつ使用時間を延ばすために,省エネ努力が注がれてきました。

省工ネの度合いを測るために、電池容量と通話時間、待受け時間の関係を用いることがあります。デジタル携帯電話が市場に出始めたころ、730 mAhの電池で待受け時間が50時間程度でしたから、待受け中に消費する電流値は15 mA程度でした。現在では、600 mAhの電池で300時間程度の待受け時間ですから、待受け中に消費する電流値は2mA程度に減りました(図1)。

この間,携帯電話に詰め込まれてきた省エネ設計は,部品や回路の動作電圧を下げて消費電力を下げようとする低電圧化と,部品や回路の不要期間の動作を小まめに停止させて消費電力を下げようとする動作停止とに大別できます。

### 低電圧化

低電圧化という面での省エネ設計としては、携帯電話に搭載するLSIへの供給電圧を低くすることで、LSIで消費する電力を小さくし低消費電力化を図る方法があります。

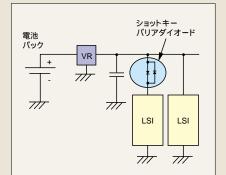

携帯電話の初期のころは,LSIへの供給電圧を下げるため,ボルテージレギュレータ(以下,VRと略記)の出力電圧をショットキーバリアダイオードでいったん落とし電源を供

図1.PDC端末諸元推移 - PDC(Personal Digital Cellular)方式デジタル携帯電話の省エネ努力は、電池容量と待受け時間、通話時間で読み取ることができます。

給しました。ショットキーバリアダイオードを挿入しなくても、VR自体の電圧を下げればよいと考えられますが、電圧を下げることが可能なLSIとそうでないLSIがあり、それぞれに対応した電源系を構成すると、電源システムが複雑になってしまうというデメリットから、ショットキーバリアダイオードを挿入する方法で低電圧化を実施しました(図2)

また、LSIへの供給電圧を下げることのもう一つの目的は、受信性能を劣化させる原因となる、高速で動作するLSIの動作クロックの高調波スペクトラムを小さくすることが挙げられます。

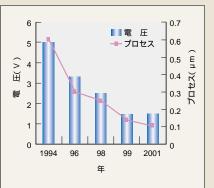

しかし近年では,搭載するLSIの 低消費電力化や小型化の要求から LSIの設計プロセスの微細化が進 み、更なる低電圧化が可能となっています(図3)。このようにLSIの低電圧化が進むと、それまでは問題とならないVRでのエネルギーロスが問題となってきます。そのエネルギーロスとは、VRを使用して電池からLSIへの供給電圧を作るとき、電池電圧と供給電圧との電圧差がVR内で熱となり消費される部分の電力のことです。供給電圧が低いほどこのロスは大きくなり、流れる電流が大きいほど、このロスを改善したときの待受け時電流への影響が大きくなります。

このロスを改善するためには,DC/DCコンバータを使用します。 改善の度合いは使用するDC/DCコンバータ及び電池電圧,供給電圧によって異なります。電池電圧

図2.携帯電話初期の低電圧設計 - 供給電圧を下げるため、VRとショットキーバリアダイオードとを組み合わせて使っていました。

図3.LSIの低電圧化 - LSIプロセスの微 細化に伴って動作電圧が下がってきました。

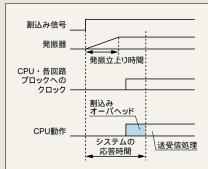

図5.クロック供給制御の設計ポイント例 - 発振回路停止中のCPU送受信動作スタート設計では,システム応答時間が重要です。

外部通信信号 回路 割込み信号 クロック ||プロック 小部通信発生時の 400 イネーブル クロック、 CPU 各回路ブロック イネーブル CPU 400 'ネジメン イネーブル イネーブル イネーブル CPII. 各回路ブロック 発振回路 クロック ¬W¬ クロック 発生回路 発振立上り時間設定

図4.クロック供給制御設計例 - 初期は緑色の部分だけでしたが,段階的に青色の部分,赤色の部分を盛り込んでいきました。

3.6 V ,供給電圧1.8 V時のVRでの ロスは50 %ですが。DC/DCコンバ ータを使用すると ,ロスは10~20 % まで改善することができます。

## クロック供給制御設計

回路動作停止という面での省工 ネ設計には、部品別に電源を入り切りしたりCPU処理をできるだけ少な くするなどセットレベルでの努力と、 回路部分ごとにクロックの供給を制御する部品内部レベルでの努力と が挙げられます。ここでは、回路部分ごとのクロック供給制御設計を例にとって解説します。

デジタル携帯電話が市場に出始 めたときには、動作する必要のない 回路に対するクロックをCPUの制御によって停止させるという,わりと単純な方法を主に使っていました。

しかし,次第に複雑なクロック供給制御方法も使うようになってきました。CPUがCPU自身のクロックを停止したり,クロックの発振回路まで停止したりするようになったのです(図4)。

CPU自身のクロックやクロックの基になる発振回路を停止できるようにするためには、発振回路やCPUクロックを再開する回路(図4では"CPUパワーマネジメント回路"と呼んでいます)の設計を十分考える必要があります。例えば、発振回路が停止している最中に、外部(携帯電

話網や外部に接続された機器)からの通信要求が発生したとします。 CPUが外部からの通信要求に正しく応答するためには,外部からの通信要求を発振回路やCPUに伝えて動作を開始するための割込み信号とそれに連動する回路を単に備えるだけでなく,要求が発生してからCPUが通信処理を開始するまでのシステム応答時間を,必要時間内に設計する必要もあります(図5)。

**NOTES**

**TECHNO**

このように、クロック供給制御の設計は、単に必要なクロックを停止したり再開したりする回路を設けるだけではなく、つねにシステム応答時間を考慮する必要があります。

## 今後の展望

今回,携帯電話の省エネ技術として,部品や回路の低電圧化と,不必要回路部分の動作停止とを挙げて紹介しました。これら省エネ技術の実現方法は,半導体プロセスや回路システム設計と連動して進化しているのです。

今後ますます多くの機能を集積 し 性能を高めていく携帯電話では, 半導体プロセスのいっそうの微細化 に伴って,更に新しい省エネ技術が 必要になるでしょう。

#### 酒井 昌樹

モバイルコミュニケーション社 モバイルコミュニケー ションデベロップメントセンター モバイルソフトウェア 設計第二部主務

#### 谷定 昌弘

モバイルコミュニケーション社 モバイルコミュニケー ションデベロップメントセンター モバイルハードウェア 設計第一部主務

東芝レビューVol. 57 No. 8 ( 2002 ) 省工ネ最前線