# MPEG-4 LSIにおけるシステムLSI技術

System LSI Technology for MPEG-4 Audiovisual LSI

高橋 真史 TAKAHASHI Masafumi 西川 剛志 NISHIKAWA Tsuyoshi

IMT2000(International Mobile Telecommunications 2000)次世代携帯電話やPDA(携帯情報端末)などのモバイル情報機器で、MPEG-4(Motion Picture Experts Group 4)ビデオや音声データを圧縮・伸張するためのMPEG-4対応システムLSIを開発した。独自開発の16ビットRISC(縮小命令セットコンピュータ)型プロセッサとハードウェア(HW)アクセラレータから構成される柔軟なアーキテクチャを採用し、様々なビデオ・オーディオ・多重分離規格に対応することができる。混載DRAM搭載などの低消費電力技術を盛り込むことによって、携帯情報機器用途としては必要十分な低消費電力化を実現した。最新のテレビ(TV)電話対応MPEG-4 LSIは、0.18 μm CMOS(相補型金属酸化膜半導体)プロセスを採用し、TV電話動作時の消費電力を75 mWにまで低減している。

Toshiba has developed an MPEG-4 audiovisual coding/decoding LSI for mobile applications such as PDAs and IMT2000 cellular phone terminals. Various audiovisual and multiplexing standards can be handled by the MPEG-4 LSI with its 16-bit reduced instruction set computer (RISC) processors and dedicated hardware accelerators. Embedded DRAM technology and other low-power techniques are employed in order to reduce power consumption.

This latest MPEG-4 audiovisual LSI is fabricated with 0.18 µm CMOS technology and consumes only 75 mW when operating for video telephony processing.

# 1 まえがき

近年,携帯電話やPDAなどのモバイル情報機器が,ます ますわたくしたちの身近な存在になってきている。これらの モバイル情報機器は、小型・軽量化が進む一方で、インター ネット接続,画像,音楽などの多彩なサービスが展開されて きている。今後,ビデオの録画再生やリアルタイム転送が, モバイル情報機器での重要なサービスの一つとなることが 予想される。ビデオや音楽などのマルチメディアデータは、 そのままでは膨大なデータ量になるため、これらをモバイル 情報機器で扱うためには圧縮・伸張処理が不可欠となる。 マルチメディア圧縮・伸張規格としては,モバイル情報機器 ではMPEG-4の採用が主流となりつつある。これらのマル チメディア圧縮・伸張処理には,数10~数100MIPS(Million Instructions Per Second )の処理性能が要求され,現状の 携帯電話やPDAのホストCPUで処理するには重すぎる処理 であるため,何らかのアクセラレータチップが必要になる。 更に 携帯電話のようにバッテリーで動作する小型機器では, バッテリー容量の制約から、LSIの消費電力に関しても低く 抑えることが要求される。したがって,モバイル情報機器用 のビデオオーディオアクセラレータLSI(以下,マルチメディ アLSI)は,必要十分な処理性能と低消費電力を両立する必 要がある。

ここでは、モバイル情報機器でマルチメディア圧縮・伸張

処理を行うための,MPEG-4対応ビデオオーディオLSIを紹介する。

# 2 MPEG-4 LSIのアーキテクチャ

消費電力 ,実装面積 ,処理の柔軟性を考慮して ,RISC型プロセッサにHWエンジンを組み合わせたアーキテクチャを採用し ,専用マルチメディアLSIとして開発した(\*)(²)。様々なアプリケーションに柔軟に対応したLSIを短期間で開発するため ,必要な機能をIP( Intellectual Property )として容易に切り出し ,再利用できるよう工夫している。

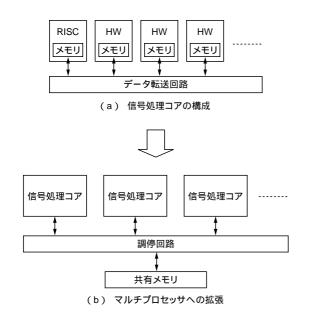

MPEG-4 LSIのアーキテクチャの基本概念を図1に示す。 基本となる信号処理コアは,独自開発された16ビット小型 RISCプロセッサとHWエンジンから構成される。RISCプロセッサは,基本的な命令セットに,絶対値演算などのマルチメディア用命令が付加されており,計算量は少ないが複雑な処理(制御など)を担当する。一方,HWエンジンは,単純であるが計算量の多い処理を担当する。RISCプロセッサや各々のHWエンジンは,作業メモリを保持しており,作業メモリ間のデータ転送は専用回路によって制御される(図1(a))。

このようにして構成された信号処理コアは,アプリケーションからの処理要求に応じてマルチプロセッサ構成へと展開が可能である(図1(b))。複数の信号処理コアが,調停回路を介して単一の共有メモリにアクセスする構成をとること

図1.アーキテクチャの考え方 信号処理コアは、RISCプロセッサとHWアクセラレータで構成される。信号処理コアはマルチプロセッサ構成に拡張可能である。

Architecture concept

ができる。信号処理コアの数が増加すると,共有メモリへの アクセスがボトルネックに成りうる。これを防ぐためには, 共有メモリをオンチップ化することによって,共有メモリのアクセスバンド幅を大きくすることが考えられる。特に大容量メモリが必要な場合には,混載DRAM技術が有効である。このように,信号処理アーキテクチャとLSIテクノロジを融合させることによって,携帯電話用途に最適なマルチメディ

# 3 MPEG-4 マルチメディアLSIの構成

アLSIを開発している。

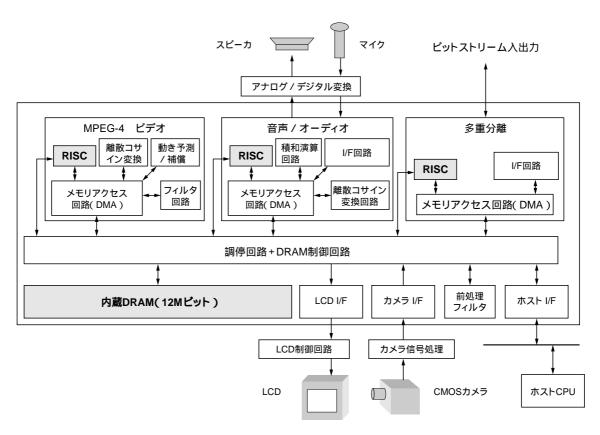

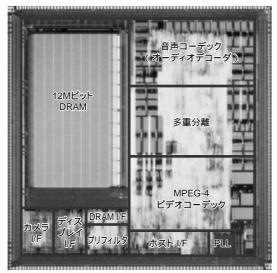

開発したMPEG-4ビデオオーディオLSIの構成を図2に示す。このLSIは、MPEG-4ビデオ、音声/オーディオ、多重分離の三つの信号処理ユニット、周辺インタフェース(I/F)、及び12 Mビットの混載DRAMから構成される。各信号処理ユニットは、命令拡張された16ビットRISCプロセッサとHWエンジンがデータ転送回路で接続される構成をとっている。チップ全体としては、混載DRAMを三つのRISCが共有するマルチプロセッサ構成である。また、各信号処理ユニットには、処理に応じて動き検出、動き補償、離散コサイン変換、積和演算などのHWエンジンが導入されている。周辺I/Fとしては、外部ホストCPU接続I/F、CMOSカメラを直結可能なカメラI/F、ディスプレイI/F、PCMオーディオ入出力I/F、ビットストリームI/Fを備えている。

図2.MPEG-4ビデオオーディオLSIの構成 セッサとHWアクセラレータから構成される。 Configuration of MPEG-4 audiovisual LSI

三つの信号処理コア,周辺I/F回路,12MビットDRAMから構成される。信号処理コアは,RISCプロ

このLSIの動作開始前に、各RISC用のファームウェアプログラムをDRAM上にダウンロードする。ファームウェアは高級言語で開発することが可能であり、ファームウェアの変更によって、将来の規格のバージョンアップや新たなアプリケーションへの対応が可能である。ビデオユニットはMPEG-4ビデオやITU-T(International Telecommunication Union-Telecommunication sector)H.263に対応しており、今後JPEG(Joint Photographic Experts Group)などにも対応する。また、音声ユニットは、AMR(Adaptive Multi Rate)のほかにITU-T G.729、G.723.1音声コーデック、MP3(MPEG-1 Audio Layer3)、AAC-LC(Advanced Audio Coding - Low Complexity)オーディオデコーダに対応する。

### 4 低消費電力技術

モバイル情報機器向けLSIでは、上記の機能を実現するとともに、LSI自体の消費電力を下げることが不可欠である。 LSIの低消費電力技術として、不要な部分へのクロック供給を止めるゲーテッドクロック技術や、並列処理により必要動作クロック周波数を下げる手法が一般的に用いられている。 今回開発したマルチメディアLSIでは、更に下記のような低消費電力技術を導入している。

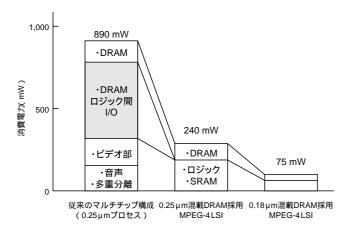

第一の技術は混載DRAMの導入である。これにより、システム全体の消費電力を大幅に削減することができる。混載DRAM導入による消費電力削減のようすを図3に示す。従来のマルチチップ構成時の消費電力の1/2以上をチップ間I/O(In/Out)による消費電力が占めている。今回開発したマルチメディアLSIでは、テレビ電話に必要なほとんどの機能を1チップに収め、更にDRAMを内蔵したことにより、チップ間I/Oに要する消費電力はほぼ0になった。更に、0.18 μmプロセスの採用により、テレビ電話動作時の消費電力75 mWを達成している。

図3.全体消費電力の比較 最新LSIは,0.18 μmプロセスの採用と様々な低消費電力技術により,75mWの消費電力を達成している。 Total power consumption

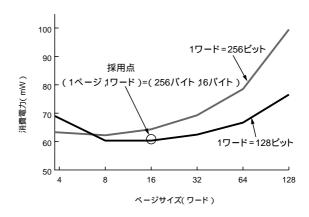

図4.混載DRAM部の消費電力の低減 シミュレーションでDRAM部の消費電力を見積もり、消費電力が最小になる構成を選択した。 Power reduction in embedded DRAM

更に、混載DRAMではビット幅や内部のページサイズを自由に選択することが可能である。各構成による消費電力を、設計前にあらかじめシミュレーションによって求め(図4)、最も消費電力の少なくなる構成を採用した。ページサイズとデータビット幅として、ページサイズ256バイト、ビット幅128ビットを選択した。これによって、DRAM自体の消費電力も、最適構成としなかった場合と比較して20%程度削減されている。

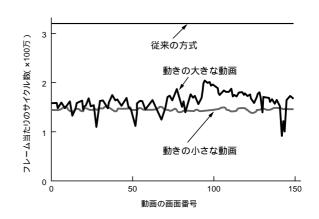

第二の技術は低電力動き検出アルゴリズムの導入である。動き検出は、ビデオ圧縮技術の根幹を成す重要な処理で、その演算量は極めて多い。このLSIでは、新規に開発した動き検出アルゴリズムをHWとして組み込んだ。これによって、誤差を最後まで計算する従来方式と比較して、動きベクトル検出に要する時間を平均で約1/2に短縮している(図5)。これにより、動き検出に要する消費電力も約1/2に低減することができた。

図5.動き検出の処理量削減 新動き検出アルゴリズムの導入により,動き検出時間を1/2に短縮し,動き検出処理で消費する電力も1/2に削減することができた。

Computation reduction in motion estimation

# 5 LSIを用いた携帯端末の実装

開発したMPEG-4ビデオオーディオLSI(TC35273XB)のチップを図6に示す。また、その諸元を表1に示す。60MHz動作時に、TV電話に必要な処理、すなわち、QCIF(Quarter Common Intermediate Format)サイズ(176×144画素)のMPEG-4ビデオ圧縮・伸張(15フレーム/s)、AMR音声圧縮・伸張、及びITU-T H.223多重分離処理を75mWの消費電力で実行することができる。

PLL: Phase Locked Loop

図6 . MPEG-4ビデオオーディオLSIチップ 12MビットDRAM ,三つの処理コア ,周辺I/F回路が1チップに搭載されている。 Chip micrograph of MPEG-4 audiovisual LSI

表1. MPEG-4ビデオオーディオLSIの諸元 Specifications of MPEG-4 audiovisual LSI

| 項目    | 内 容                                                |

|-------|----------------------------------------------------|

| プロセス  | 0.18 µ m CMOS 4層メタル                                |

| 動作周波数 | 最大76.9 MHz                                         |

| ビデオ性能 | MPEG-4 QCIF 15フレーム/s( 60 MHz動作時 )                  |

| 電源電圧  | 1.5 V ± 10 % ,2.5 V ± 10 % ,2.5 ~ 3.3 V ± 10 %の3電源 |

| 消費電力  | 75 mW( 60MHz動作時 )                                  |

| パッケージ | 141ピンFBGA                                          |

FBGA: Fine Ball Grid Array

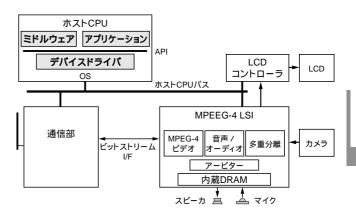

MPEG-4 LSIのねらう応用分野は、携帯電話端末でのテレビ電話機能及びモバイルビデオ配信対応機能である。携帯TV電話端末を実現するための端末構成例を図7に示す。音声対応のIMT-2000携帯電話端末(ホストCPU+ベースバンドチップセット)にMPEG-4ビデオオーディオLSI,CMOSカメラ,カラー液晶ディスプレイ(LCD),LCDコントローラを付加してシステムを構成する。ホストCPUの基本ソフトウェア(OS)上にMPEG-4ビデオオーディオLSI用のデバイスドラ

図7.携帯TV電話の構成例 ホストCPUのバスにMPEG-4 LSIを接続する。ホストCPU上にデバイスドライバほかを搭載する必要がある。 Mobile video telephony

イバをポーティングし, API( Application Program Interface)を定義する。TV電話用ミドルウェア及びユーザーの開発する各種アプリケーションソフトウェアは,このAPIを介してMPEG-4ビデオオーディオLSIにアクセスすることができる。

# 6 あとがき

携帯情報機器向けMPEG-4対応ビデオオーディオLSIを 開発した。0.18 µ mCMOSと混載DRAM技術を採用し,TV 電話動作時の消費電力を75mWにまで低減できた。

今後,携帯電話端末やPDAなど小型情報機器のマルチメディア化が加速されることが予想される。これにより,要求される処理性能は飛躍的に高くなる。これまで開発してきたMPEG-4対応LSIのシステム技術を基に,更に高付加価値なシステムLSIを開発していく。

# 文 献

- (1) Takahashi M. ,et a1 . A 60mW MPEG-4 Video Codec Using Clustered Voltage Scaling with Variable Supply-Voltage Scheme . IEEE Journal of Solid-State-Circuits ,33 ,11 ,1998 ,p.1772 1780.

- (2) Nishikawa T., et al. "A 60MHz 240mW MPEG-4 video-phone LSI with 16Mbit embedded DRAM". ISSCC Digest of Technical Papers . February 2000.

#### 高橋 真史 TAKAHASHI Masafumi

セミコンダクター社 システムLSI事業部 システムLSI開発センター主査。マルチメディアLSIの開発に従事。情報処理学会会員。

System LSI Div.

西川 剛志 NISHIKAWA Tsuyoshi , D.Eng. セミコンダクター社 システムLSI事業部 システムLSI開発センター主務 , 工博。マルチメディアLSIの開発に従事。