# 極薄ゲート酸化膜絶縁破壊機構の解明と新高信頼化成膜プロセスの提案

Study on SiO<sub>2</sub> Degradation Mechanism and Novel Oxidation Process for Highly Reliable Gate Oxide

佐竹 秀喜 SATAKE Hideki 三谷 祐一郎 MITANI Yuichiro

微細化が進むシリコンLSIに用いられる膜厚 10 nm以下の薄いゲート酸化膜の絶縁破壊機構を,新たに考案した評価手法を用いて検討した。ゲート酸化膜の絶縁破壊後抵抗値の統計分布という指標に初めて注目して,絶縁破壊が起きたときに流れ込む蓄積静電エネルギーの大小と時定数に依存して,破壊モード(完全破壊又は擬似破壊)が決定していることを明らかにした。

いずれの破壊モードにおいても、破壊の起源として作用するゲート酸化膜中の欠陥生成を抑制するために、フッ素(F)原子を添加したゲート酸化膜形成を試み、絶縁破壊に至るまでに通すことができる電子総量(Qbd)のウェーハ面内分布のすそ部分を消滅させ、寿命分布をより均一にできることを実証した。

We investigated the mechanisms of dielectric breakdown in ultra-thin  $SiO_2$  used for scaled Si LSIs, using newly developed investigation methods. It was found that  $SiO_2$  dielectric breakdown is dominated by the amount of discharging energy and the time constant for discharging of the stored energy in a MOS system. For the suppression of defect generation in  $SiO_2$ , we demonstrated that fluorine-incorporating  $SiO_2$  has a great potential for realizing a very steep charge-to-breakdown ( $Q_{bd}$ ) distribution.

#### 1 まえがき

LSIの高集積化が進むに伴って,高速化・低消費電力化に対する要求はますます高まっていく。LSIの高速性能を維持していくためには,ゲート酸化膜の薄膜化が必須であり,既に3nmを下回る膜厚が製品で使用される世代になっている。3nmという膜厚はシリコン原子と酸素原子の積み重ねで言うと,わずか10層程度の薄さである。容易に予想されるように,ゲート酸化膜の薄膜化が進むと,ゲート酸化膜の絶縁破壊がいっそう深刻な問題となってくる。LSIの高速性能を維持するために,ゲート酸化膜に印加される電界が高くなっていくためである。また,フラッシュメモリなどの不揮発性メモリに用いられるトンネル酸化膜では,書込み・消去動作の際に10 MV/cm以上の高い電界を印加するため,ゲート酸化膜の信頼性確保が極めて重要となっている。

上記のような背景の下,ゲート酸化膜の絶縁破壊の物理的起源を明確化して,その知見に基づいて,ゲート酸化膜の形成プロセスのあるべき方向性を探るという立場で,われわれは研究を進めてきている。ここでは,新たに開発した評価手法を用いて明らかにした,ゲート酸化膜の絶縁破壊過程の具体的なモデルを示す。更に,絶縁破壊の種となる欠陥生成の抑制を目的として,F原子を酸化シリコン(SiO2)中に導入することによって,ウェーハ内における電気的に弱い箇所の修復を選択的に行い,絶縁破壊に至るまでに通すことができる電子総量(Qbd)のウェーハ面内分布のすそ部分を消滅させ,寿命分布をより均一にできることを実証した。

## 2 ゲート酸化膜の破壊モードを支配する因子

ゲート酸化膜の破壊機構をより正確に理解するために,われわれは今回,ゲート酸化膜が絶縁破壊を起こした後の抵抗値(Rbd)のウェーハ面内分布に初めて注目した。絶縁破壊寿命(bd)やQbdと比較してRbdの分布は,より直接的に絶縁破壊箇所の情報を反映していると判断したためである。Rbdの定義は 絶縁破壊を起こした後に0.5 Vの電圧を印加して,そこに流れる電流をIbdとして,(1)式のようになる。

$$R_{bd}( ) = 0.5( V ) / I_{bd}( A )$$

(1)

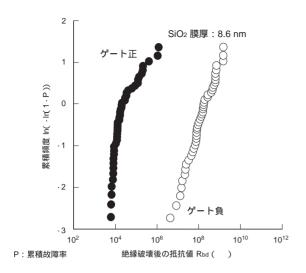

実測に用いた素子は、n型のSi基板上に形成したpチャネルのMOS(Metal Oxide Semiconductor)トランジスタである。図1は、ゲート電極に正及び負の一定電流ストレスを印加して、絶縁破壊を起こした場合のRbd分布(1)を示したものである。ゲート酸化膜厚は8.6 nmであり、破壊時に急峻(きゅうしゅん)な電圧変動を伴う完全破壊(HBD:Hard Break Down)モードですべての素子が破壊している。図に見られるように、ゲート正のストレスを印加した場合には、ゲート負のストレスを印加した場合と比較して、破壊後の抵抗値がめいりょうに小さくなる。

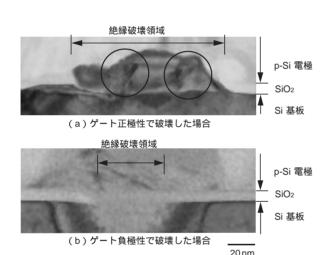

この理由を考察するために、ゲート正負の両ストレスの場合に対して、絶縁破壊箇所の断面を TEM(透過型電子顕微鏡)観察した結果(2)を図2に示す。図2に見られるように、ゲート正ストレス印加の場合には、広い領域にわたって Si 基板表面に大きなうねりを生じ、ゲート酸化膜を突き抜けて結晶相がゲート電極と Si 基板間に存在している。一方、ゲート

図1.ゲート電極に,正及び負の一定電流ストレスを印加した場合の 絶縁破壊後抵抗値Rbdの分布 ゲート正のストレスを印加した場合 には,ゲート負のストレスを印加した場合と比較して,破壊後のRbdの 値が小さくなる。

Rbd distribution for gate-positive and gate-negative stress conditions

図2.ゲート正極性及び負極性のストレスを印加した場合の絶縁破壊 箇所の断面 TEM 像 絶縁破壊断面形状がめいりょうに異なっており、 ゲート正極性の場合(a)には広い領域にわたって破壊が起きている。 TEM images of dielectric breakdown portion for gate-positive (a) and gate-negative (b) stress conditions

負極性の場合には、絶縁破壊領域がめいりょうに狭い。この絶縁破壊の起き方の違いが、図1のRbdの相違に直接的に反映されている。

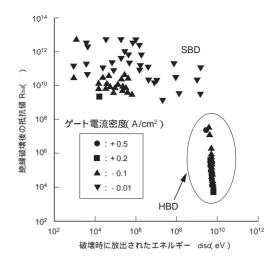

ゲート酸化膜厚が薄くなると,図1及び図2に示した完全破壊モードに加えて,破壊時にわずかな電流増加が観測されるだけの擬似破壊(SBD:Soft Break Down)モードが現れる。図3は,絶縁破壊時に放出される静電エネルギー discとRbdとの相関を示している。 discは(2)式によって見積もった。

$$disc = \{ S_{ch} \times C_{ox} \times (V_{gi}^2 - V_{gf}^2) \}/2$$

(2)

ここにおいて、Schはチャネル面積、Coxは酸化膜容量、Vgi

図3.ゲート酸化膜の絶縁破壊時に放出されるエネルギーとRbdとの相関 HBDの場合には、Rbdは絶縁破壊時の放出エネルギーに強く依存しているのに対して、SBDが起きた場合には、放出エネルギーにはほとんど依存しない。

Relationship between discharging energy at  $\text{SiO}_2$  dielectric breakdown and  $R_{\text{hd}}$

及びVgfは一定電流ストレス印加における絶縁破壊直前のゲート電圧及び絶縁破壊直後のゲート電圧である。図3に見られるように、HBDの場合には、Rbdは discに強く依存しているのに対して、SBDの場合には、放出エネルギーにはほとんど依存しない。更に、放出エネルギーがほとんど同じ場合でも、HBDとSBDの両方が現れている。

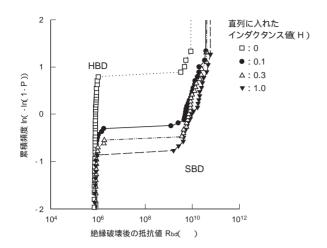

図3の実験事実は,放出されるエネルギーのほかに破壊 モードを決定している因子があることを示している。この因 子は、エネルギー放出の時定数であるとわれわれは考えて いる。その根拠となる実験結果を図4に示す。図4は、測定 回路中に直列に導入したインダクタンス(L)によるHBDと SBDとの頻度分布の変化を示している。図4から,Lが大 きい場合ほどSBDの頻度が大きくなり,エネルギー放出に 要する時定数の大きさが絶縁破壊モードの決定に直接的に 関与していることを示唆している。以上の結果から、ゲート 酸化膜の絶縁破壊は、以下のような過程で進行していると 予想している。ゲート酸化膜に高電界を印加することによっ て,膜中に欠陥が生成される。これらが,ゲート電極からシ リコン基板まで連結する。これが絶縁破壊の第一段階であ る。連結された欠陥パス領域に短時間にエネルギーが流れ 込んで,欠陥パスの周囲も含めて破壊された場合には完全 破壊として観測される。これが絶縁破壊の第二段階である。 一方,ゲート酸化膜厚が小さくなって放出エネルギーが小さ くなった場合,あるいは,エネルギー放出の時定数が長くな った場合には,上記の第二段階のステップは起こらずに,S-BDとして観測されることになる。いずれにせよ,高電界印 加による欠陥の生成を抑制することがゲート酸化膜の信頼 性を高めるために必須であると言える。

図4.測定回路中に導入したインダクタンスの大きさによる,HBDとSBD頻度分布の変化 インダクタンスの値が大きくなるほど,SBDの頻度が高くなる。

Change in ratio of hard and soft breakdowns by inductance serially induced into measured circuit

## 3 F添加によるQbd分布の改善

ゲート酸化膜の絶縁破壊には,大きく分けて2種類あり,一つは真性破壊と呼ばれる酸化膜の本質にかかわる破壊モード,もう一つは外的要因により真性破壊よりも寿命の短い偶発的な破壊モードである。ゲート酸化膜の高信頼化という観点からは,両者のいずれも改善させることが重要であり,様々な高信頼化プロセスが提案されてきている。

偶発不良の原因としては,一般的に酸化膜中の不純物や 欠陥などが考えられており,これらを除去するために,ウェーハのクリーニング技術や酸化プロセス技術の研究・開発 が進められてきた。更に,酸化後の後工程でこれらの欠陥 を修復できれば,より応用性の高い技術となる。

われわれは、2 フッ化ボロン(BF2)をイオン注入して形成した p型ポリSi(p-Si)ゲートトランジスタのQbdのウェー八面内分布が極めて均一であるという研究結果(3)をヒントに、酸化膜の信頼性を向上させる一つの方法として、F原子の役割に着目した(4)。

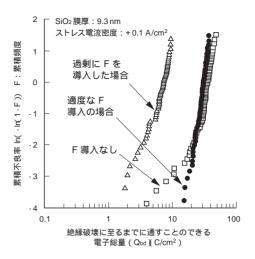

酸化膜へのFの導入には、まずゲート酸化膜上にゲート電極として堆積した多結晶シリコン膜中に、イオン注入法によりFイオンを打ち込む。これを熱処理することで多結晶シリコン中のF原子をゲート酸化膜中に拡散させる。このように、この技術は簡便で、かつ現状のLSIプロセスとの整合性が高いという特長もある。図5は、F導入した酸化膜としていない酸化膜でのQbdの面内分布を累積不良率でプロットしたもの(ワイブルプロット)を示している。図に見られるように、Fをゲート酸化膜中に導入することにより、平均的なQbdの値は劣化させずに、分布のすそ部分だけを消滅させることができることがわかる。一方、過剰にFを導入した場

図5 .Fイオン注入ドーズ量を変えた場合における ,絶縁破壊に至るまでにゲート酸化膜を通過した電子総量 Qbd のワイブルプロットの変化 適切なF量をゲート酸化膜に導入することにより ,Qbd分布を急峻にできるが ,過剰に入れるとQbd分布全体が悪くなる。

Weibull distribution of Qbd according to fluorine dosage

合は ,Qbdの全体が劣化してしまうことから ,F素導入量には 最適値があることもわかる。

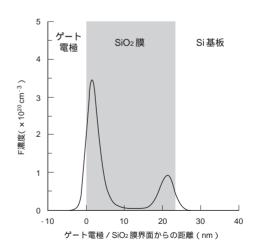

この実験的事実は、ゲート酸化膜中へのF導入による信頼性向上技術として重要であると同時に、Si原子と酸素(O)原子以外の第3の原子をゲート酸化膜中へ導入することによる、電気的な信頼性向上に対する起源の解明についても重要な示唆を与えている。SiO2中の導入されたFの分布を二次イオン質量分析法(SIMS)を用いて分析した結果を図6に示す。ゲート電極多結晶Si膜から拡散したF原子は、主にゲート酸化膜の両界面に分布する。特に、Si基板とゲート酸化膜のヘテロ界面近傍には、界面遷移層と呼ばれる領域があり、この領域は特異な性質を持つことが知られている。F

図6.SIMSによって得られたゲート酸化膜中のFの分布 ゲート電極多結晶Si膜から拡散したF原子は,ゲート酸化膜の両界面に分布する。

Fluorine distribution in Rbd obtained by SIMS

はこのような界面遷移層に選択的に導入され,作用していることが予想される。

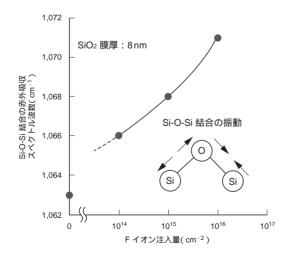

また、F導入によりゲート酸化膜の物理膜厚がわずかに増加し、この増加量はF導入前のSiO2膜厚に依存しないことが、断面TEM観察や電気的評価で得られている。このことから、F添加によるSiO2膜厚増加は主に界面近傍で起きていることが考えられる。更に、フーリエ変換赤外分光法(FT-IR)でF導入によるゲート酸化膜中のSi-O-Si 結合の赤外吸収スペクトルを図7に示す。図7に示されるように、F導入により、Si-O-Si 結合の吸収スペクトル波数が高波数側に移動することがわかる。この吸収スペクトルの高波数側への移動は、SiO2膜中の歪(ひず)んだSi-O-Si 結合の構造緩和を示していると考えられ、Fはゲート酸化膜の構造緩和に寄与していることになる(5)。

以上のように、Fは酸化膜界面に主に導入されること、F導入によって酸化膜厚が増加すること、また、酸化膜の構造緩和が起こること、といった実験結果から、F導入による高信頼化の機構を次のように考えている。前述のSi基板とゲート酸化膜の界面近傍に存在する界面遷移層には歪んだSi-O-Si結合が多く存在すると考えられる。この歪んだ結合は、通常のSi-O-Si結合に比べエネルギー的に不安定で、高電界ストレス印加で容易に切断されることで欠陥が生成され、Qbd分布のすそ部分の原因になる。

これに対し,反応性の高いFはこのような歪んだSi-O-Si 結合と選択的に反応し,Si-F結合を形成すると同時に構造 緩和させる。また,Fにより結合を切られたO原子は酸化膜 界面に拡散し,界面を再酸化して膜厚を増加させる。

以上のようにして,導入されたFが,ゲート酸化膜のネット ワーク構造を再構築することで,すそ部分を消滅させてい

図7.フーリエ変換赤外分光法(FT-IR)で得られたF導入によるO-Si 結合の赤外吸収スペクトルの変化 Fを多く導入するほど,Si-O-Si の吸収スペクトル波数が高波数側へシフトする。

Change in absorption spectrum of Si-O-Si asymmetry stretching vibration by fluorine incorporation, measured by FT-IR

ると考えられる。

### 4 あとがき

急激な薄膜化の要求の高まりに伴って,長期的な信頼性の確保が重要な課題となってきているゲート酸化膜の絶縁破壊機構について,新たな評価手法を用いて得られた実験結果を報告した。更に,ここで得られた知見に基づいて,新たなゲート酸化手法を提案し,その実効性を確認した。

ゲート酸化膜の絶縁破壊機構について,ゲート酸化膜が 絶縁破壊を起こした後の抵抗値の統計的な分布に初めて注 目して解析を行い,ゲート酸化膜の絶縁破壊は,膜中に形成 された欠陥が連結する第1ステップと,連結した欠陥の周囲 を含めて蓄積エネルギーが瞬時に放出される第2ステップ の2段階の連続する過程であることを示した。更に,蓄積さ れたエネルギーの大きさに加えて,エネルギー放出の時定 数が,絶縁破壊の起き方に強く影響していることを示した。

新たな評価手法から得られたSiO2の絶縁破壊機構に関する知見を基礎に,膜中の欠陥生成を抑制する手法として, F原子をゲート酸化膜に導入する技術の構築に取り組み,F が添加されたゲート酸化膜では絶縁破壊耐性のウェーハ面 内分布が抑制されることを確認した。今後は,この検討で の結果に基づき,電気的な信頼性の高いゲート絶縁膜プロ セス技術開発を加速していく。

#### 文 献

- Satake, H., et al. Dielectric Breakdown of Thin-SiO<sub>2</sub> Studied by the Post-Breakdown Resistance Statistics. IEEE Trans. on Electron Devices. 47, 2000, p.741 - 745.

- (2) Satake, H., et al. SiO<sub>2</sub> dielectric breakdown mechanism studied by the postbreakdown resistance statistics. Semiconductor Science and Technology. 15, 2000. p.471 - 477.

- (3) Toriumi, A., et al. "Gate Electrode Effect on Dielectric Breakdown of SiO2." Proceedings of the Material Reserch Society Symposium. 446, 1997, p.3 - 13.

- (4) Mitani, Y., et al." Reexamination of Fluorine Incorporation into SiO<sub>2</sub> Significant Improvement of Charge-to breakdown Distribution Tail ". 1999 IEEE International Reliability Physics Proceedings. 1999, p.93 98.

- 5) Yasuda, N., et al." Spectral Shape Analysis of Infrared Absorption of Thermally Grown Silicon Dioxide Films." Appl. Surface Sience. 117/118, 1997, p.216 - 220.

## 佐竹 秀喜 SATAKE Hideki

研究開発センター LSI 基盤技術ラボラトリー研究主務。 LSI 用絶縁膜形成プロセス技術・信頼性評価技術の研究・ 開発に従事。応用物理学会会員。 Advanced LSI Technology Lab.

三谷 祐一郎 MITANI Yuichiro

研究開発センター LSI 基盤技術ラボラトリー研究主務。 LSI プロセス技術の研究・開発に従事。応用物理学会会員。 Advanced LSI Technology Lab.