携帯用途に適した,低消費電力 MPEG-4( Moving Picture Experts Group 4)テレビ電話用LSIを開発した。このLSIは,MPEG-4処理コア,音声処理コア,多重分離コア,各種インタフェース,更に16 M ビット DRAM を集積する,世界初の単一チップ MPEG-4 テレビ電話用LSI である。従来の低消費電力設計手法に加え,最適化した DRAM の混載,しきい値可変 CMOS,低消費電力動きベクトル検出回路を採用し,240 mW という低消費電力を達成した。

We have developed a low-power LSI for an MPEG-4 mobile videophone. This is the first single-chip, MPEG-4 videophone LSI in the world. In addition to conventional low-power techniques, we adopted new techniques comprising an optimized embedded DRAM, a variable threshold voltage scheme, and low-power motion estimation. The new LSI consumes 240 mW, which is sufficiently low power for typical videophone operation.

## 1 まえがき

近年高速データ通信に対する需要が高まってきている。 家庭用固定回線でも128 kbpsの回線が容易に利用可能となり,更に大容量化の動きを見せている。また,モバイルデータ通信でも64 kbps,更にはそれ以上の速度で通信するための規格が検討されている。そして,この高速回線を用いて民生用携帯テレビ電話を実現できないだろうか,という要望がある。

MPEG-4は,動画像圧縮の国際標準規格であり,通信業界の有力企業などから提出された方式を委員会で比較検討し,優れたものを採用するという手順で策定されている。MPEG-4は当初からモバイル用途を考慮した規格であり,64kbps以下から40Mbpsまで幅広い通信速度をカバーする。このMPEG-4を用いることで,モバイルデータ通信の帯域でも滑らかな動画像を送受信することができる。民生用携帯テレビ電話が近い将来作られるとすれば,それはMPEG-4準拠のものになると思われる。

以前にも当社は、モバイル用途を考慮した低消費電力 MPEG-4 LSI を試作したが<sup>(1)</sup>,携帯テレビ電話を構成するためにはこのLSI 以外に、音声データの圧縮伸張及び符号の多重分離を行うための他のチップを実装する必要があり、小容量に収めるのが困難であった。この問題を解決するため、当社は既に設計資産として存在する MPEG-4 画像処理コアと、音声処理、多重分離用のプロセッサ及び専用ハードウェアを複数個組み合わせ、ワンチップに集積することにした。この構成を採ることにより、性能向上、低消費電力及び省実装面積が同時に実現できる。今回のLSI は、音声の圧

縮伸張回路及び信号の多重分離回路,オーディオ,ビデオインタフェース,更にはDRAMをも統合した,世界初のワンチップMPEG-4テレビ電話用LSIである。以下に,その概要と詳細について述べる。

### 2 LSIの概要

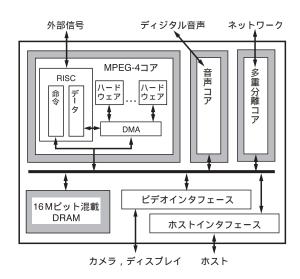

今回開発した,MPEG-4テレビ電話用LSIの構成を図1に示す。構成要素は,MPEG-4画像処理コア,音声処理コア, 多重分離コア,各種インタフェース,そして16 Mビット

図 1 . MPEG-4 テレビ電話用 LSI の回路構成 混載 DRAM, MPEG-4 画像処理コア,音声処理コア,多重分離コアをワンチップに集 積した。

Circuit configuration of MPEG-4 videophone LSI

DRAMである。

MPEG-4画像処理コア,音声処理コア,多重分離コアの構成は同じであり,各1個ずつ搭載された16ビットRISC(Reduced Instruction Set Computer)プロセッサがマスターとなって,複数個の専用ハードウェア及びDMA(Direct Memory Access)コントローラを制御し,演算を遂行する仕組みである。各専用ハードウェア及びRISCプロセッサは,専属の小メモリを装備しており,このメモリはデータを受け渡す,あるいはデータを一時格納するために用いられる。MPEG-4画像処理コアはビデオインタフェース,音声処理コアはオーディオインタフェース,多重分離コアはネットワークインタフェースをそれぞれ制御する。

ビデオインタフェースは、出力装置として汎用のNTSC(現行テレビ方式)エンコーダ、もしくは仕様に準拠する液晶ディスプレイ(LCD)コントローラが接続可能であり、入力装置として汎用のNTSCデコーダ、もしくは仕様に準拠するCMOS(相補型金属酸化膜半導体)センサが接続可能である。

混載16 M ビット DRAM は占有面積最大の部品であり,各コアのプログラムや,信号,画像フレームのバッファとして使用される。この部品を内蔵しているため,外付けのメモリはこのLSIにとって不必要なものになっている。

各種部品の内蔵により、このLSIはワンチップで携帯テレビ電話に必要とされるほとんどの信号処理を実行できる。このことは、実装面から見て、多チップ構成よりもはるかに有利な特長であると言える。

このLSIは複数ハードウェア並列動作により、60 MHz という低周波数でのMPEG-4テレビ電話動作が可能である。これは、より低消費電力の動作が可能ということを示している。更に、各専用ハードウェアは演算をしていないときには、みずからのクロックを停止し電力を節約、RISC プロセッサもみずからのクロックを停止する命令を持っており、プログラム的に電力を節約できる。これらの基本的な低消費電力対策に加えて、新たに三つの低消費電力対策を加えている。それらを次章で述べる。

## 3 低消費電力対策

## 3.1 DRAM の混載

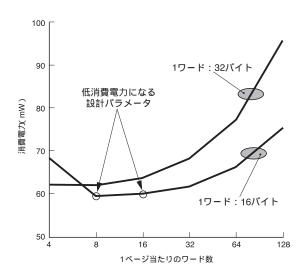

入出力(I/O)端子及びそれにつながるボード上の配線容量は内部配線の容量に比べて大きいため、I/Oを介した通信が少ないほど電力消費が小さくなる。このLSIでは、DRAMを混載することにより、DRAM・プロセッサ間のデータ通信に掛かる消費電力を削減した。更に、混載DRAMにおいてはページサイズ(1ページ当たりのバイト数)とワードサイズ(1ワード当たりのバイト数)を比較的自由に設計できるという柔軟性を利用し、よりいっそうの低消費電力設計を実施した。信号処理中のDRAMに対するデータアクセス

パターンを解析し、DRAM消費電力モデルを用いてページサイズとワードサイズを変化させた際の消費電力値を求めたところ、図2のような特性を得た。これはページサイズ又はワードサイズの大きさの選び方次第では数十mWの消費電力が変化するということを示している。図2の解析結果から、このLSIではDRAMのワードサイズを16バイト、ページサイズを256バイトとした。

図2.DRAMの消費電力 データアクセス解析結果と消費電力モデルを基に、ページサイズを変化させた場合のDRAMにおける消費電力依存性をプロットした。

DRAM power consumption

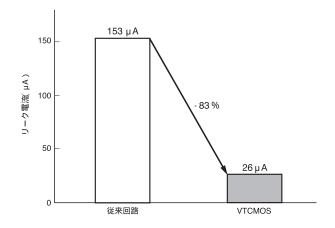

#### 3.2 VTCMOS

低消費電力のために電源電圧を低く設定する場合,動作速度を低下させないように,トランジスタのしきい値も低下させる必要がある。これにより動作時の電力は低減できるが,待機時の漏れ電流が大きくなってしまう。この漏れ電流を低減するため,バックゲートに電圧を掛け,トランジスタのしきい値を動的に引き上げる。このようにして待機時の漏れ電流を低減する技術がVTCMOS(Variable Threshold CMOS)である。図3に示すように,VTCMOSの導入により待機時の漏れ電流を従来の17%にまで削減できた。

#### 3.3 低消費電力動きベクトルの検出

MPEG-4では動画像における時間方向の冗長性を除去するため,フレーム間で動きベクトルの検出を行う。ある参照画像の動きベクトルを算出する場合,次のような処理を行う。対象フレームの探索範囲から参照画像と同じ形状の部分画像を切り出し,参照画像に含まれる画素一つ一つに対して,切り出した画像の対応する画素との差分をとり,更にその絶対値を求めこれを画素の誤差とする。この誤差を参照画像に含まれる画素すべてに対して累積加算し,切出し画像に対する誤差値とする。この値を絶対値差分和(SAD)と呼

MPEG-4 テレビ電話用 LSI 55

図3.従来回路と比較した VTCMOS 回路のリーク電流 リーク電流は,従来回路に比べて17%にまで削除できた。 Leakage current of VTCMOS circuit compared to conventional circuit

ぶ。探索範囲から切り出すことができる部分画像の中で,最小のSADを与える部分画像と参照画像との座標移動量を動きベクトルとするのである。これは総当り的な処理であり、必要演算量が多いことで知られている。

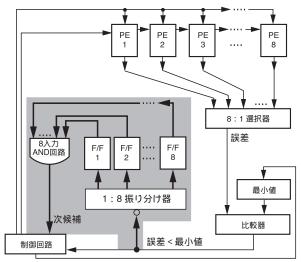

このLSIでは、MPEG-4画像処理コア内の専用ハードウェアが動きベクトル検出を行う。従来の動きベクトル検出回路では、画素の誤差をすべて合計した後に誤差の評価をしていた。図4は、このLSIで用いた改良回路であり、網掛けした回路が新たに付け加えた部分である。図4の回路は、累積加算中の値とその時点で保持している最小の誤差値とを

PE: Processing Element(単位演算要素) F/F: Flip-Flop(1ビット記憶素子)

図4.低消費電力動きベクトル検出回路 8並列の低消費電力動きベクトル検出回路の回路構成を示す。検討中の候補がすべて無効になった場合は,次候補の検討を開始する。

Circuit configuration of low-power motion estimator

比較し,その値を超えた累積加算器をマークする。更に,並列処理する累積加算器がすべてマークされた場合,即座に新しい動きベクトル候補の検討を開始するため,評価に必要なサイクル数が短縮される。この改良に起因する検出精度の劣化はない。

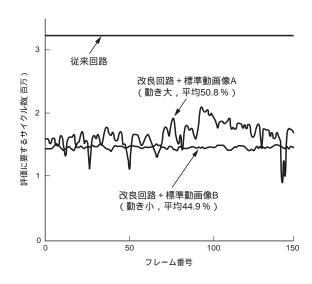

標準動画像の動きベクトル検出を,改良回路を用いて実施した場合の動作サイクル数を図5に示す。従来回路の場合,どのフレームについても固定のサイクル数が動作しなくては評価が完了しない。改良回路の場合,標準動画像Aにおいて平均50.8%,標準動画像Bにおいて平均44.9%のサイクル数で評価が完了している。この効率は入力画像の性質により変動するが,最悪値でも100%(従来回路の固定サイクル数)を超えることはない。前述のように,専用ハードウェアである動きベクトル検出回路は,処理が終了した時点でみずからのクロック供給を停止する。このため,高速化が低消費電力化につながる。必要とする付加回路は小さいため,処理サイクル数の減少は消費電力の減少とほぼ比例する。

図5.動きベクトル検出に要するサイクル数 改良回路は,従来の回路の半分に近いサイクル数で動きベクトル検出を完了することができる。

Cycle count required for search

# 4 LSIの性能

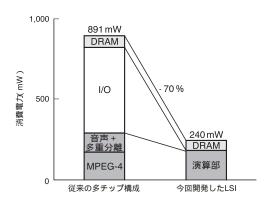

このLSIの消費電力を図6に示す。従来の多チップ構成に 比べて70%の電力削減に成功している。240 mW という消費 電力は,典型的なテレビ電話の使用状態,すなわち MPEG-4 画像処理コアが176 × 144の大きさ(QCIF(注1))の画像を毎

(注1) CIF( Common Intermediate Format )というITU-T( International Telecommunication Union - Telecommunication standardization sector )で定められた画像のサイズがあり、これは352 × 288 画像の短形(くけい)である。QCIF( Quarter CIF )は,縦横ともCIFの半分のサイズであり、176 × 144 画素の画像を表す。

図6.消費電力 MPEG-4画像処理コア,音声処理コア,多重分離コアを搭載し,240mWという低消費電力でテレビ電話に必要な情報処理を実行できる。

Power dissipation

秒 15 枚双方向通信し,音声処理コアが音声圧縮規格 GSM-AMR,G.729 準拠の双方向通信を処理し,多重分離コアは符号通信規格 H.223 の処理を行う状況を想定している。このときの動作周波数は 60 MHz である。動作時電力以外の機能を次に示す。

- (1) MPEG-4 シンプル プロファイルに準拠

- (2) 60 MHz で QCIF 画像を 15 フレーム毎秒双方向処理

- (3) GSM-AMR, G.729, G.723.1 準拠

- (4) オーディオ圧縮規格 TwinVQ, AAC LC 準拠(復号)

- (5) H.223 準拠

- (6) 音声インタフェース搭載

- (7) 動画像インタフェース搭載

- (8) 画像入力用プリフィルタ搭載

- (9) VTCMOS 搭載 ,スタンバイ時リーク電流 65 µ A

# 5 あとがき

MPEG-4テレビ電話用LSIは、このLSIに先駆けて開発していたプロトタイプのMPEG-4画像処理LSIで培った技術を継承しながら、各種インタフェース、音声処理、多重分離処理なども取り込んだ本格的ワンチップテレビ電話用LSIとして実現されたものである。加えて、DRAMの混載、DRAMの最適化、VTCMOSの採用、低消費電力動きベクトル検出回路などで、低消費電力性能に優れたLSIとして、ユーザーニーズにこたえていけるものと期待している。

今後は、よりいっそうの低消費電力化を目指すとともに、マーケットの変化にタイムリーな対応ができるよう努力を続けていきたい。

## 文 献

Takahashi, M., et a1. "A 60mW MPEG-4 Video Codec Using Clustered Voltage Scaling with Variable Supply-Voltage Scheme". ISSCC Digest of Technical Papers. 1998-2. p.36 - 37.

西川 剛志 NISHIKAWA Tsuyoshi, D.Eng. セミコンダクター社 システム LSI 事業部 システム LSI 開 発センター主務, 工博。低消費電力マルチメディア LSI の 設計・開発に従事。応用物理学会会員。 System LSI Div.

MPEG-4 テレビ電話用 LSI 57