# 試作レス開発を実現する 半導体 SPICE モデル生成技術

Technology to Generate Conceptual SPICE Model for Power Semiconductors without Prototyping in Customer Product Conceptual Design Phase

平木 元博 HIRAKI Motohiro 竹田 駿 TAKEDA Shun 馬場 江未瑠 BABA Emiru

パワーエレクトロニクス分野では、製品開発の複雑化に伴い、モデルベース開発(MBD: Model Based Development)の導入が進んでいる。特に、半導体は最終製品の性能に影響するため、顧客のMBD開発環境に対応して電気特性をモデル化したSPICE (Simulation Program with Integrated Circuit Emphasis) モデルを早い段階で生成し、製品企画と同時に回路・システムレベルで検証できるようにして、開発期間短縮や試作削減に貢献することが求められている。

東芝デバイス&ストレージ(株)は、デバイスシミュレーションツールで抽出した電気特性と構想設計データを組み合わせることで、製造前のパワー半導体の特性予測が可能な“コンセプト SPICE モデル”を生成する技術を構築した。既存のLVMOS(低耐圧MOSFET(金属酸化膜半導体型電界効果トランジスター))製品の電気特性を実測して生成したSPICE モデルを基準として、同製品のコンセプト SPICE モデルの誤差を、ドレイン-ソース間電圧( $V_{ds}$ )、ゲート-ソース間電圧( $V_{gs}$ )、及びドレイン電流( $I_d$ )を評価した結果、静特性で15%以下、動特性で20%以下と、構想検討が目的のモデルとして十分な精度で特性予測できることを確認した。

With product development in the field of power electronics growing increasingly complex in recent years, more companies are introducing model-based development (MBD). As semiconductors tend to affect the performance of final products, it is necessary to provide customers with a simulation program with integrated circuit emphasis (SPICE) model which simulates the electrical properties of each device in response to MBD development environment early in the design process. To shorten product development periods and reduce the number of prototypes, demand continues to grow for rapid provision of SPICE models for circuit- and system-level verifications in parallel with device manufacturing planning.

Toshiba Electronic Devices & Storage Corporation has developed technology which generates Conceptual SPICE Model capable of predicting the electrical characteristics of each power semiconductor by combining electrical characteristics extracted using device simulation tools with conceptual design data prior to device manufacturing. Evaluations of a conventional SPICE model based on measured electrical characteristics of the existing low-voltage metal-oxide-semiconductor field-effect transistor (LVMOSFET) and our Conceptual SPICE Model of the same LVMOSFET have verified that the differences in drain-source voltage ( $V_{ds}$ ), gate-source voltage ( $V_{gs}$ ) and drain current ( $I_d$ ) between two models are less than 15% in static characteristics and less than 20% in dynamic characteristics. Conceptual SPICE Model makes it possible to predict electrical characteristics with a sufficient degree of accuracy in the conceptual design phase.

## 1. まえがき

近年、パワーエレクトロニクス分野においては、技術の高度化及び市場ニーズの多様化に伴い、製品開発の複雑性が一層増している。こうした背景の下、開発効率の向上と品質確保を両立させる手法として、MBDを活用したフロントローディング設計が注目されている。これは各設計フェーズでモデルを使い検証するものであり、その適用による開発期間の短縮、コスト削減、及び品質向上が大きく期待されている。特に、パワー半導体の場合、電気的特性が製品性能に直結するため、電気的特性をモデル化したSPICE モデルをいち早く生成することが求められている。

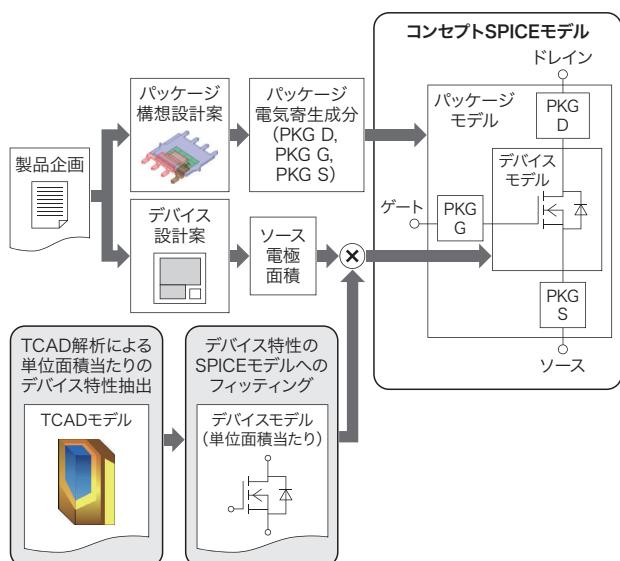

東芝デバイス&ストレージ(株)は、製造前にパワー半導体(MOSFETなど)の電気的特性の予測を可能にするSPICE モデルの生成環境の構築に取り組んでいる<sup>(1), (2)</sup>。従来のSPICE モデルは、半導体製造後に電気的特性を測定し、その結果を基に生成している。これに対し、半導体製造前に性能を予測して生成するSPICE モデルを“コンセプト SPICE モデル”と呼んでいる。これを活用することで、顧客は試作前に回路動作やシステムレベルの検証が可能になり、市場投入までのリードタイムが短縮できる。同時に、当社も製品企画段階での意思決定の質を高めることで、後戻りや不具合を未然に防ぎ、開発の期間短縮が期待できる(図1)。

図1. コンセプト SPICE モデルの活用方法

製品企画段階での回路動作検証が可能となり、開発期間の短縮が期待できる。

Use of Conceptual SPICE Model to shorten development period

## 2. 試作レスを実現するコンセプト SPICE モデル

### 2.1 コンセプト SPICE モデルの特長

コンセプト SPICE モデルは、あらかじめパワー半導体の特性をプロセスや耐圧ごとにデータ化しておき、パッケージの構想設計案から抽出した電気寄生成分と組み合わせることで迅速に生成できる。これにより、デバイスサイズやパッケージ設計の変更による特性への影響が容易に検証できる。

### 2.2 コンセプト SPICE モデルの生成技術

コンセプト SPICE モデルの生成フローを図2に示す。コンセプト SPICE モデルは、大きく分けてデバイスモデルとパッケージモデルで構成される。

図2. コンセプト SPICE モデルの生成フロー

物理情報や構想設計データを基にしたデバイスモデルとパッケージモデルを統合することにより生成できることから、設計変更に伴う電気特性への影響の検証を容易にする。

Conceptual SPICE Model generation process

ステップ1：デバイスモデル生成 デバイスシミュレーションツールのTCAD (Technology Computer Aided Design) による解析で、デバイスの単位面積当たりの電気的特性 ( $I_d - V_{ds}$  特性,  $I_d - V_{gs}$  特性, ボディーダイオードリカバリー電流 ( $I_{dr}$ ) -  $V_{ds}$  特性、及び静電容量 ( $C$ ) -  $V_{ds}$  特性) を抽出する。抽出したデバイス特性をフィッティングした SPICE モデルを生成し、これにデバイス設計案のサイズへの補整を施することで、デバイスモデルを生成する。

ステップ2：パッケージモデル生成 パッケージ設計案から3D (3次元) モデルを構築し、電磁界解析により電気寄生成分を抽出し、パッケージモデルを生成する。

ステップ3：コンセプト SPICE モデル生成 デバイスモデルとパッケージモデルの統合によりコンセプト SPICE モデルを生成する。

コンセプト SPICE モデルの生成においては、ステップ1 のデバイスモデル生成が電気的特性に大きく影響を及ぼす。そこで、デバイスモデル生成のための要素技術として、①TCAD 解析によるデバイス特性抽出技術、及び②SPICE モデルのフィッティング技術について、検討を実施した。これら二つの技術の詳細と有効性について、3章で述べる。

## 3. コンセプト SPICE モデルの要素技術

### 3.1 TCAD 解析によるデバイス特性抽出技術

TCAD は、デバイス構造を微細なメッシュに離散化し、ボアン方程式及び電流連続式を解くことで、デバイスの電位・電界・キャリア密度などの物理量と電気的特性を解析するシミュレーションツールである。

近年のパワー半導体には、オン抵抗 ( $R_{on}$ ) 低減やスイッチング損失の削減、デバイスの微細化が求められ、その構造は日々進化している。新規構造を持つパワー半導体の TCAD モデル開発では、デバイスの特性を精度良く再現する計算結果を得るために、デバイスごとに新たな物理モデルが導入されてきた。当社では、プロセスシミュレーションによるデバイス形状と不純物濃度分布の作成に加えて、応力依存のキャリア移動度やトンネル効果の電界依存性などを考慮することで、デバイス特性を高精度に再現する TCAD モデルを開発・蓄積してきた。

TCAD 解析では、デバイス全てをモデル化して解析することは計算コストの観点から現実的ではない。そのため縦型のパワー半導体は、デバイス構造の1セル単位の解析結果から全体の特性を算出する方法が用いられている。しかし、実際のパワー半導体は、表面にゲート電極や終端領域を設けるため、表面のソース電極面積よりも裏面のドレイン電極

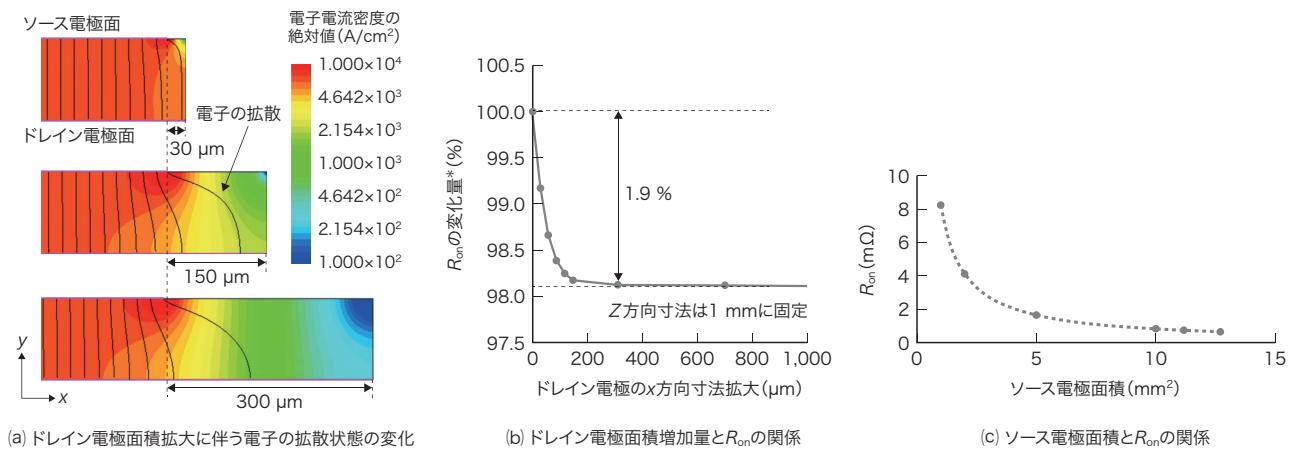

図3. ドレイン電極面積とソース電極面積の電気的特性への影響の検証

ドレイン電極面積の拡大の影響は軽微であり、一方、ソース電極面積の増加は $R_{on}$ に反比例することから、ソース電極面積をデバイスサイズとした。

Effects of drain and source electrode areas on electrical characteristics

面積の方が大きくなる。コンセプトSPICEモデルを生成する上で、このドレイン電極面積が大きいことによる電気的特性への影響と、ソース電極面積をデバイスサイズとするモデル構築が可能か否かについて検証した。

### (1) ドレイン電極面積の電気的特性への影響の検証

ソース電極面積を固定し、ドレイン電極面積を $x$ 方向に拡大する解析を実施した。その結果、図3の(a)と(b)が示すように、ソース端から約300 μmで電子の拡散は収束し、 $R_{on}$ の変化量も1.9 %程度で飽和した。これにより、ドレイン電極面積が大きいことによる電気的特性への影響は軽微であると判断した。

### (2) ソース電極面積と電気的特性の相関関係

図3の(c)にTCAD解析においてソース電極面積を増加させた結果を示す。その結果、ソース電極面積に対して $R_{on}$ は反比例した。これは、オームの法則と同傾向であり、ソース電極面積をデバイスサイズとして適用するモデル構築が可能であることを示している。

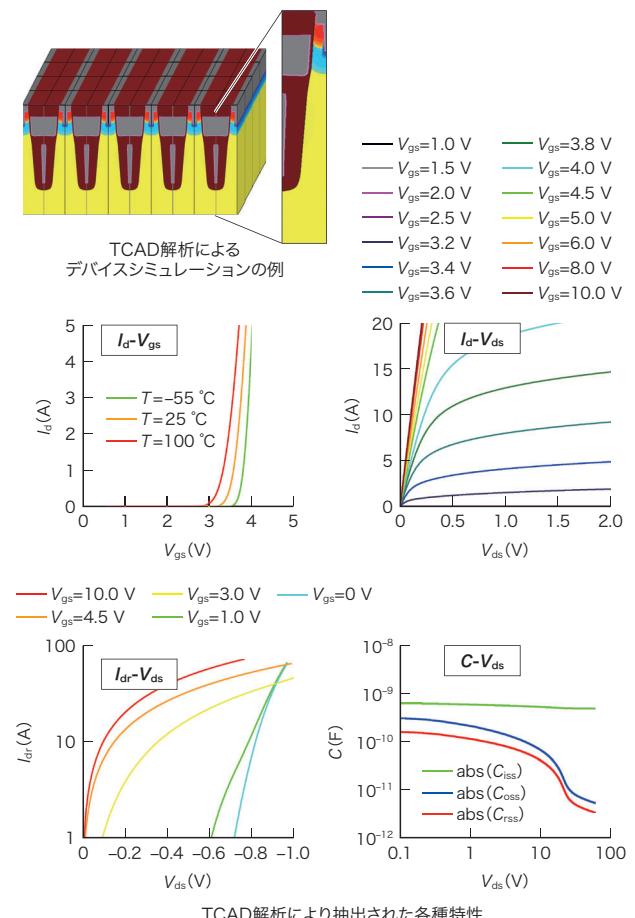

図4に、TCAD解析で抽出した単位面積(1 mm<sup>2</sup>)当たりの電気的特性を示す。これらの特性をターゲットとしたSPICEモデルのフィッティングについて、3.2節で述べる。

### 3.2 SPICEモデルのフィッティング技術

SPICEモデルは、半導体の特性を表す方法として、コンパクトモデル、マクロモデル、及びビヘイビアーモデルに分類される。この検討のモデル作成では、動作が速くフィッティングに適したビヘイビアーモデルを採用している。

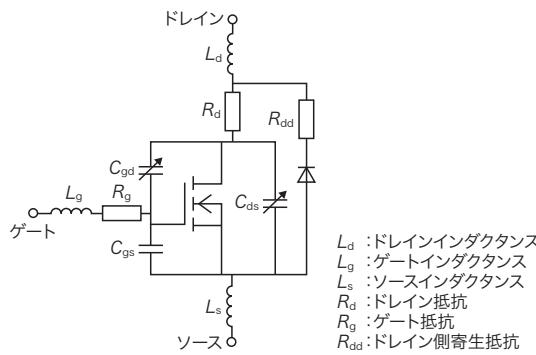

MOSFETのビヘイビアーモデルは、図5の等価回路を用いる。ビヘイビアーモデルとして表現されたコアMOSFET、ボ

TCAD解析により抽出された各種特性

abs:絶対値を計算する関数  $C_{iss}$ :入力容量  $C_{oss}$ :出力容量  $C_{rss}$ :逆伝達容量

図4. TCAD解析によるデバイス特性の抽出

TCAD解析により、1 mm<sup>2</sup>当たりの電気的特性を抽出した。

Electrical characteristics obtained by technology computer-aided design (TCAD) simulations

図5. ビヘイビアーモデルにおけるMOSFETの等価回路

当社のビヘイビアーモデルは、キャリアー移動度の物理的要素をパラメーターとして導入していることを特長としている。

Equivalent circuit of behavioral model for power MOSFETs

ディーダイオード、及び各ノード間の寄生成分で構成されている。

コアMOSFETのモデル式は、以下の式(1)で定義されている。

$$I_d = f_A(V_{ds}, V_{gs}, T; p_{A1}, p_{A2}, \dots, p_{An}) \quad (1)$$

$I_d$ とその支配要因である  $V_{ds}$ ,  $V_{gs}$ , 及び温度 ( $T$ )との関係が、TCAD解析で抽出した  $I_d-V_{ds}$  特性と  $I_d-V_{gs}$  特性に一致するように、フィッティングパラメーターである  $p_{A1} \sim p_{An}$  ( $n$ はデータ数)を調整する。当社のコアMOSFETのモデル式では、キャリアー移動度の温度依存性やキャリアー移動度変調効果、キャリアー速度飽和効果などの物理的要素をパラメーターとして導入している。これにより、収束性及びパラメーター独立性の向上を可能にしている。更に、動作領域(カットオフ、線形、飽和)を滑らかに連結して一つの式で表現しているため、数値計算上の安定性も向上している。

ボディーダイオードのモデル式は、以下の式(2)で定義されている。

$$I_{dr} = f_B(V_{ds}, T; p_{B1}, p_{B2}, \dots, p_{Bn}) \quad (2)$$

$I_{dr}$ とその支配要因である  $V_{ds}$ 、及び  $T$ との関係が、TCAD解析で抽出した  $I_{dr}-V_{ds}$  特性に一致するように、フィッティングパラメーターである  $p_{B1} \sim p_{Bn}$  を調整する。

寄生容量のうち、ゲート-ソース間寄生容量 ( $C_{gs}$ ) は一定値の容量であるが、ゲート-ドレン間寄生容量 ( $C_{gd}$ ) とドレン-ソース間寄生容量 ( $C_{ds}$ ) は  $V_{ds}$  依存で変化する非線形容量である。モデル式は、以下の式(3)で定義されている。

$$C = f_C(V_{ds}; p_{C1}, p_{C2}, \dots, p_{Cn}) \quad (3)$$

$C$ とその支配要因である  $V_{ds}$ との関係が、TCAD解析で抽

出した入力容量( $C_{iss} (=C_{gs}+C_{gd})$ ) $-V_{ds}$ 特性、出力容量( $C_{oss} (=C_{ds}+C_{gd})$ ) $-V_{ds}$ 特性、及び逆伝達容量( $C_{rss} (=C_{gd})$ ) $-V_{ds}$ 特性に一致するように、フィッティングパラメーターである  $p_{C1} \sim p_{Cn}$ を調整する。

#### 4. コンセプト SPICE モデル検証

構築したコンセプト SPICE モデルの精度を検証するためには、既存製品に対してTCAD 解析で抽出した電気的特性からコンセプト SPICE モデルを生成し、実測データから生成した SPICE モデル(以下、実測モデルと略記)と比較評価した。対象製品は、当社製 LVMOS の TPH1R306PL であり、 $V_{ds}$ ,  $V_{gs}$ ,  $I_d$  の最大定格はそれぞれ、 $V_{ds}$  が 60 V,  $V_{gs}$  が  $\pm 20$  V,  $I_d$  が 100 A である。

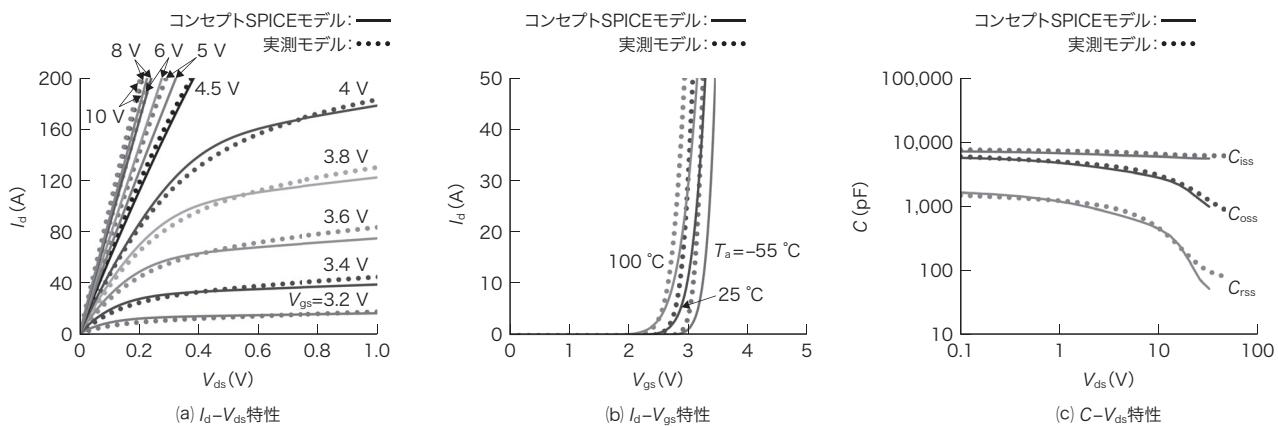

##### 4.1 静特性の検証

静特性については、ソース接地回路を用いて周囲温度 ( $T_a$ ) が 25 °C の条件下での  $I_d-V_{ds}$  特性、及び  $V_{ds}$  が 10 V の条件下での  $I_d-V_{gs}$  特性を抽出した。更に、周波数 ( $f$ ) が 1 MHz かつ  $T_a$  が 25 °C の条件下での  $C$  ( $C_{iss}$ ,  $C_{oss}$ ,  $C_{rss}$ ) $-V_{ds}$  特性についても抽出した。

図6にコンセプト SPICE モデルと実測モデルで代表的な電気特性での比較評価を行った結果を示す。誤差の評価基準としては、実測モデルのデータを真値とし、以下の式(4)で定義する NRMSD (正規化二乗平均平方根誤差) を用いた。

$$NRMSD = \sqrt{\frac{\sum_{k=1}^n (y - y^*)^2}{n}} / (\bar{y}^*) \quad (4)$$

ここで、 $y$  はコンセプト SPICE モデルから得られた値、 $y^*$  は実測モデルから得られた値、 $\bar{y}^*$  は  $y^*$  の最大と最小値の差、 $k$  はデータ番号を表す。

その結果、 $I_d-V_{ds}$  特性 ( $V_{gs}=4.5$  V) の誤差は 4.3 %,  $I_d-V_{gs}$  特性 ( $T_a=25$  °C) の誤差は 14.1 %,  $C-V_{ds}$  特性の誤差はそれぞれ  $C_{iss}$  で 7.7 %,  $C_{oss}$  で 6.3 %,  $C_{rss}$  で 11.2 % となった。

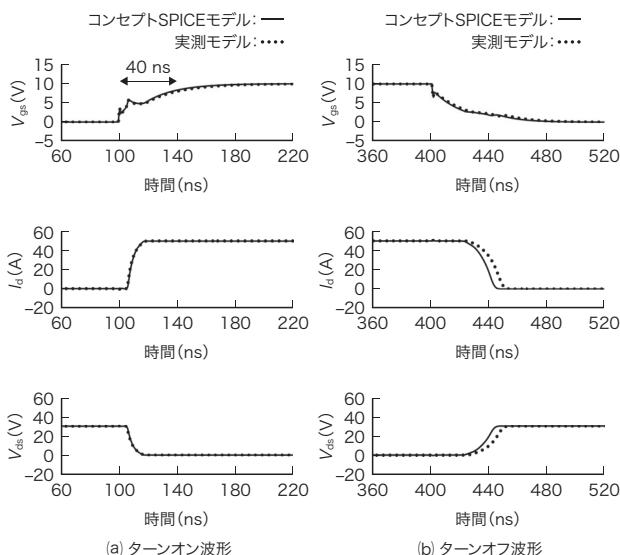

##### 4.2 動特性の検証

動特性(スイッチング特性)については、スイッチング特性測定回路を用いてスイッチング時の過渡特性を抽出した。図7に、コンセプト SPICE モデルと実測モデルで、通電時の  $V_{gs}$  が 10 V の条件でスイッチングした場合の電圧・電流波形の比較結果を示す。 $V_{ds}$  に関してはターンオン時において誤差は 2.4 %、ターンオフ時において誤差は 16.6 % となった。 $I_d$  に関してはターンオン時において誤差は 1.5 %、ターンオフ時において誤差は 16.7 % となった。同様に、通電時の  $V_{gs}$  が 4.5 V の条件でも  $V_{ds}$  と  $I_d$  の誤差は同等となった。

以上のように、コンセプト SPICE モデルは、実測モデルと

図6. コンセプトSPICEモデルの静特性検証結果

静特性の誤差は  $I_d-V_{ds}$  特性,  $I_d-V_{gs}$  特性, 及び  $C-V_{ds}$  特性のいずれも 15 % 以下であり, 実測モデルに近似した結果であった。

Comparison of static characteristics obtained by conventional SPICE model and Conceptual SPICE Model

図7. コンセプトSPICEモデルの動特性検証結果

動特性の誤差は, ターンオン時及びターンオフ時のいずれも 20 % 以下であり, 実測モデルに近似した結果であった。

Comparison of dynamic characteristics obtained by conventional SPICE model and Conceptual SPICE Model

比較して, 静特性検証及び動特性検証のいずれにおいても誤差が 20 % 以下となり, 構想検討を目的とするモデルとして十分な精度であることを確認した。

## 5. あとがき

試作前の段階における回路動作検証を含んだ仕様検討を可能にするため, TCAD 解析によるデバイス特性抽出と SPICE モデルへのフィッティング技術を構築し, 半導体のパッケージ構想案の寄生成分から特性を予測したコンセプト

SPICE モデルを生成した。また, 生成した SPICE モデルは, 実測モデルとの比較検証で近似した結果となっており, 構想検討時の相対評価として用いるモデルとしては十分な精度であることを確認した。今後は, 電気的特性に加えて, 温度特性や信頼性も検証可能なモデルとすることで, 多様な物理現象も考慮した試作レス開発を実現していく。

## 文献

- 岡野資睦, ほか, 車載用パワー半導体の高速・高精度な熱・ノイズミュレーション技術, 東芝レビュー, 2021, 76, 5, p.53-57. <<https://www.global.toshiba/content/dam/toshiba/jp/technology/corporate/review/2021/05/f02.pdf>>, (参照 2025-10-14).

- 東芝デバイス&ストレージ, “車載半導体製品のモデルベース開発 (MBD) 取り組み”, 特集記事, <<https://toshiba.semicon-storage.com/jp/semiconductor/knowledge/highlighted-contents/articles/model-based-development-initiatives-for-automotive-semiconductor-products.html>>, (参照 2025-09-25).

平木 元博 HIRAKI Motohiro

東芝デバイス&ストレージ(株)

半導体事業部

パッケージ&テスト技術開発センター

Toshiba Electronic Devices & Storage Corp.

竹田 駿 TAKEDA Shun

東芝デバイス&ストレージ(株)

半導体事業部

パッケージ&テスト技術開発センター

Toshiba Electronic Devices & Storage Corp.

馬場 江未瑠 BABA Emiru

東芝デバイス&ストレージ(株)

半導体事業部

先端半導体デバイス開発センター

Toshiba Electronic Devices & Storage Corp.