# Star-Deltaスイッチング回路方式による 高降圧率・高変換効率・高電流密度DC-DC変換IC

DC-DC Converter IC with Star-Delta Switching Topology to Achieve Large Voltage Step-Down Ratio, High Power Conversion Efficiency, and High Current Density

テー チェンコン TEH Chen Kong 畢 特 BI Te 伊藤 修一 ITO Shuichi

電源供給経路の導通損失を減らすために、48 Vを直接1 Vにする高降圧率のDC (直流)-DC変換の需要が高まっている。従来、DC-DC変換に使われてきたBuck回路方式は、高降圧率と高変換効率を両立できない。一方、トランジスタを用いると、高降圧率と高変換効率は実現できるが、実装体積が大きくなる。

東芝デバイス＆ストレージ(株)は、トランジスタ不要で高降圧率と高変換効率を実現する独自のStar-Deltaスイッチング回路方式を開発した。この方式では、パワースイッチのオン時間をBuck回路方式の5倍に広げて、スイッチング損失を抑えた。また、IC内のキャパシターの静電容量を小さくする技術を開発し、キャパシタ一面積を最大61%削減してICを小型化した。外付けのトランジスタを3個のフライングキャパシター( $C_{fly}$ )に変えて、実装体積を約1/10にできる。Star-Deltaスイッチング回路方式のICを試作し、トランジスタ使用時と同等の最大変換効率88%と、業界最高<sup>(注1)</sup>の790 mA/mm<sup>2</sup>の高電流密度を確認した。

There is a growing need for large voltage step-down DC-DC converters with 48 V input and 1 V output to reduce conduction losses in power supply system due to rapid rises in load currents at data centers. However, this poses issues such as an insufficient voltage step-down ratio and poor conversion efficiency using conventional Buck topology. Isolated topologies that use transformers can solve such issues, but require a larger mounting volume.

Toshiba Electronic Devices & Storage Corporation has developed a proprietary star-delta switching topology for DC-DC converters to achieve a large voltage step-down ratio and high conversion efficiency without using any transformers. The new topology reduces switching losses by expanding switching-on times fivefold compared with the Buck topology. We have also developed a bootstrap topology for downsizing integrated circuits (ICs) by lowering the capacitance of capacitors in ICs, thereby reducing the layout area by up to 61%. The mounting volume has been shrunk by approximately one tenth by replacing an external transformer with three flying capacitors. Experiments on a prototype IC using the new topology have confirmed basic performance, including a maximum conversion efficiency of up to 88% equivalent to that of conventional ICs using an external transformer and the industry's highest current density of 790 mA/mm<sup>2</sup>.

## 1. まえがき

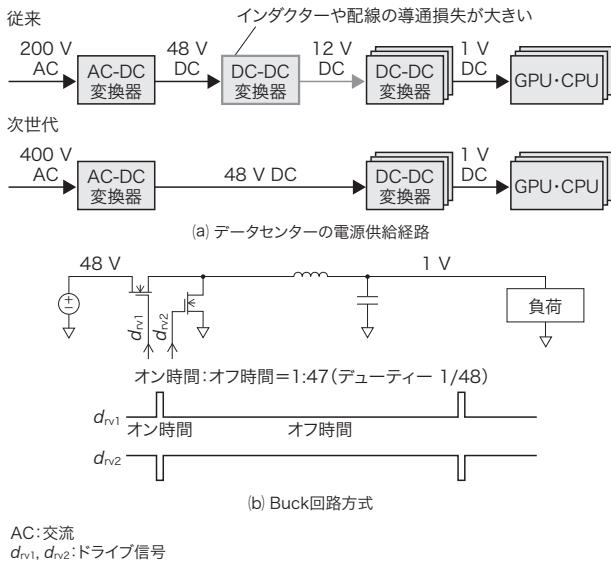

近年、AI処理などの大規模計算を実行するデータセンターでは、負荷電流が急速に伸びており、電源供給経路の導通損失が無視できない。GPU (Graphics Processing Unit) やCPUへの供給電圧1Vを得るために、従来は48Vから12Vを経て1Vに変換していたが、導通損失低減対策として、48Vから直接1Vに変換する(以下、48V-1V変換と略記)規格化<sup>(1)</sup>が進んでいる(図1(a))。

しかし、従来のBuck回路方式の48V-1V変換では、パワースイッチのオン時間をスイッチング周期の1/48と短くし、またソース-ドレイン間のスイッチング振幅を12Vから48Vにする必要がある(図1(b))。そのため、損失が大きく、変換効率が70%程度しか得られない。そこで、トランジスタの

巻き数比を利用しパルス幅を拡大する絶縁回路方式が主流になってきたが、実装体積が大きくなるという問題がある。実装体積を削減するために、スイッチトキャパシタ回路方式が研究されているが、スイッチング時にスパイク電流が生じることがあり、損失とノイズが大きくなる。そこで、キャパシタとインダクタを融合したハイブリッド回路方式<sup>(2)-(4)</sup>が近年提案されており、インダクタが電流を制限する効果を持つため、スパイク電流を抑えることができた。しかし、従来のハイブリッド回路方式は4～12個の $C_{fly}$ を使用するため、IC周りのパワー配線が狭いところに集中して、多層配線が必要になる。

このような中、東芝デバイス＆ストレージ(株)は、3個の $C_{fly}$ で、オン時間のデューティーを1/48から5/48に5倍広げるStar-Deltaスイッチングというハイブリッド回路方式を開発した。ICを試作し、88%の最大変換効率と、最大790 mA/mm<sup>2</sup>の高電流密度を確認した。

(注1) 2024年6月現在、パワースイッチ混載・80%以上の変換効率・2MHz以上のスイッチング周波数の48V-1V変換ICとして、当社調べ。

図1. 電源供給経路とBuck回路方式の概要

導通損失を抑えるためDC-DC変換の高降圧率化が進んでいる。従来使われてきたBuck回路は、スイッチングのオン時間が短く、変換効率を高くできない。

Current and next-generation power supply system and outline of Buck topology

ここでは、Star-Deltaスイッチング回路方式の概要と、試作したICの評価結果について述べる。

## 2. 開発したStar-Deltaスイッチング回路方式

### 2.1 スイッチング層

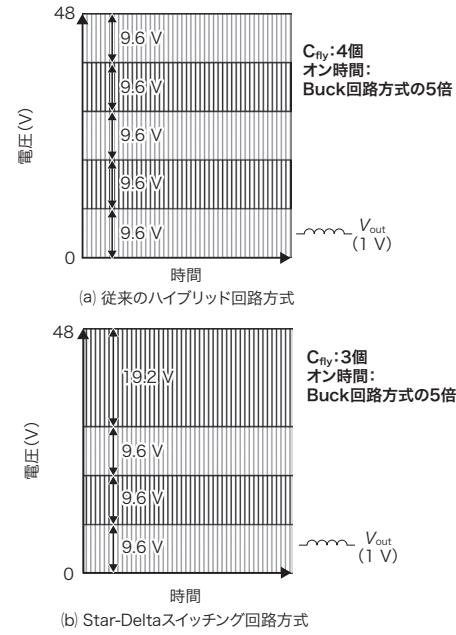

Buck回路方式では、一つのスイッチング層(0Vと48Vの間)であるのに対し、ハイブリッド回路方式は48Vを複数のスイッチング層に分ける(図2)。複数に分けることで、各パワースイッチのドレイン-ソース間電圧 $V_{ds}$ を小さくして降圧量を減らし、オン時間を広げる。図2の例では、一番下のスイッチング層の9.6Vスイッチングからインダクターを通して1Vを生成するため、オン時間はスイッチング周期の5/48(1/9.6)であり、Buck回路方式の1/48の5倍に広がる。

しかし、スイッチング層が $n$ 個の場合、 $n-1$ 個の $C_{fly}$ (図2(a)では4個)が必要であり、実装体積が増える。そこで、上位にある二つのスイッチング層を合併した(図2(b))。DC-DC変換では電圧が高いほど電流が少ないため、上位層の合併によるスイッチング損失の増加は抑えられるからである。この結果、 $C_{fly}$ を3個に減らした。

### 2.2 スイッチング時のLC配置

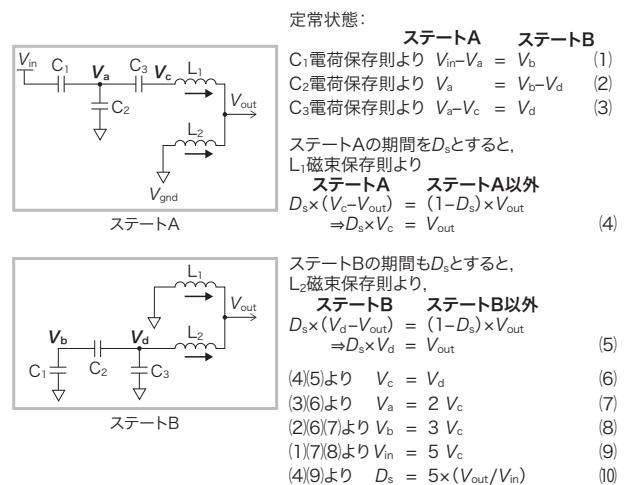

スイッチング層からは回路が一意に決まらないため、まずスイッチング時のLC(インダクター、キャパシター)配置を構築した(図3)。ここで、 $C_1 \sim C_3$ はキャパシター、 $L_1 \sim$

図2. スイッチング層の比較

Star-Deltaスイッチング回路方式は、従来技術であるハイブリッド回路方式よりもスイッチング層数が少ないので、 $C_{fly}$ の個数を減らせる。

Switching layer comparison between conventional hybrid topology and star-delta switching topology

図3. スイッチング時のLC配置

各スイッチング状態におけるインダクターとキャパシターの配置を構築した。 $D_s$ を従来のBuck回路の5倍に拡大した。

Configurations of inductors and capacitors in each switching state

$L_2$ はインダクター、 $V_{in}$ は入力電圧、 $V_a \sim V_d$ は電圧、 $V_{out}$ は出力電圧、 $V_{gnd}$ はグラウンド電圧、 $D_s$ は各ステートのオン時間のデューティーである。

スイッチング状態を、ステートAとステートBの二つとする。ステートAでは、入力電圧 $V_{in}$ からの電流が $C_1$ 、 $C_3$ 、

$L_1$ を通して  $V_{out}$  に供給され、グラウンド電流が  $L_2$  を通して  $V_{out}$  に供給される。ステートBでは、 $C_1$ からの電流が  $C_2$ ,  $L_2$  を通して  $V_{out}$  に供給され、グラウンド電流が  $L_1$  を通して  $V_{out}$  に供給される。ここで、 $C_1$ ,  $C_2$ , 及び  $C_3$  が、ステートAではY形(Star形状), ステートBでは三角形(Delta形状)の配置であるため、これをStar-Deltaスイッチング回路方式と命名した。

電荷保存則と磁束保存則に基づき、各状態の  $V_a \sim V_d$  の方程式を立てて解くと、 $D_s$ は  $5 \times (V_{out}/V_{in})$ を得る(図3)。これは、Buck回路方式の5倍であることを示す。 $V_a \sim V_d$  は一つの解しかないので、定常状態では回路が安定である。

図2(b)では、上からそれぞれ  $V_{in} - V_b$  間,  $V_b - V_a$  間,  $V_a - V_d$  間,  $V_d - V_{gnd}$  間のスイッチング層に該当し、各層の振幅は各々 19.2 V, 9.6 V, 9.6 V, 9.6 V である。

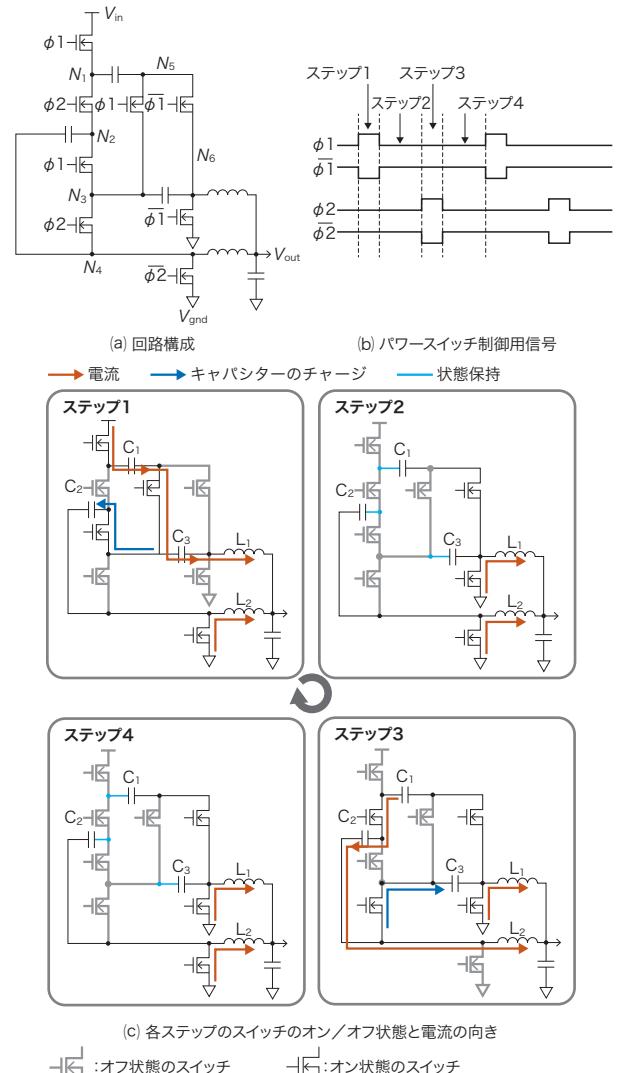

### 2.3 回路動作

2.2節に述べた二つのステートのLC配置を、パワースイッチを用いて実現する回路構成を、図4(a)に示す。 $N_1 \sim N_6$  はノード電圧、 $\phi_1$  及び  $\phi_2$  は回路のパワースイッチのオン/オフ制御信号であり、 $\bar{\phi}_1$  及び  $\bar{\phi}_2$  はその逆相信号である(図4(b))。 $\phi_1$  と  $\phi_2$  のオン時間を等しくして、1サイクルにステップ1～ステップ4の四つのステップを設ける。 $V_{out}$  の値に応じて、オン時間を変調するPWM(Pulse Width Modulation)制御か、スイッチング周期を変調するPFM(Pulse Frequency Modulation)制御かを選択できる。

図4(c)は、各ステップにおけるパワースイッチのオン/オフ状態、及び電流の向きを示す。ステップ1は2.2節のステートAと、またステップ3はステートBと、それぞれ同じLC配置である。ステップ2とステップ4は、 $L_1$ ,  $L_2$  がエネルギーを放出するステップであり、 $V_{gnd}$  から  $V_{out}$  に電流を供給する。四つのステップを繰り返すことで、48 V-1 V変換を実行する。

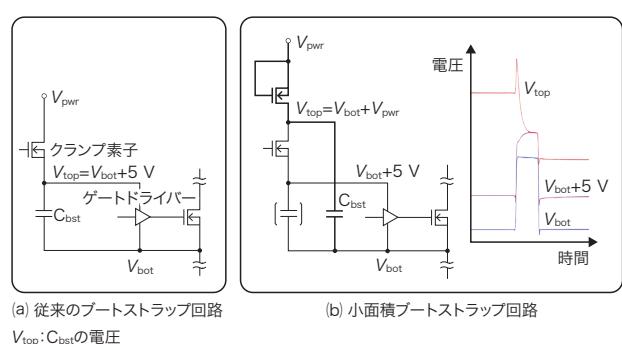

### 2.4 小面積ブートストラップ回路

Star-Deltaスイッチング回路は、複数のN型パワースイッチを立て積みに接続するため、各々のパワースイッチのゲートを駆動する回路(ゲートドライバー)の電圧は、ソース電圧に追随する必要がある。

そのため従来、各パワースイッチに、図5(a)に示すようなブートストラップ回路を設けていた。5 Vをキャパシタ  $C_{bst}$  に印加し、パワースイッチのソース電圧  $V_{bot}$  が高まると、 $C_{bst}$  の上側の端子電圧( $V_{bot} + 5$  V)も追随して高くなる。次に、 $C_{bst}$  の電圧はゲートドライバーを通してパワースイッチのゲートに供給するが、パワースイッチのゲートの寄生容量が大きいため、 $C_{bst}$  の静電容量を大きくする必要があり、その結果、 $C_{bst}$  の面積が大きくなるという問題があった。

図4. 開発したStar-Deltaスイッチング回路とその動作

回路中の8個のパワースイッチをスイッチングして、四つのステップを繰り返し、48 V-1 V変換を行う。

Developed star-delta switching topology and operational details

図5. 開発した小面積ブートストラップ回路の概要

従来に比べて、 $C_{bst}$ の静電容量を最大87%減らし、IC上の $C_{bst}$ の面積を最大61%縮小した。

Developed bootstrap circuit with size reduction

そこで、図5(b)に示す小面積ブートストラップ回路を開発した。この回路では、5 Vよりも数倍高い電源電圧  $V_{\text{pwr}}$  を  $C_{\text{bst}}$  に印加し、パワースイッチのソース電圧が上昇するとき、 $C_{\text{bst}}$  の電圧をより高い電圧 ( $V_{\text{bot}} + V_{\text{pwr}}$ ) として一旦生成して、クランプ素子で  $V_{\text{bot}} + 5$  V にクランプしてゲートドライバーに供給する。 $C_{\text{bst}}$  のチャージ量  $Q$  は、 $C_{\text{bst}}$  の静電容量と  $V_{\text{pwr}}$  の積であるので、同じ  $Q$  値を得るための  $C_{\text{bst}}$  の静電容量は、 $V_{\text{pwr}}$  が大きいほど小さくできる。これにより、ブートストラップ回路の  $C_{\text{bst}}$  の静電容量を最大 87 % 減らして、必要な面積を最大 61 % 縮小し、IC 内に収容できるようにした。

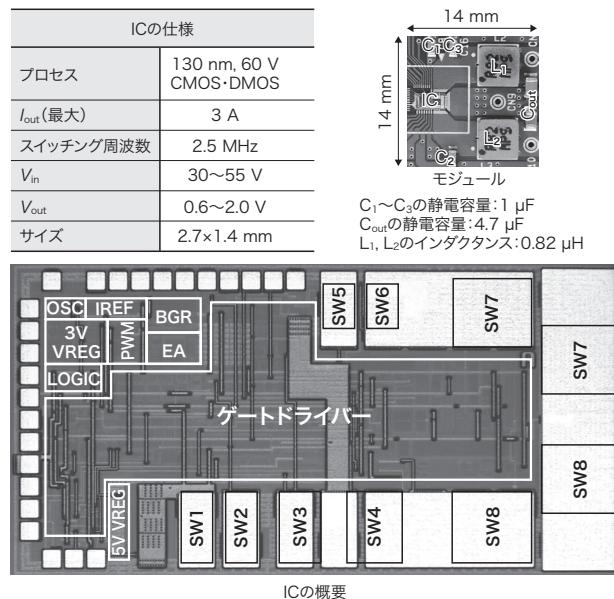

### 3. IC 試作・評価

130 nm CMOS (相補型金属酸化膜半導体)・DMOS (二重拡散型金属酸化膜半導体) プロセスにより、Star-Delta スイッチング回路方式の DC-DC 変換 IC を試作した (図6)。IC のサイズは  $2.7 \times 1.4$  mm と小さいが、パワースイッチと制御回路だけでなく、ブートストラップ回路も全て搭載できた。1 V 出力で、 $V_{\text{in}}$  は 30 ~ 55 V、出力電流  $I_{\text{out}}$  は最大 3 A である。モジュール体積は  $14 \times 14 \times 2$  mm で、トランジスタ使用時の約 1/10 である。スイッチング損失及び面積の削減のため、パワースイッチの耐圧が  $V_{\text{in}}$  の 48 V よりも小さい N 型 DMOS を採用する (40 V, 25 V, 18 V など)。

OSC:発振器 IREF:基準電流源 3V VREG:3 V電圧源

LOGIC:ロジック回路 BGR:Band Gap 基準電圧源 EA:エラーアンプ

5V VREG:5 V電圧源 SW1~SW8:パワースイッチ

図6. 試作IC

パワースイッチや制御回路だけでなく、小面積ブートストラップ回路も IC 内に搭載した。

Prototype IC

また、起動前の  $V_{\text{ds}}$  破壊を回避するため、パワースイッチのソース電圧を所定値にプルアップする回路も搭載した。2 相の PWM 制御を採用し、2.5 MHz 相当のスイッチング周波数で、 $L_1$ ,  $L_2$  インダクター値を  $0.82 \mu\text{H}$  に、出力キャパシタ  $C_{\text{out}}$  は  $4.7 \mu\text{F}$  2 個に抑えた。 $C_{\text{fly}}$  は、 $1 \mu\text{F}$  3 個を用いる。

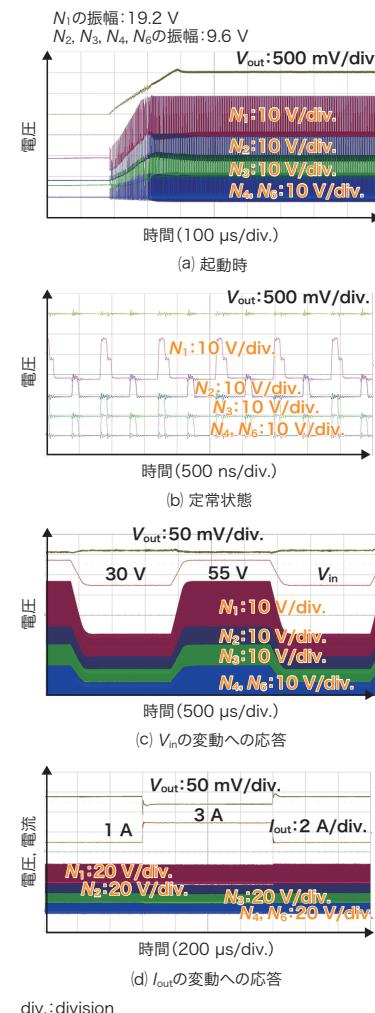

図7 に、過渡応答の測定結果を示す。起動すると、各ノード電圧 ( $N_1 \sim N_6$ : 図4) は 19.2 V 又は 9.6 V の振幅に安定してスイッチングされ、 $V_{\text{out}}$  がランプアップして 1 V に収束する (図7(a))。時間範囲を拡大すると、隣同士のノードで異なる位相での動作が確認できる (図7(b))。30 V と 55 V の  $V_{\text{in}}$  変動に対して、 $V_{\text{out}}$  の変動が  $\pm 10$  mV 以内に抑えられており、小面積ブートストラップ回路が  $V_{\text{in}}$  の急変動に対応できることを確認できた (図7(c))。1 A と 3 A 間の

図7. 試作ICの過渡応答の測定結果

定常状態では、各ノードが 19.2 V 又は 9.6 V の振幅でスイッチングをする。 $V_{\text{in}}$  の変動に対しては  $V_{\text{out}}$  変動は  $\pm 10$  mV 以内、 $I_{\text{out}}$  変動に対しては  $V_{\text{out}}$  変動は  $\pm 45$  mV 以内であった。

Results of transient response tests on prototype IC

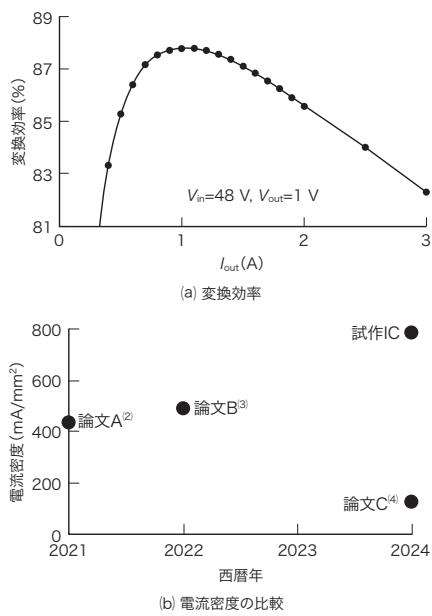

図8. 試作ICのDC測定結果

最大変換効率88 %、電流密度790 mA/mm<sup>2</sup>を確認した。

Results of DC measurement tests on prototype IC

$I_{out}$ 変動(1 A/μs)に対して、 $V_{out}$ の変動は±45 mV以内であり、必要な性能を持つことを確認した(図7(d))。

図8(a)に変換効率の測定結果を示す。48 V-1 V変換では最大88 %の変換効率を得た。図8(b)にICの電流密度の比較結果を示す。既発表の論文A～C<sup>(2)-(4)</sup>に比較して、最も高い<sup>(注1)</sup>電流密度790 mA/mm<sup>2</sup>を実現した。

#### 4. あとがき

トランジスタ不要のStar-Deltaスイッチング回路方式を開発し、48 Vから1 Vへの高い降圧率を実現した。試作したDC-DC変換ICで、最大変換効率88 %と、790 mA/mm<sup>2</sup>の優れた電流密度を確認した。また、Star-Deltaスイッチング回路方式によりIC周りにパワー配線が集中する問題を解決し、多層配線を不要にした。

この論文では、3個のC<sub>fly</sub>で5倍のオン時間拡大を中心述べたが、4個のC<sub>fly</sub>で8倍のオン時間拡大も試作済みである<sup>(5)</sup>。また、今回のモノリシック版による試作では $I_{out}$ は最大3 Aであるが、スイッチサイズを大きくすることで10 Aまで拡張でき、更に、低いスイッチング層にあるパワースイッチを外付けにすると、100 A以上に引き上げられる見込みである。

今後、サーバー、車載、及び工業向けに、製品化を進めていく。

## 文献

- (1) Open Compute Project. "Open Rack Standard V2.0", <<https://www.opencompute.org/documents/openrack-standard-v20-overview>>, (accessed 2025-10-07).

- (2) Yang, X. et al. "33.4 An 8A 998A/inch<sup>2</sup> 90.2% Peak Efficiency 48V-to-1V DC-DC Converter Adopting On-Chip Switch and GaN Hybrid Power Conversion". 2021 IEEE International Solid-State Circuits Conference (ISSCC) Proc. San Francisco, CA, 2021-02, IEEE, 2021, p.466-468.

- (3) Chen, C. et al. "A 2.5-5MHz 87% Peak Efficiency 48V-to-1V Integrated Hybrid DC-DC Converter Adopting Ladder SC Network with Capacitor-Assisted Dual-Inductor Filtering". 2022 IEEE ISSCC Proc. San Francisco, CA, 2022-02, IEEE, 2022, p.234-236.

- (4) Choi, H.-J. et al. "A 92.7% Peak Efficiency 12V-to-60V Input to 1.2V Output Hybrid DC-DC Converter Based on a Series-Parallel-Connected Switched Capacitor". 2024 IEEE ISSCC Proc. San Francisco, CA, 2024-02, IEEE, 2024, p.156-158.

- (5) Teh, C. K. et al. "730-790mA/mm<sup>2</sup> 48V-to-1V Integrated Hybrid DC-DC Converters based on a Star-Delta Switching Network with 5x/8x Duty Expansion". 2024 IEEE Symposium on VLSI Technology and Circuits. Honolulu, HI, 2024-06, IEEE, 2024, C21.4.

-

TEH Chen Kong, D.Eng.

東芝デバイス&ストレージ(株)

半導体事業部 IC開発センター

博士(工学)

Toshiba Electronic Devices & Storage Corp.

BI Te, D.Eng.

東芝デバイス&ストレージ(株)

半導体事業部 IC開発センター

博士(工学)

Toshiba Electronic Devices & Storage Corp.

ITO Shuichi

東芝デバイス&ストレージ(株)

半導体事業部 IC開発センター

Toshiba Electronic Devices & Storage Corp.