# パワーデバイスのスイッチングノイズを 設計段階で予測するシミュレーション技術

Simulation Technology to Predict Noise in Switching Operations of Power Devices in Design Phase

安住 壮紀 YASUZUMI Takenori 山下 浩明 YAMASHITA Hiroaki 子迫 修司 KOSAKO Shuji

東芝グループは、Si (シリコン)パワーデバイスであるMOSFET (金属酸化膜半導体型電界効果トランジスター)やIGBT (絶縁ゲート型バイポーラートランジスター)の動作中に生じるスイッチングノイズを予測するシミュレーション技術を開発した。実機動作を再現する等価回路の詳細なモデリングによって、パワーデバイスの設計段階でスイッチングノイズが計算可能になった。

この技術を、試作したMOSFETやIGBTに適用し、それぞれのスイッチングノイズのレベルとその発生メカニズムを明らかにした。メカニズムを基にスイッチングノイズを抑えた設計をすることで、設計の後戻りを抑制し、開発効率の向上を図る。

The Toshiba Group has developed simulation technology to predict noise in switching operations of silicon (Si) power devices, including metal-oxide-semiconductor field-effect transistors (MOSFETs) and insulated gate bipolar transistors (IGBTs), through detailed modeling of equivalent circuits to replicate actual device operations, thereby calculating the switching noise in the power device design phase.

We conducted simulation tests using prototype MOSFETs and IGBTs confirming that the technology can accurately estimate switching noise levels and clarify the noise generation mechanisms of each prototype device. This makes it possible to design low switching noise devices based on the noise generation mechanisms obtained through simulations and is expected to streamline power device development thanks to reducing design process retrogression.

## まえがき

電力変換装置の高効率化や高エネルギー密度化に向けて、電力変換装置内の回路に搭載するMOSFETやIGBTなどのSiパワーデバイスの高性能化が重要となっている。パワーデバイスの重要指標として、動作中のスイッチング損失に関係する $R_{\rm on}A$ (単位面積当たりのオン抵抗)やスイッチング速度が挙げられる。スイッチングの高速化でスイッチング損失を改善できる一方で、スイッチング時の電流・電圧の時間変動が大きくなり、スイッチングノイズが増加する。

電気製品は、規格で定められたEMI (Electromagnetic Interference) 許容値をクリアする必要がある<sup>(1)</sup>。そのため、製品に搭載されるパワーデバイスは、スイッチング損失の増加を避けながら、スイッチングノイズを抑えることが望ましい。

そこで東芝グループは、実機動作を再現するための等価 回路の詳細なモデリングによって、スイッチングノイズを予 測するシミュレーション技術を開発した。設計段階でスイッ チングノイズを予測して、レベルや発生メカニズムを明らか にすることで、試作前に改善策を適用し、開発効率の向上 を図る

ここでは、開発したシミュレーション技術を、試作した MOSFETとIGBTに適用した結果について述べる。

## 2. SJ-MOSFET

従来のSi半導体を用いたプレーナー型のMOSFETで発生するスイッチング損失を低減するため、低 $R_{on}A$ かつ高耐圧特性を実現するSJ (Super Junction) -MOSFETが開発されている $^{(2)}$ 。従来と同一の $R_{on}A$ において寄生容量が低減できるため、低損失で高速スイッチング化が可能である。しかし、スイッチングノイズは増加する。

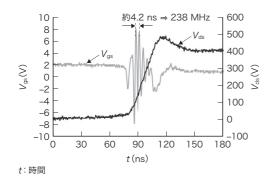

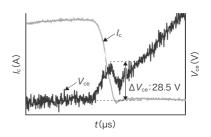

SJ-MOSFET の特徴的なスイッチングノイズとして、**図1** にターンオフ時の電圧波形を示す。ドレイン-ソース間電圧  $V_{ds}$ が増加して数十V程度となるタイミングで、ゲート-ソース間電圧  $V_{gs}$ に周期が約4.2 nsのスイッチングノイズが発生している。これが、238 MHz 付近の放射 EMI  $\ell$ -クの要因となる。

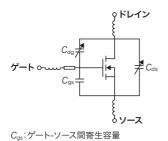

パワーデバイスのスイッチング動作を詳細に分析するための手法として、等価回路シミュレーションが有効である。任意の端子間電圧に加え、実機評価では観測が不可能なパワーデバイス内外を流れる電流を可視化できる。パワーデバイスのチャネルや端子間の寄生容量を流れる各々の電流を分離して観測するために開発したSJ-MOSFETデバイスモデルを図2に示す。ここでは、回路シミュレーターに用意されているデバイスモデルの電流-電圧(I-V)特性やしきい

#### 図1. SJ-MOSFETがターンオフした際の電圧波形

ターンオフ時に、238 MHzのスイッチングノイズの発生を確認した。

Voltage waveform data of superjunction MOSFET (SJ-MOSFET) when turned off

## 図2. SJ-MOSFET デバイスモデル

実測値に合うようにパラメーターを調整して、デバイス内の寄生容量や寄生 インダクター成分を詳細にモデル化した。

SJ-MOSFET device model

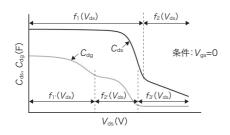

# 図3. デバイスモデルの寄生容量特性

$C_{

m ds}$ と $C_{

m dg}$ の $V_{

m ds}$ に対する特性が、実デバイスの測定結果を再現するように、モデル化した。

Device model parasitic capacitance characteristics

値電圧 $V_{th}$ を実測値に合うように同モデル内のパラメーターを決定した。

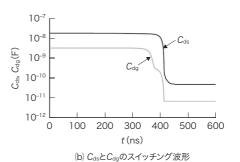

図2のデバイスモデルの、ドレイン-ソース間の寄生容量  $C_{ds}$ とドレイン-ゲート間の寄生容量  $C_{dg}$ の、 $V_{ds}$ 依存性を、図3に示す。 $C_{ds}$ と $C_{dg}$ は、 $V_{ds}$ 依存性を表現するために、 $V_{ds}$ の領域ごとに任意の指数関数 $f_1(V_{ds})$ 、 $f_2(V_{ds})$ , $f_{1'}(V_{ds})$ , $f_{2'}(V_{ds})$ ,及び $f_{3'}(V_{ds})$ を設定した。このデバイスモデルでスイッチング波形をシミュレーションした結果、図1に示した

図4. スイッチング波形のシミュレーション結果

開発したデバイスモデルでシミュレーションした結果、実際と同様のスイッチングノイズを再現できた。

Switching waveform simulation data when using device model

(b) C<sub>gs</sub>·の有無による放射EMIの違い

#### 図5. V<sub>gs p-p</sub>と放射EMIの測定結果

シミュレーション結果による予測のとおり、実際の測定で $C_{\mathbb{S}^s}$ による放射 EMIの低減効果を確認した。

Result of peak-to-peak gate-source voltage ( $V_{\rm gs\ p-p}$ ) and radiated electromagnetic interference (EMI) noise measurements

数百MHzのスイッチングノイズを再現できた( $\mathbf{Z}$ 4(a))。スイッチングノイズのレベルは、 $C_{ds}$ や $C_{dg}$ の時間変化に依存している。これら寄生容量の時間変化を可視化できることも開

発技術の特長である(図4(b))。

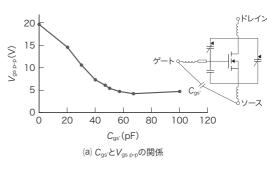

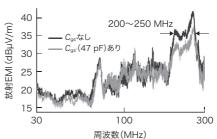

シミュレーション結果を踏まえて、スイッチングノイズを抑制するために、ゲート-ソース端子間に小容量の静電容量  $C_{gs'}$ を接続した場合の効果を、検証した。 $C_{gs'}$ の適正値を決定するために、 $C_{gs'}$ に対する $V_{gs}$ のスイッチングノイズの振幅  $V_{gs}$  p-p を測定した( $\mathbf{図5}(\mathbf{a})$ )。 $V_{gs}$  p-p は $C_{gs'}$  の増加に伴って減少し、47 pF以上では5~7 V程度に収束することが分かる。図5(b)は、47 pFの $C_{gs'}$ 有無による実際の放射 EMIの違いを示しており、200~250 MHz で抑制効果を確認した。

### 3. RC-IGBT

RC (Reverse Conducting)-IGBTは, FWD (Free Wheeling Diode)をIGBTのチップに組み込んだデバイスである。

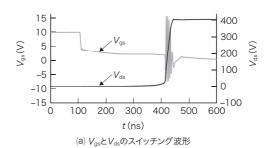

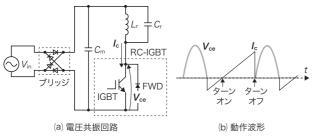

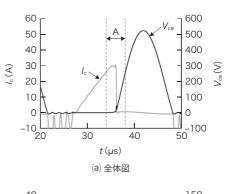

図6(a)に、IH (Induction Heating) 家庭調理用機器のインバーターシステムなどに使われるRC-IGBTを用いた電圧共振回路を示す。ターンオン時は、RC-IGBTのコレクター電流 $I_c$ とコレクターーエミッター間電圧 $V_{ce}$ はほぼゼロであり、 $I_c$ の時間変化も緩やかであるが、ターンオフ時は、 $I_c$ が急峻(きゅうしゅん)にゼロへと向かうため、スイッチングノイズが発生しやすい(図6(b))。

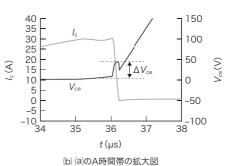

電圧共振回路のターンオフ時に観測したスイッチング波形の測定結果を $\mathbf{27}$ に示す。この回路は、インダクターとコンデンサーを負荷とした電圧共振型の回路であり、ターンオフの際は、 $V_{\rm gs}$ の立ち下がりに応じてコレクター - エミッター間電圧  $V_{\rm ce}$  が正弦波状に変化する。図7では、変化を開始する際にこぶ状のノイズ波形が重畳しており、その立ち上がり時間などから数十MHzの放射 EMIに影響すると推測できる。ここで、 $V_{\rm ce}$  が立ち上がる前の値とこぶ状の波形のピーク値との差 $\Delta V_{\rm ce}$ を放射 EMI の指標として着目した。2 章と同様に、実測値のI-V特性や寄生容量特性に沿った RC-

$V_{\rm in}$ : 入力電圧  $C_{\rm m}$ : 主コンデンサー  $L_{\rm r}$ : 共振用インダクター  $C_{\rm r}$ : 共振用コンデンサー

## 図6. RC-IGBTを用いた電圧共振回路と動作波形の例

ターンオフ時に $I_c$ の変化が大きくなり、スイッチングノイズが発生しやすい。 Voltage-controlled resonant circuit using reverse-conducting IGBT and example of waveform data during operation IGBTのデバイスモデルを開発することで、こぶ状の波形を シミュレーションで再現できた(図8)。

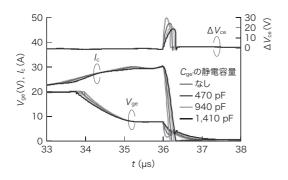

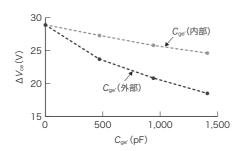

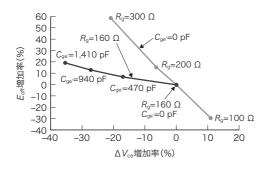

大きなスイッチング損失増加を避けるためには、スイッチング時間への影響を小さく抑えながらターンオフ時の $I_c$ の傾きを緩やかにする、ゲート-エミッター間静電容量 $C_{ge}$ への追加静電容量 $C_{ge}$ の接続が有効であり、 $C_{ge}$ が大きいほど抑制効果が高い(図9)。また、 $C_{ge}$ をパッケージ内部(RC-IGBTチップ内)に接続するより外部(パッケージ配線を介した端子間)に接続する方が、 $C_{ge}$ による $\Delta V_{ce}$ 抑制効果が高い(図10)。

次に、外部に $C_{\rm ge'}$ とゲート抵抗 $R_{\rm g}$ を接続して、 $C_{\rm ge'}$ と $R_{\rm g}$ を変えた場合の、 $\Delta V_{\rm ce}$ の増加率とターンオフ時のスイッチング損失 $E_{\rm off}$ の増加率との関係を、シミュレーションで求めた

図7. ターンオフ時のスイッチング波形の測定結果 この測定結果から,放射 ${

m EMI}$ の指標として $\Delta V_{ce}$ に着目した。 Switching waveform measurement data when turned off

図8. ターンオフ時のスイッチング波形のシミュレーション結果 実測と同様の $\Delta V_{ce}$ を再現できた。

Switching waveform simulation data when turned off

図9.  $C_{ge'}$ の大きさと $V_{ge}$ ,  $I_c$ , 及び $\Delta V_{ce}$ の関係のシミュレーション結果  $C_{ge'}$ が大きいほど、 $\Delta V_{ce}$ の抑制効果が高い。

Dependence of gate-emitter voltage  $(V_{\rm ge})$ , collector current  $(I_{\rm c})$ , and collector-emitter voltage difference  $(\Delta V_{\rm ce})$  on additional gate-emitter capacitance  $(C_{\rm ge})$  obtained through simulations

図 10.  $C_{ge'}$ の接続位置による  $\Delta V_{ce}$  の違いのシミュレーション結果  $C_{ge'}$  を内部に接続するより外部に接続する方が,  $\Delta V_{ce}$  の抑制効果が高いことが分かった。

Relationship between  $\Delta V_{ce}$  and  $C_{ge'}$  obtained through simulations

図 11.  $C_{ge}$ と $R_g$ を変えた場合の $\Delta V_{ce}$ 増加率と $E_{off}$ 増加率の関係のシミュレーション結果

$\Delta V_{\rm ce}$ 増加率を抑えるためには、 $R_{\rm g}$ を大きくするより $C_{\rm ge}$ を大きくする方が $E_{\rm off}$ の増加が少ない。

Relationship between increase rates of  $\Delta V_{ce}$  and turn-off loss ( $E_{off}$ ) depending on  $C_{ge'}$  and gate resistance ( $R_g$ ) obtained through simulations

(**図11**)。  $\Delta V_{ce}$ に依存するターンオフ時の $I_c$ の傾きは,一般に $R_g$ で調整することが多いが,このグラフを見ると $C_{ge}$ で調整する方が $E_{off}$ の増加が少ないことが分かる。

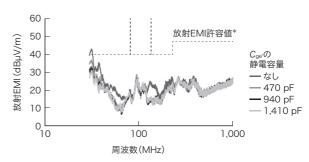

これらのシミュレーション結果を検証するために, 放射

\*J55011: 2015,「工業, 科学及び医療用装置からの妨害波の許容値及び 測定法」<sup>(1)</sup>による

#### 図12. Cge を変えたときの放射 EMIの測定結果

適切な $C_{ge}$ を接続することで、放射 EMI を許容値より低いレベルまで低減できた。

Results of radiated EMI noise measurements due to change in  $C_{\rm ge'}$

EMIを実際に測定したところ、適正な $C_{ge}$ の接続で、放射 EMIを抑制できることを確認した( $\mathbf{図12}$ )。

## 4. あとがき

パワーデバイスのスイッチングノイズを, 高度化した等価 回路デバイスモデルで予測するシミュレーション技術につい て述べ, シミュレーションで実際のデバイスの特性を予測 できることを示した。この技術の適用により, 設計段階でスイッチングノイズを抑制し、開発効率を向上できる。

今後も, 効率的かつ実用的なノイズ対策技術を研究し, パワーエレクトロニクス分野の技術発展に貢献していく。

#### 文 献

- (1) J55011: 2015.工業、科学及び医療用装置からの妨害波の許容値及び 測定法

- (2) Fujihira, T.; Miyasaka, Y. "Simulated superior performances of semiconductor super junction devices". Proc. of the 10th International Symposium on Power Semiconductor Devices and ICs (ISPSD '1998). Kyoto, 1998-06. 1998, p.423-426.

安住 壮紀 YASUZUMI Takenori, Ph.D. 総合研究所 生産技術センター 回路・制御技術研究部 博士(工学) 電子情報通信学会会員 Circuit and Control Technology Research Dept.

山下 浩明 YAMASHITA Hiroaki 東芝デバイス&ストレージ(株) 半導体事業部 パワー半導体開発技術部 Toshiba Electronic Devices & Storage Corp.

子迫 修司 KOSAKO Shuji 東芝デバイス&ストレージ(株) 半導体事業部 半導体応用技術センター Toshiba Electronic Devices & Storage Corp.